# LCD-Pro IP user manual

UM0011 (v1.0) - 14 July 2009

User Manual:

# **Overview**

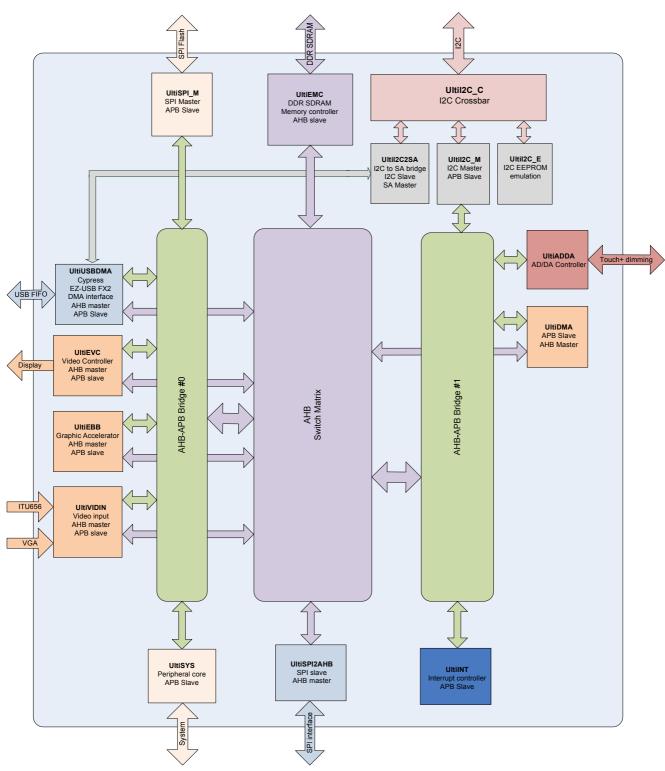

This document describes the LCD-Pro IP architecture, including the next cores: UltiEVC display controller, UltiEBB 2D graphic accelerator, UltiEMC DDR memory controller, UltiVidin video input core, UltiDMA DMA controller, UltiSPI2AHB SPI slave core and UltiSPI\_M SPI master core.

Full core interfaces and registers are described for user reference.

This document describes the LCD-Pro IP core for Full Version<sup>1</sup>.

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved. Technical data subject to change. All trademarks and trade names appearing in this document are property of their respective owners. Copyright © 2008-2009 Sitek SpA-Verona-Italy, All Rights Reserved.

Disclaimer Sitek SpA is providing this design, code, or information "as is." basis, without warranty of any kind, either expressed or implied, including, without limitation, warranties that the covered code is free of defects, merchantable, fit for a particular purpose or non-infringing. Each party bears the entire risk as to the quality and performance of the original code, upgraded code, and modifications, to the extent originating with and provided by such party. Should any covered code prove defective in any respect, you assume the cost of any resulting damages, necessary servicing, repair or correction. This disclaimer of warranty constitutes an essential part of this license. No use of any covered code is authorized hereunder except subject to this disclaimer.

UM0011 (v1.0) – 14 July 2009 User Manual www.exorint.net

<sup>&</sup>lt;sup>1</sup> Refer to LCD-Pro IP architecture datasheet (DS0031) for more information on other versions.

| 1 | INT        | RODUCTION     | V                                     | 4  |

|---|------------|---------------|---------------------------------------|----|

|   | 1.1        | FEATURES      |                                       | 4  |

| 2 | COF        | RE ARCHITE    | ECTURE                                | 5  |

|   | 2.1        | BLOCK SCI     | HEMATICS                              | 6  |

| 3 | Sys        | tem Intercon  | nect                                  | 7  |

|   | 3.1        |               |                                       |    |

|   | 3.2<br>3.3 |               | nge mapping                           |    |

| 4 |            |               | ents                                  |    |

|   | 4.1        | •             | ce                                    |    |

|   | 4.1.       |               | Bulk access                           |    |

|   | 4.4        | 0             | Oingle coope                          | 40 |

|   | 4.1.       | 2             | Single access                         | 13 |

|   | 4.1.       | 3             | Registers                             | 14 |

|   | 4.2        | SPI master    | interface                             | 15 |

|   | 4.2.       | 1             | Registers                             | 16 |

|   | 4.2.       | 2             | General description and operation     | 17 |

|   | 4.3        | EVC video     | controller                            | 19 |

|   | 4.3.       | 1             | General Description                   | 19 |

|   | 4.3.       | 2             | Core architecture                     | 20 |

|   | 4.3.       | 3             | Functional description                | 21 |

|   | 4.3.       | 4             | Layer image acquisition               | 21 |

|   | 4.3.       | 5             | Layer image definition                | 24 |

|   | 4.3.       | 6             | Multi –layer blending                 | 28 |

|   | 4.3.       | 7             | Pixel color conversion and scrambling | 32 |

|   | 4.3.       | 8             | Flat panel display control            | 32 |

|   | 4.3.       | 9             | Configuration and control             | 36 |

|   | 4.3.       | 10            | Configuration example                 | 44 |

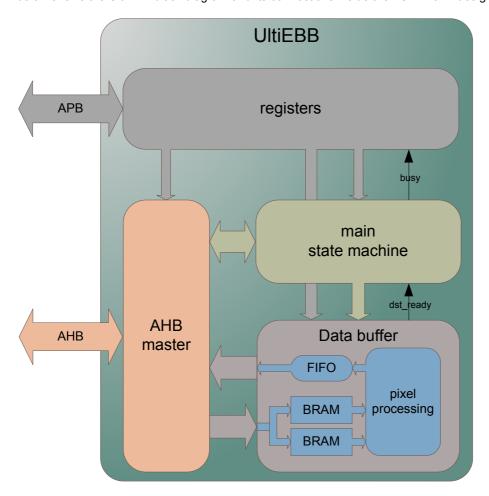

|   | 4.4        | BitBlit core: | UltiEBB                               | 46 |

|   | 4.4.       | 1             | Registers                             | 47 |

|   | 4.4.       | 2             | Operation                             | 55 |

|   | 4.4.       | 3             | Configuration examples                | 69 |

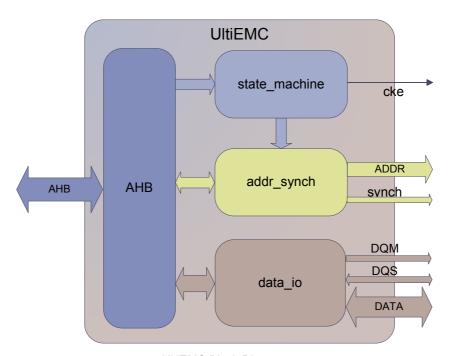

|   | 4.5        | DDR memo      | ry controller: UltiEMC                | 71 |

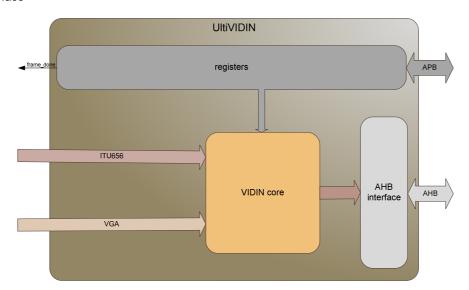

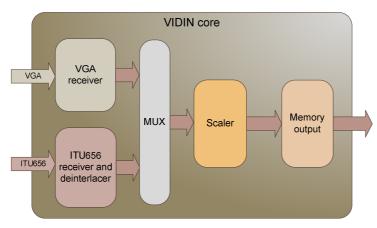

| 4.6 Video Ir     | nput core: UltiVIDIN           | 72  |

|------------------|--------------------------------|-----|

| 4.6.1            | Registers                      | 73  |

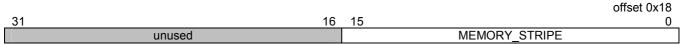

| 4.6.2            | UltiVIDIN operation            | 77  |

| 4.6.3            | Configuration example          | 78  |

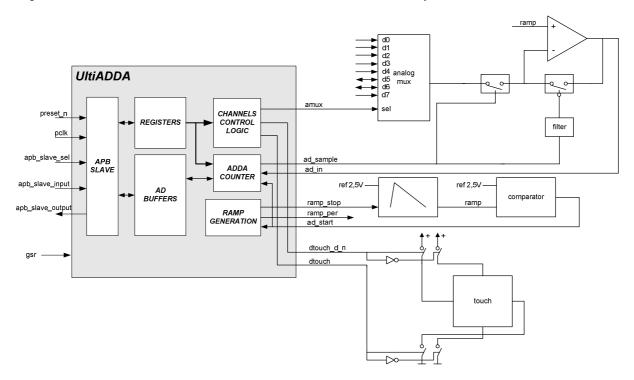

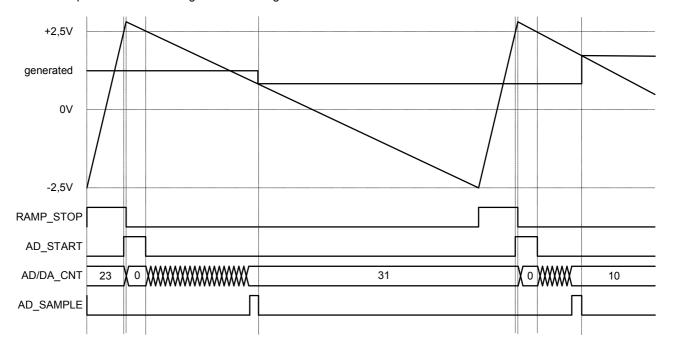

| 4.7 AD/DA        | controller: UltiADDA           | 79  |

| 4.7.1            | Functional description         | 80  |

| 4.7.2            | Memory and registers           | 82  |

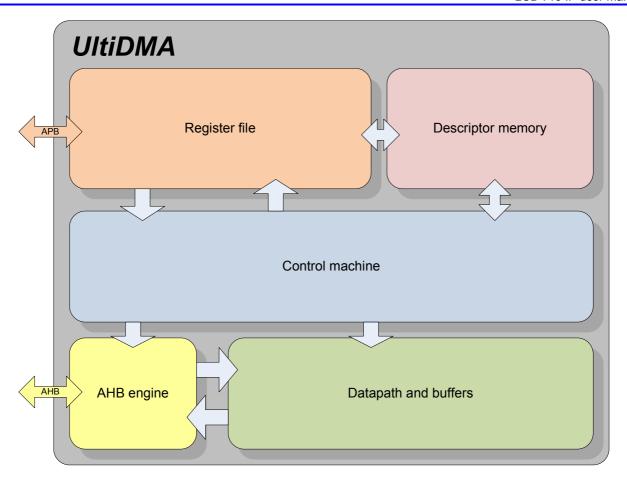

| 4.8 UltiDMA      | <b>\</b>                       | 83  |

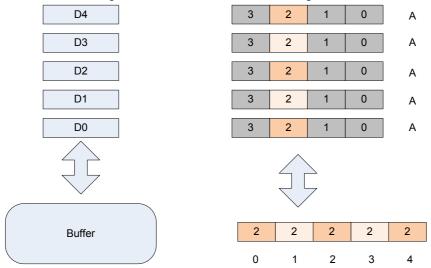

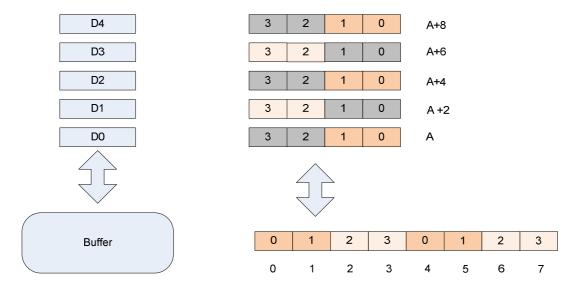

| 4.8.1            | Operation                      | 84  |

| 4.8.2            | Configuration and control      | 90  |

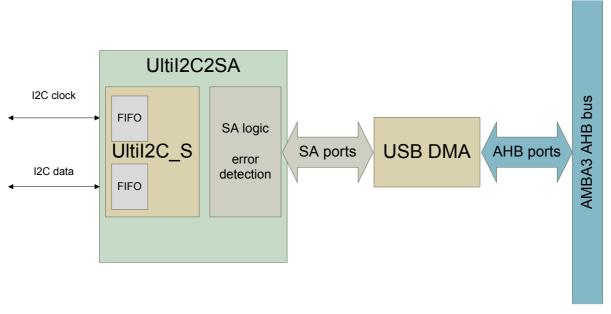

| 4.9 I2C arch     | nitecture and interface        | 95  |

| 4.9.1            | Ultil2C2SA core                | 96  |

| 4.9.2            | Ultil2C_M                      | 97  |

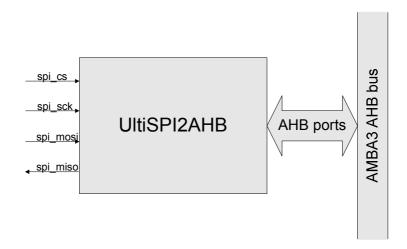

| UltiSPI2AHB core | e                              | 100 |

| 4.9.3            | Instruction set                | 101 |

| 4.9.4            | Operation                      | 102 |

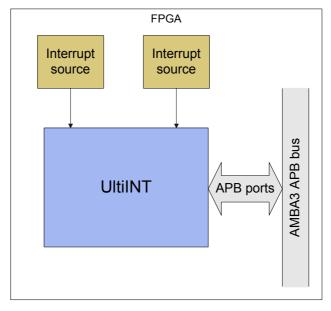

| 4.10 UltiINT     | Γ Interrupt controller         | 111 |

| 4.10.1           | Configuration and register map | 111 |

| 4.11 UltiSY      | S                              | 112 |

| 4.11.1           | Registers and use              | 112 |

# 1 INTRODUCTION

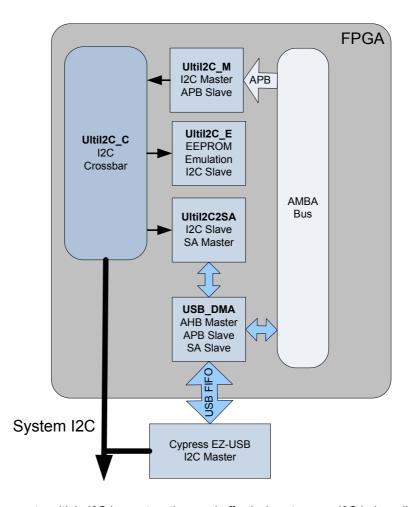

LCD-Pro IP is designed as multipurpose Video controller, targeted for TFT displays, based on Lattice ECP2-50 FPGA.

The module's functionality is implemented using an FPGA-based system-on-chip (Lattice ECP2-50 FPGA). The system-on-chip is based on the SoC interconnect, enabling simplified FPGA design integration and IP-block oriented design for the FPGA

One of the features of the LCD-Pro IP modules is the ability to operate as a standalone USB peripheral. LCD-Pro IP supports the 8051-based high speed USB peripheral controller, Cypress EZ-USB FX2 (CY7C68013A), used for interfacing the LCD-Pro IP module to a device with USB host functionality, such as PCs and USB-OTG compliant devices.

#### 1.1 FEATURES

- Supports Lattice ECP2 family

- Supports video controller module

- ° Supports touch controller module

- Supports backlight dimming control

- ° Supports memory controller module

- Supports USB controller module

- Supports Video input module

- Supports SPI master module

- ° System-on-chip architecture based

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 4/112

# **2 CORE ARCHITECTURE**

The LCD-Pro IP includes the next cores:

- UltiEVC

- 0 **UltiEBB**

- UltiVidin

- USB DMA

- UltiSPI M

- UltiEMC

- Ultil2C\_M Ultil2C\_C

- Ultil2C\_E

- Ultil2C2SA

- **UltiADDA**

- **UltiDMA**

- 0 **UltiINT**

- UltiSPI2AHB

- 0 **UltiSYS**

- SoC buses, switch matrix and bridges

UM0011 (v1.00) - 14 July 2009 www.exorint.net 5/112

# 2.1 BLOCK SCHEMATICS

LCD-Pro IP Block Diagram. Full version: Full version Video Controller + Video Input module

# 3 System Interconnect

The LCD-Pro IP is based on SoC interconnection, bus structure is organized in 2 layers:

- 1. AHB bus: high speed, multiplexed, pipelined bus

- 2. APB bus: low speed multiplexed bus, not pipelined, used primarily for peripheral access

#### 3.1 AHB bus

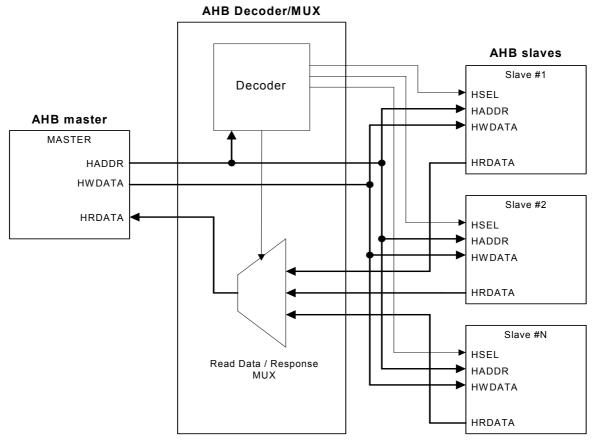

The AHB bus is the main system interconnect in LCD-Pro IP SoC, providing high-speed system interface for system bus masters. AHB is a multiplexed bus, where one AHB master can perform transaction to an only one AHB slave at the same time. AHB is also a pipelined bus, and the slave response to the master transaction is active at least one clock cycle after the master's request. The bus protocol is synchronous, and the pipelined operation enables high transfer speeds.

AHB slaves are connected to the master via a bus decoder/multiplexor which generates slave enable signals and muxes the slave response lines to the master. Additionally the decoder behaves as a default, idle slave.

AHB Bus decoding/multiplexing

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 7/112

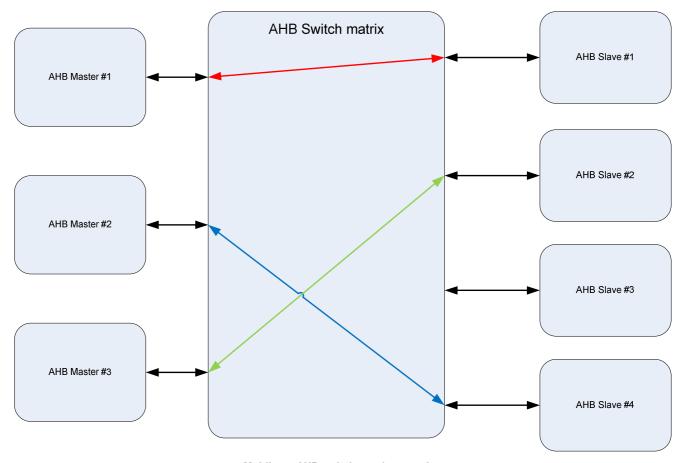

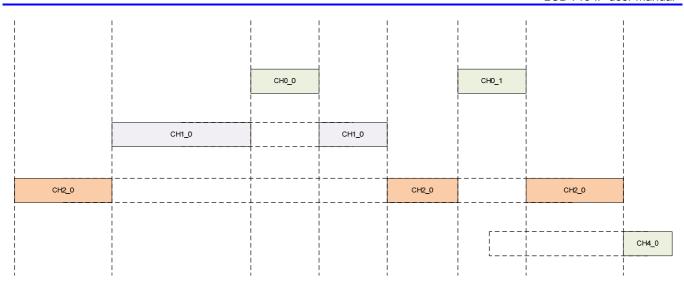

Multilayer AHB switch matrix operation

The AHB switch matrix appears as a slave to the AHB master which attempts the transaction. The switch matrix accepts the transaction, delaying the transfer with the HREADY line until the slave access becomes available.

A master also has the capability to lock a bus for its use in consecutive transfers.

Simultaneous bus transactions through the AHB switch matrix raise effective bus bandwidth, and reduce access latencies. For example, a video controller could fetch image data at a constant rate from the video memory concurrently to a DMA I/O transfer from the system memory to the Ethernet controller.

In LCD-Pro IP, the AHB bus has a 32 bit data bus clocked at 96 MHz. The AHB address bus is 32 bits wide, which can be used to address 4.294.967.296 bytes (4 GB)

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 8/112

#### 3.2 APB bus

APB bus is the peripheral bus, designed for simpler or slower devices, primarily peripherals. It is a non-pipelined multiplexed synchronous bus which allows a single master to drive multiple slaves. The protocol does not support burst transfers, and does not support transfer sizes less than the bus width. The minimum addressable chunk of address space on the APB bus is the bus width.

APB is envisioned as the hierarchical extension of the AHB bus. The APB bus master is, effectively, an AHB-to-APB bus bridge. The AHB-APB bus bridge behaves as an AHB slave, which converts the AHB transfers to the APB transfers. The address space of the APB bus is mapped in the address space of the AHB bus.

On LCD-Pro IP, the APB bus has a 32-bit address and data bus size. Only part of this address range is decoded for slave selection, so user has to take care not to access non-existing addresses, which will wrap to unknown APB slave. The APB bus is clocked on 48 MHz. The APB bridge resamples the transfer internally between the faster AHB clock domain and the slower APB clock domain. Running the APB logic on a slower clock enables better timing optimization in the logic design, as it decouples the slow peripheral access bus from the fast system bus.

The APB decoder is connected to a dedicated AHB layer on the AHB interconnection matrix, which prevents the AHB bus operation being interrupted by slow APB transfers from a high priority master.

# 3.3 Address range mapping

The only true AHB slave in the system is the UltiEMC DDR memory controller. As the source of the image refresh, it requires the burst capability and high bandwidth offered by the AHB.

Additionally, two distinct AHB-to-APB interface bridges are present, each of them mapped to a different address range. The control interfaces of the IP in the system are mapped to the APB buses.

The LCD-Pro IP AHB interconnection matrix maps the AHB address space into ranges:

| 0x00000000  |                        |

|-------------|------------------------|

|             | DDR SDRAM memory range |

| 0x7FFFFFFF  | , ,                    |

|             |                        |

| 0x800000000 |                        |

|             | 48 MHz APB #0          |

|             | 40 IVII IZ AFD #0      |

| 0xBFFFFFFF  |                        |

| 00000000    |                        |

| 0xC0000000  |                        |

|             | 48 MHz APB #1          |

| 0xffffffff  |                        |

| OXECCECE    |                        |

The APB address spaces are further divided. Several cores are mapped to the 48 MHz APB.

|            | APB #0    |

|------------|-----------|

| 0x80000000 |           |

| 0xA0000FFF | UltiEVC   |

|            |           |

| 0xA0001000 | LUEEDD    |

|            | UltiEBB   |

| 0xA0001FFF |           |

| 0xA0002000 |           |

|            | UltiSPI_M |

| 0xA0002FFF |           |

| 0xA0003000 |           |

|            | UltiSYS   |

| 0xA0003FFF |           |

| 0xA0004000 |           |

|            | USB DMA   |

| 0xA0004FFF | _         |

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 9/112

| 0xA0005000<br>0xA0007FFF | UltiVidin |  |  |  |  |

|--------------------------|-----------|--|--|--|--|

|                          |           |  |  |  |  |

|                          | APB #1    |  |  |  |  |

| 0xC0000000               |           |  |  |  |  |

|                          | UltiADDA  |  |  |  |  |

| 0xC0001FFF               |           |  |  |  |  |

| 0xC0002000               |           |  |  |  |  |

|                          | Ultil2C_M |  |  |  |  |

| 0xC0002FFF               | _         |  |  |  |  |

| 0xC0003000               |           |  |  |  |  |

|                          | Ulti_INT  |  |  |  |  |

| 0xC0004FFF               | _         |  |  |  |  |

| 0xC0005000               |           |  |  |  |  |

|                          | UltiDMA   |  |  |  |  |

| 0xC000FFFF               |           |  |  |  |  |

Note: The apparently large address range of the UltiEVC is due to the functionality of the AHB-APB bridge. For the APB slave with the highest base address, the bridge will map the entire remainder of the address space. Identical decoding principle is used also by the AHB switch matrix, hence the large address space assigned to the APB.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 10/112

# 4 System Components

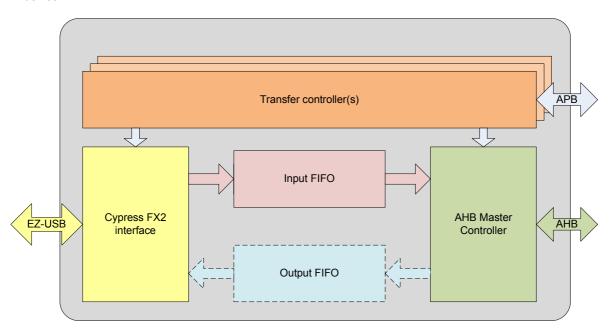

### 4.1 USB Interface

The Cypress USB DMA is a programmable data pump used to transfer data from the USB endpoints of the external Cypress EZ-USB FX2 chip to the LCD-Pro IP video memory. The primary function is to transfer image data. With its quantum fifo interface, the Cypress can support high speed USB data streaming to the device over bulk or isochronous USB endpoints. Additionally, it supports issue of single access operations on the AHB bus.

The USB DMA uses a modular internal architecture which enables the hardware to be easily configured for the target application, based on the number of the data endpoints and their direction. In LCD-Pro IP, the USB DMA is currently configured to work as a single endpoint, downstream data pipe, enabling transfer of data from the USB host to the LCD-Pro IP device.

For configuration, the DMA interface also behaves as an APB slave, enabling the configuration of the USB DMA.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 11/112

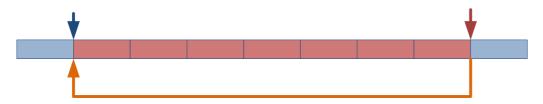

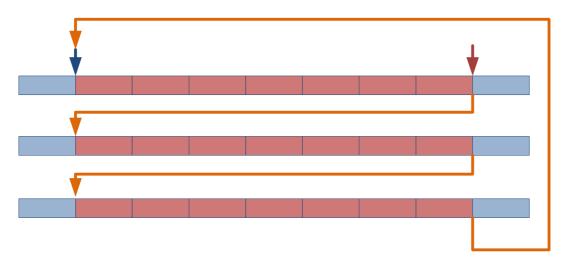

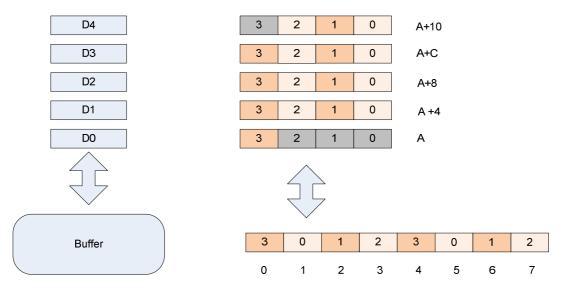

#### 4.1.1 Bulk access

Bulk access operation enables the transfer of a data stream from the USB endpoint to the LCD-Pro IP device memory (the streaming from the memory to the USB endpoint is not currently implemented, but is possible).

The USB DMA supports several bulk access operating modes, enabling operation from simple data transfers to image transfers, which require image dimension information for correct alignment. The USB DMA supports several operating modes.

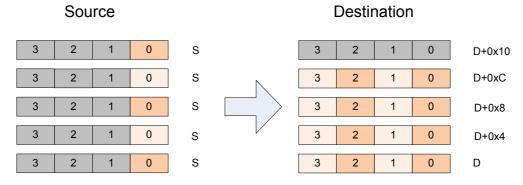

Linear: the data is written to the AHB bus incrementally from a defined base address.

- Circular: the data is written to the AHB bus incrementally from a defined base address for a specific data count, after which it returns back to the starting address.

- Stride: used for image transfer. The data is written to the AHB bus incrementally from a starting address for a specified number of data elements. After that the new starting address is defined as old starting address incremented by the stride length. After a specific data count has been reached, the new starting address to the original base address.

The USB DMA bulk interface transfers data in 16-word bursts, which is the maximum specified burst size on the AHB bus. Data sizes less than a word (32 bits) are not supported. The destination addresses and counts need to be defined in quantums of the burst size. These limitations reflect the nature of the interface, which supports high speed operation of the interface while keeping the logic simple.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 12/112

# 4.1.2 Single access

The single access mode enables random access to the bus address space. It supports single read and write accesses of all sizes. The single access mode utilizes two USB endpoints for a request-response protocol. The requests are sent over one endpoint, while over the second endpoint the responses are received by the USB host.

Over each endpoint a stream of messages is transferred.

### 4.1.2.1 Request message

A request message is 16 bytes in size.

| 0x0 |  |

|-----|--|

| 0x4 |  |

| 8x0 |  |

| 0xC |  |

| 0       | 1            | 2       | 3  |  |  |

|---------|--------------|---------|----|--|--|

| Tag     | Command/Size | A0      | A1 |  |  |

| A2      | A3           | D0      | D1 |  |  |

| D2      | D3           | padding |    |  |  |

| padding |              |         |    |  |  |

Α

request message consists of:

- Tag the identifier of the operation in the stream, used to identify the corresponding response message in the response stream. The tag of the request will be copied to the response.

- Command/size the identifier used to define the bus operation.

- A[3:0] the bus address in little endian ordering (A0 = LSB byte, A3 = MSB byte)

- D[3:0] the bus data (for write operations) in little endian ordering (D0 = LSB byte, D3 = MSB byte). Dummy data/padding for read operations.

- Padding dummy data to align on 16 byte boundary (to pack messages into a single USB frame and for future use).

The command/size identifier:

| 7      | 6 | 5  | 4  | 3 | 2      | 1      | 0      |

|--------|---|----|----|---|--------|--------|--------|

| HWRITE |   | RF | =U |   | HSIZE2 | HSIZE1 | HSIZE0 |

The HWRITE line is mapped to the HWRITE flag on the AHB bus.

- 1 AMBA write

- 0 AMBA read

The HSIZE[2:0] identifier is mapped to the HSIZE bus on the AHB bus.

- 000 = Byte

- 001 = Halfword (16 bits)

- 010 = Word (32 bits)

Bits 6:3 are RFU and should be set to 0.

# 4.1.2.2 Response message

A response message is 8 bytes in size.

A response message consists of:

- Tag the identifier of the operation in the stream, used to match the response message in the response stream to its corresponding request message The tag of the request is copied to the response.

- D[3:0] the bus data (for read operations) in little endian ordering (D0 = LSB byte, D3 = MSB byte). Dummy data/padding for write operations.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 13/112

Padding – dummy data to align on 8 byte boundary (to pack messages into a single USB frame and for future use).

# 4.1.3 Registers

The USB DMA has several APB-mapped registers used to control the DMA transfer.

| Offset | Name   | Description                          |  |

|--------|--------|--------------------------------------|--|

| 0x0    | MODE   | Operating mode for bulk transfer     |  |

| 0x4    | ADDR   | Address for bulk transfer            |  |

| 0x8    | CNT    | Data count for bulk transfer         |  |

| 0xC    | STRIDE | Stride for bulk transfer stride mode |  |

| 0x10   | LINE   | Line for bulk transfer line mode     |  |

| 0x14   | RESET  | Reset for the entire USB DMA         |  |

| 0x18   | PE CNT | PKTEND timeout counter               |  |

The MODE register is used to control the USB DMA bulk operating mode.

| 31     | 3 | 2  | 1  | 0      |

|--------|---|----|----|--------|

| unused |   | MO | DE | ENABLE |

The MODE parameter denotes the operating mode.

- 00 Linear mode

- 01 Circular mode

- 10 Stride mode

The ENABLE bit serves as the mode initiator/local reset. The USB DMA needs to be disabled (ENABLE = 0) before the parameters (mode, address, stride, line, count) can be modified. Once the ENABLE bit is set from 0 to 1, the parameters from the registers are initialized and transfer can begin.

The ADDR register contains the address of the bulk transfer. The address must be aligned to the bus burst boundary.

| 31   | 6 | 5 | 0 |

|------|---|---|---|

| ADDR |   | 0 |   |

The bits 5:0 of the address counter MUST be always set to 0.

The CNT register holds the data count for the transfer. Which is the size of the circular buffer in the Circular transfer mode, and the size of the image for transfer in the Stride mode.

The STRIDE register holds the stride size for the Stride transfer mode. Not used otherwise.

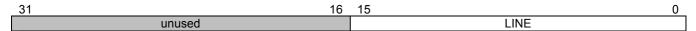

The LINE register holds the size of the image line for the Stride transfer mode. Not used otherwise.

The RESET register contains the reset bit. This bit resets the entire USB DMA while set to 1.

1 0

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 14/112

unused RESET

The initial state of the reset bit is set to '1' which keeps the DMA machine in total reset. This is to prevent the transient occurring during the system power-up and Cypress SDRAM, and to prevent contention on external lines until the Cypress FX2 boot up process is completed.

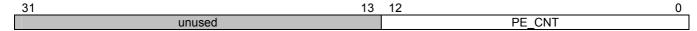

The PE CNT register holds the timeout counter for the PKTEND commit line of the Cypress FX2.

This is used with single access mode to enable the commit of the last packet in the Cypress FX2 FIFO to the USB domain even if the packet is not completely full (required for the FX2 to auto-commit the packet to the USB domain). The timeout counter is reset to PE\_CNT on each byte transferred to FX2. When the timeout reaches 0 (no response has been issued for a given period of time indicating that the transfer gueue is completed), the PKTEND is issued and the packet is committed.

This register is initialized by the FX2 firmware and should not be modified!

#### 4.2 SPI master interface

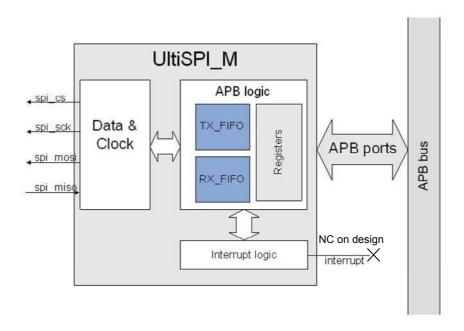

SPI master interface is implemented using the UltiSPI\_M core, based on FIFO interface for data and registers for configuration.

SPI interface consists of two FIFOs for data flow, registers for configuration and interrupt logic (the interrupt output line is not connected on LCD-Pro IP design). SPI interface consists of chip select output, clock output, serial data output and serial data input. Both transmit and receive FIFO are 2048 bytes deep.

Internal structure of SPI master interface

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 15/112

# 4.2.1 Registers

| Register     | Width (bits) | Read/Write           | Address offset |

|--------------|--------------|----------------------|----------------|

| FIFO         | 8            | R/W                  | 0x00           |

| TX_STATUS    | 16           | R                    | 0x10           |

| RX_STATUS    | 16           | R                    | 0x20           |

| CLK_DIV      | 5            | R/W                  | 0x30           |

| SPI_CONFIG   | 9            | R/W                  | 0x40           |

| TRN_BYTE_NUM | 12           | R/W                  | 0x50           |

| FRAME_SIZE   | 12           | R/W                  | 0x60           |

| TIMEOUT      | 16           | R/W                  | 0x70           |

| DESEL_TIME   | 8            | R/W                  | 0x80           |

| STATUS       | 3            | R/W*                 | 0x90           |

| INT_MASK     | 4            | R/W                  | 0xA0           |

| INTERRUPT    | 4            | R/Clear on write '1' | 0xB0           |

# SPI\_master registers

write access to the STATUS register is used for start (write "001") or reset (write "1XX").

The FIFO register is organized as follows

| Register bit(s) | Description                         |

|-----------------|-------------------------------------|

| FIFO            | Write to TX_FIFO, read from RX_FIFO |

The TX\_STATUS is organized as follows

| Register bit(s) | Description                |

|-----------------|----------------------------|

| TX_STATUS[11:0] | Number of bytes in TX_FIFO |

| TX_STATUS[14]   | TX_FIFO empty flag         |

| TX_STATUS[15]   | TX_FIFO full flag          |

The RX\_STATUS is organized as follows

| Register bit(s) | Description                |

|-----------------|----------------------------|

| RX_STATUS[11:0] | Number of bytes in RX_FIFO |

| RX_STATUS[14]   | RX_FIFO empty flag         |

| RX_STATUS[15]   | RX_FIFO full flag          |

The SPI\_CONFIG register is organized as follows

| Register bit(s)  | Description                                              |

|------------------|----------------------------------------------------------|

| SPI_CONFIG[0]    | CPOL mode                                                |

| SPI_CONFIG[1]    | CPHA mode                                                |

| SPI_CONFIG[3:2]  | RFU                                                      |

| SPI_CONFIG[7: 4] | Reserved: must be all 0s                                 |

| SPI_CONFIG[8]    | CS active polarity. If CS(0) is active low, write '0' to |

|                  | SPI_CONFIG[8].                                           |

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 16/112

#### The STATUS register is organized as follows

| Register bit(s) | Description                                             |  |  |

|-----------------|---------------------------------------------------------|--|--|

| STATUS[0]       | Write – ('1') start operation                           |  |  |

|                 | Read - UltiSPI_M busy ('1') or idle ('0')               |  |  |

| STATUS[1]       | Read only.  ('1') TX_FIFO underrun occurred during last |  |  |

|                 | operation. This bit is cleared on beginning of          |  |  |

|                 | each new operation.                                     |  |  |

|                 | ('0') no underrun occurred.                             |  |  |

| STATUS[2]       | Write – ('1') reset UltiSPI_M                           |  |  |

|                 | Read - ('1') RX_FIFO overrun occurred during            |  |  |

|                 | last operation. This bit is cleared on beginning of     |  |  |

|                 | each new operation.                                     |  |  |

|                 | ('0') no overrun occurred                               |  |  |

#### The INT MASK register is organized as follows

| Register bit(s) | Description                             |

|-----------------|-----------------------------------------|

| INT_MASK[0]     | Mask ('1') or unmask ('0') INTERRUPT[0] |

| INT_MASK[1]     | Mask ('1') or unmask ('0') INTERRUPT[1] |

| INT_MASK[2]     | Mask ('1') or unmask ('0') INTERRUPT[2] |

| INT MASK[3]     | Mask ('1') or unmask ('0') INTERRUPT[3] |

#### The INTERRUPT register is organized as follows

| Register bit(s) | Description                                                                     |  |  |

|-----------------|---------------------------------------------------------------------------------|--|--|

| INTERRUPT[0]    | Interrupt on UltiSPI_M idle. Reset by writing '1'.                              |  |  |

| INTERRUPT[1]    | Interrupt on error, TX_FIFO underrun, or RX_FIFO overrun. Reset by writing '1'. |  |  |

| INTERRUPT[2]    | Interrupt on TX_FIFO empty. Reset by writing '1'.                               |  |  |

| INTERRUPT[3]    | Interrupt on RX_FIFO not empty. Reset by writing '1'.                           |  |  |

### 4.2.2 General description and operation

All time periods are calculated in the number of the clock cycles, so the configuration parameters need to be calculated in relation to the 48Mhz AMBA APB interface clock frequency. All relevant registers need to be set prior to the starting of the operation and TX\_FIFO needs to be filled with at least one byte.

All frequencies obtainable by dividing the 48Mhz frequency with an even number up to 16 are possible. Highest frequency is equal to the half of the system frequency, set when writing 0 or 2 to the divider register. Desired frequency is set by the register CLK DIV. After reset, UltiSPI M is set to the highest frequency.

The SPI mode of operation and the polarity of chip select are configured by the register SPI\_CONFIG. This register sets CPOL, CPHA and active state of the chip select output. After reset all these bits are set to '0', setting the idle clock low, data sampling on the rising edge and the chip select active low.

The number of bytes to be transmitted on the write operation is set by the register TRN\_BYTE\_NUM. Present maximum size is 4096 bytes. Data is written in format N-1, so to send 2 bytes this register should be set to 0x001.

The total length of the SPI frame is set by the register FRAME\_SIZE. Present maximum size is 4096 bytes. The size of frame can be set to any value, which if larger than the value in TRN\_BYTE\_NUM means that, after sending bytes, frame will be extended to the size specified, with data being inputted to RX\_FIFO.

If TX\_FIFO does not contain enough data to complete the write operation, or RX\_FIFO is full during read operation, UltiSPI\_M will go to stall mode, stopping clock for a number of system clock cycles defined in the TIMEOUT register. If operation still cannot be completed after this period expires, system will report error in register STATUS and set chip select output to the inactive state. Maximum value for this interval is 0xFFFF. After reset, this register is set to 0x0000.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 17/112

SPI devices set minimum intervals between two operations, which is the minimum time for chip select set to the inactive state. This interval can be set by the register DESEL\_TIME; it will always be executed after operation is completed. During this interval, UltiSPI\_M will report busy state and not allow new operations. Maximum value is 0xFF, after reset this register is set to 0x00.

An operation or core reset is started by a write access to the register status, with the following options:

- Write 0x1 starts the operation, if TX\_FIFO is not empty. Otherwise, write access is ignored.

- Write 0x4 resets UltiSPI M, emptying FIFOs and resetting all registers to the reset value.

Status of the device and the result of the previous operation (whether error occurred or not) can be read from the register STATUS. Bits have the following meaning:

- STATUS[0] = '1' (busy), '0' (idle)

- STATUS[1] = '1' (TX FIFO underrun, not enough data to transmit, TIMEOUT period expired),

'0' (transmit OK)

- STATUS[2] = '1' (RX FIFO overrun, not enough space to receive, TIMEOUT period expired),

'0' (receive OK)

Status of the transmit FIFO can be read from the register TX\_STATUS, with 12 LSB bits showing the number of bytes in the FIFO and TX\_STATUS [14] being equal to the empty flag, and TX\_STATUS[15] to the full flag.

Status of the receive FIFO can be read from the register RX\_STATUS, with 12 LSB bits showing number of bytes in the FIFO and RX\_STATUS [14] being equal to the empty flag, and RX\_STATUS[15] to the full flag.

FIFO data access is done over the same address on APB, accessing TX\_FIFO on writes and RX\_FIFO on reads. When writing, it is not possible to overrun FIFO, starting the fill process again. When reading from an empty FIFO, FIFO will output last valid data and remain in the empty state. Both data write and read are mapped to the same APB address, but all writes are forwarded to the transmission FIFO, and reads are only from the receiver FIFO. To empty transmission FIFO, UltiSPI\_M has to be reset. Data access is 8-bit, while registers are various sizes, with the biggest being 32 bits.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 18/112

#### 4.3 EVC video controller

The EVC video controller interface is implemented using the UltiEVC core.

UltiEVC is a high performance modular embedded graphic display controller, targeted for driving active matrix flat panel displays. UltiEVC supports multi-layer overlay between multiple frame buffers with color-key transparency and alpha blending.

AMBA AHB interface is used as video memory interface and AMBA APB interface is used as register interface.

### 4.3.1 General Description

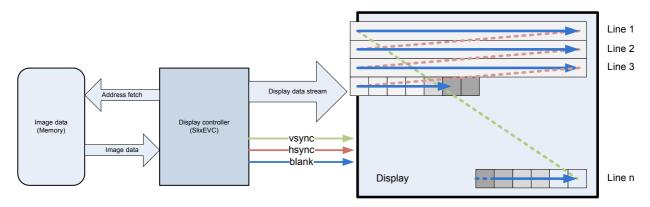

A display controller's function is to continuously refresh the image present on a graphic display device. The sequence of displayed images can be described as a continuous video stream, which can be either sourced externally or generated by scanning the image data present in a memory device. The UltiEVC generates the image stream by reading a memory area in the display memory, the frame buffer. The UltiEVC is capable of reading multiple frame buffer areas into different layers, and blending them into a single image, enabling complex graphics effects within the display controller.

The refresh operation is accompanied by generating the display control signals for horizontal and vertical synchronization (hsync and vsync) and data enable (blank). These signals define the refresh cycle and refresh rate of the display and are usually specific for a display panel. Timings for control signals are software configurable. The following characteristics are given for the LCD-Pro IP configuration:

- Active matrix display refresh

- Display resolution:

- o up to 1366x768 (2 16-bit layers, no video input) (1)

- up to 800x480 (4 layers) (1)

- 16 bit data output

- Display power-up sequence control

- Internal pixel clock generator

- ARM AMBA 3 compliant system interconnection

- AHB memory interface

- o APB register interface

- RGB8, RGB16,RGB32, ARGB32 frame buffer formats

- Multi-layer window and overlay image assembly (n° 4 layers available (2) )

- Variable frame buffer geometry stripe setting per layer

- Common overlay with color-key transparency

- · Alpha blending with per-layer fading

- Alpha mask layer support

NOTE <sup>(1)</sup>: The max display resolution depends on many factors, such as the number of layers effectively used for blending, the display refresh rate and the contemporary use of video input features. It is suggested to contact Exor International for any request regarding the specific application.

NOTE (2): The max number of layers which can be effectively used depends on many factors, such as the display resolution and refresh rate and the contemporary use of video input features. It is suggested to contact Exor International for any request regarding the specific application.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 19/112

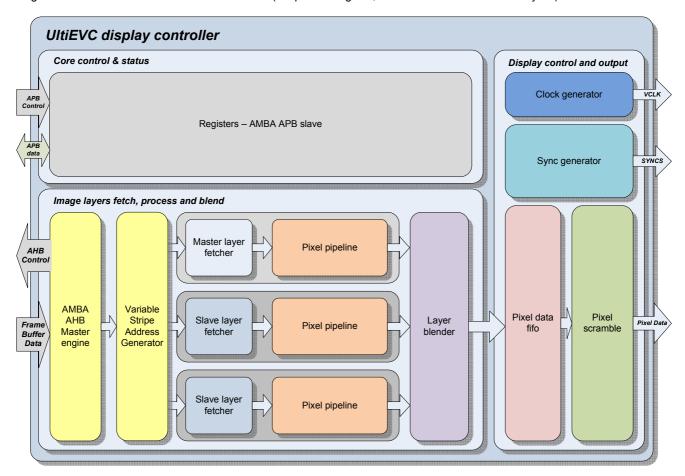

#### 4.3.2 Core architecture

The UltiEVC core consists of:

- ° Register APB slave

- ° Address generator

- AHB master

- ° Master and slave (overlay) layer fetchers

- ° Pixel pipelines

- ° Layers blending module

- ° Clock generator module

- Syncs generator module

- Pixel data fifo

- ° Pixel scramble module

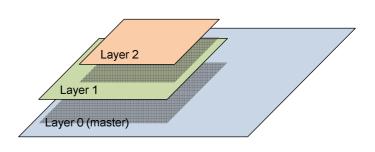

Diagram below shows UltiEVC core architecture (simplified diagram; the real core contains n° 4 layers)

**UltiEVC Block Diagram**

# 4.3.3 Functional description

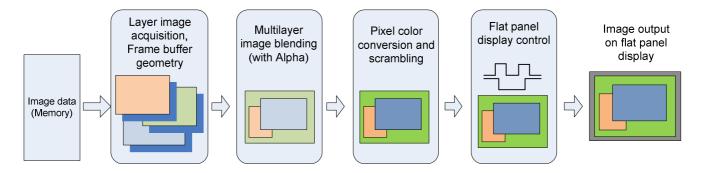

The operation of the UltiEVC can be divided into:

- Layer image acquisition with frame buffer geometry handling

- Multi-layer image blending (with Alpha channel)

- Pixel color conversion and scrambling

- Flat panel display control

**EVC** operation in phases

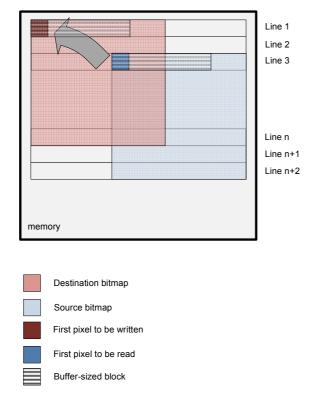

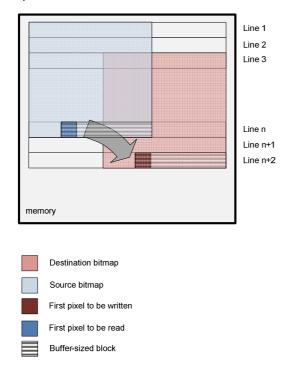

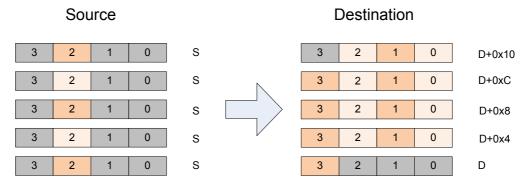

# 4.3.4 Layer image acquisition

The source images for the UltiEVC are stored in the display video memory. UltiEVC behaves as an AHB master and accesses the video memory through the on-chip AMBA AHB bus. Each image is stored in its own respective memory area (a frame buffer).

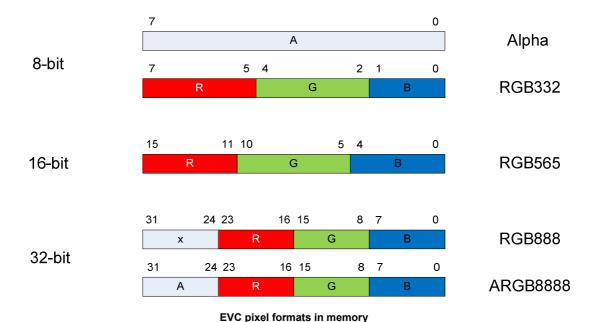

The image in memory is stored as RGB pixel data in 8, 16 or 32-bit format with or without Alpha information.

All formats are RGB. 8-bit format can be used either as 8-bit alpha channel information (for alpha mask) or as 8-bit RGB with 3 bits for red channel, 3 bits for green channel and 2 bits for blue channel (RGB 332).

16-bit format allows for RGB565, with 5 bits for red, 6 for green and 5 for blue.

32-bit format allows for RGB888, with 8 bits for each channel, and the upper 8 bits of a 32 bit word stand unused, or for ARGB8888, with 3-byte packing of pixels and alpha channel in the MSB byte.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 21/112

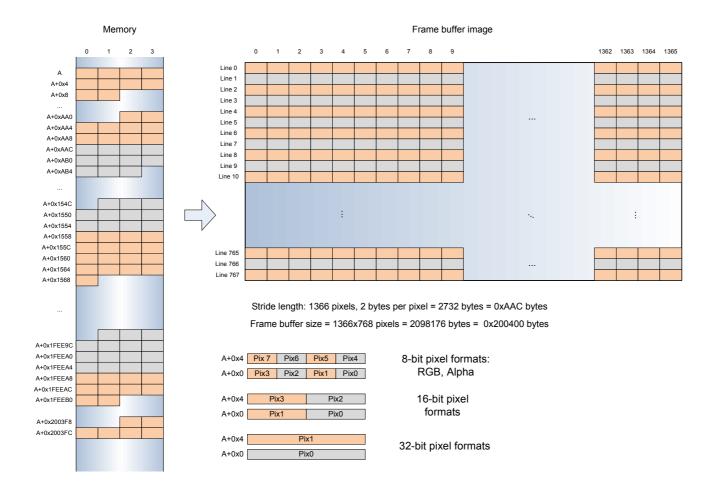

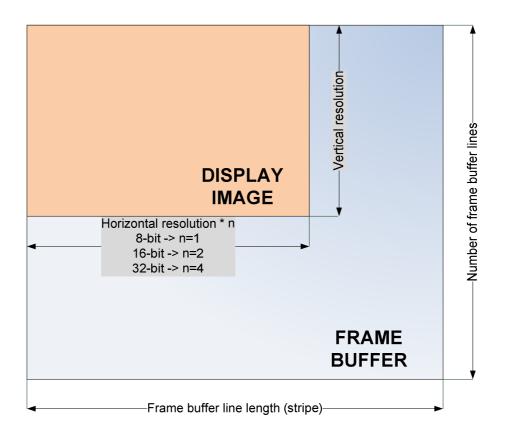

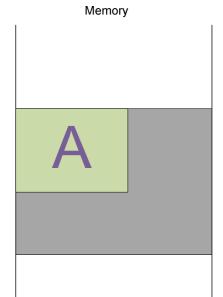

Each frame buffer is a rectangular memory area consisting of multiple lines. The size of a frame buffer is limited by the size of the system memory. The width of a frame buffer line in the memory is called the stripe, or stride. The stripe is also the distance in memory between two vertically adjacent pixels. EVC supports variable stripe length for each frame buffer, and is able to support any frame buffer geometry, which allows for more efficient memory usage.

The stripe used for a frame buffer is defined in bytes. Depending on the color depth used, the pixel geometry of the frame buffer, and the maximum achievable resolution is changed accordingly. For a defined frame buffer, the maximum horizontal resolution is equal to the stripe divided by the number of bytes occupied by a single pixel. The pixels of an individual line are ordered in ascending order in memory.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 22/112

#### Frame buffer geometry and memory organization

For the memory organization in **Error! Reference source not found.**, the EVC allows the maximum image of 1366x768 pixels with 16-bit color. If the color depth is changed to 32 bits, the maximum image resolution is decreased to 683 pixels.

The maximum vertical resolution is constrained only by the size of the allocated memory space. EVC has no limitation in the number of lines for a given frame buffer (other than the address bus width) and will successively increment the image address with the stripe count during the image fetch.

The address of a pixel within the frame buffer can be defined by the equation:

```

Pix address = y*STRIPE + x*BPP;

```

### Where:

- STRIPE is the length of the frame buffer line (the stripe) in bytes

- x, and y are the horizontal and vertical coordinates, respectively

- BPP is the number of bytes occupied by each pixel

The frame buffer organization is rectangular. For a given stride, each line of the image will be put in the corresponding line of the frame buffer, regardless of the horizontal resolution of the actual image. The remaining part of the frame buffer line will not be used.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 23/112

Image within a frame buffer

For more efficient memory usage, each image can be allocated a frame buffer exactly the size of the image.

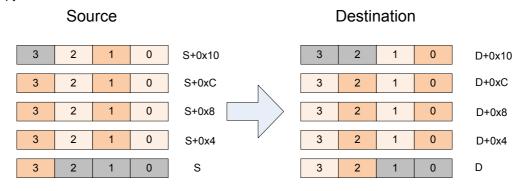

# 4.3.5 Layer image definition

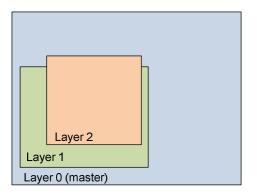

The image which is output to the display can be composed from multiple overlay image layers. Each overlay layer is fetched from its defined memory region (which acts as a separate frame buffer).

The overlay layers are divided into the master layer, which is always present, and a variable number of slave layers. Slave layers are overlayed over the master layer, with each subsequent slave layer being overlayed over the previous one. The master layer can be deactivated, but in that case the contents of the layer fetched from memory is replaced by a rectangle of a chosen color.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 24/112

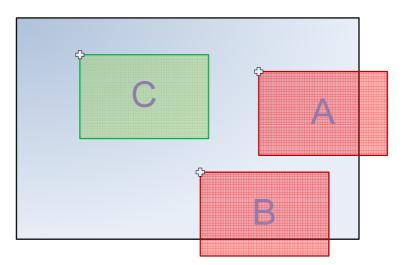

For each layer a visible overlay rectangle can be defined. The visible rectangle can be less or equal in size to the master layer (the screen resolution), and can be placed anywhere within the master layer visible rectangle as long as its boundaries are within the visible area of the master layer. Only the data in the bounding rectangle will be fetched from the frame buffer memory.

The layer rectangles can be simply overlayed, or blended together using alpha blending. When the layers are simply overlayed, each pixel within the visible rectangle of an overlay layer masks the pixels in the visible layers below. When the layers are alpha-blended, the layer image is used in alpha-compositing operation.

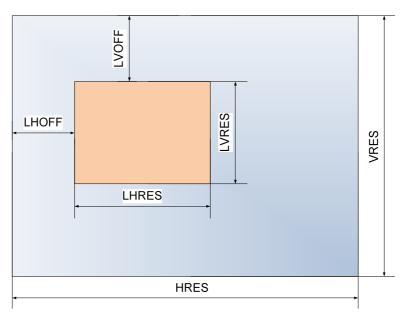

A visible rectangle is defined by 4 parameters:

- rectangle size: LHRES and LVRES

- · rectangle offset: LHOFF and LVOFF

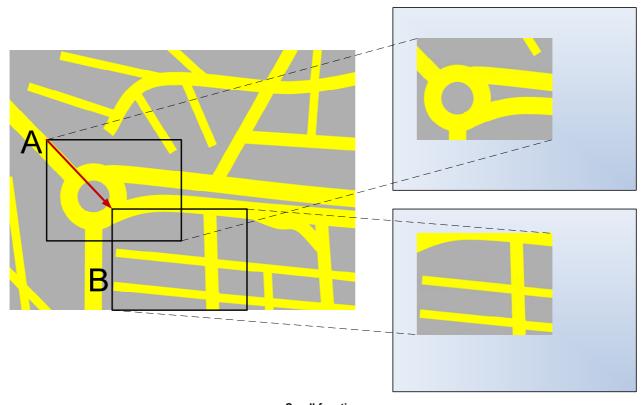

Overlay image geometry

Note: the Master layer is bound to the flat panel display size, and the layer parameters are undefined for the master layer.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 25/112

# 4.3.5.1 Layer smooth positioning

The image within the rectangle is always fetched from the base address in memory defined by the LBADDR register. Modifying the LHOFF and LVOFF will move the image across the visible screen.

This functionality is fundamental for achieving hardware cursor operation. A layer can be set to display a cursor image, and be fluidly moven around by setting LHOFF and LVOFF.

The image resides within a frame buffer area in the memory. The layer base address (LBADDR) register of the overlay layer is set to point to the beginning pixel of the image.

## Output image

The layer rectangle can be moved around the screen by LHOFF and LVOFF, but it will constantly refresh from the same address in the memory.

LHOFF and LVOFF are defined in pixels or lines, and can be set to any value within the visible area of the screen.

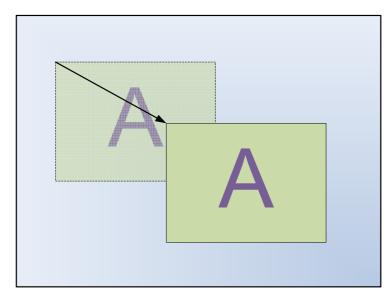

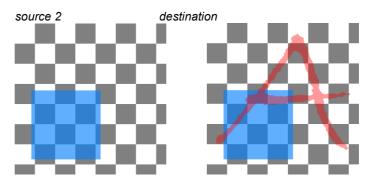

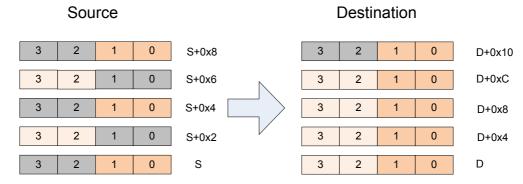

## 4.3.5.2 Smooth Scrolling

The image fetched to fill the overlay rectangle is defined by a rectangular area within a frame buffer with equal size in pixels (geometry within the frame buffer is defined by the layer color depth). The base address of the layer is the address of the upper left pixel in the layer rectangle within the frame buffer.

The starting point of the image can be changed by changing the base address of the layer. If the image contained in the overlay frame buffer is larger than the visible rectangle part, by changing the base address scrolling of the image in the frame buffer can be performed.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 26/112

Scroll function

In **Error! Reference source not found.**, the overlay rectangle does not change the screen position, but the base address is changed from the base coordinates of rectangle A to the base coordinates of rectangle B, resulting in a "scroll" effect of the map image.

In case the position and the size of the rectangle within the frame buffer causes the rectangle to exceed the frame buffer boundaries, the image will be corrupted. The visible window within the frame buffer must not cross the frame buffer boundaries.

Proper positioning of a layer visible rectangle within a frame buffer

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 27/112

In **Error! Reference source not found.**, only the rectangle "C" is properly positioned. The rectangles "A" and "B" are not, due to crossing of the frame buffer border. In case of rectangle "A", the line crosses the stripe boundary into the next line, and fetches incorrect data. In case of rectangle "B", the rectangle includes a part of the memory outside the logical space allocated for the frame buffer.

Rectangle positioning and scrolling in the UltiEVC is applicable only to the slave layers and overlay rectangles. The master layer, which defines the image resolution and contains the background image, can have its rectangle positioned only at the beginning of a frame buffer in memory.

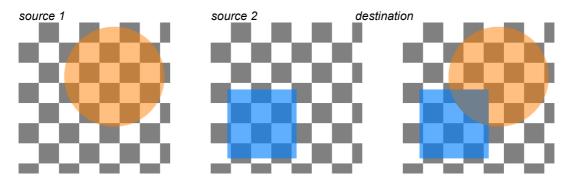

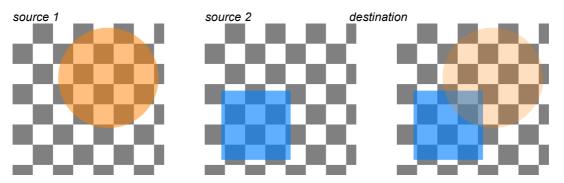

## 4.3.6 Multi -layer blending

Multi-layer blending is a process of combining multiple image windows into a single resulting image. UltiEVC supports blending of multiple image layers.

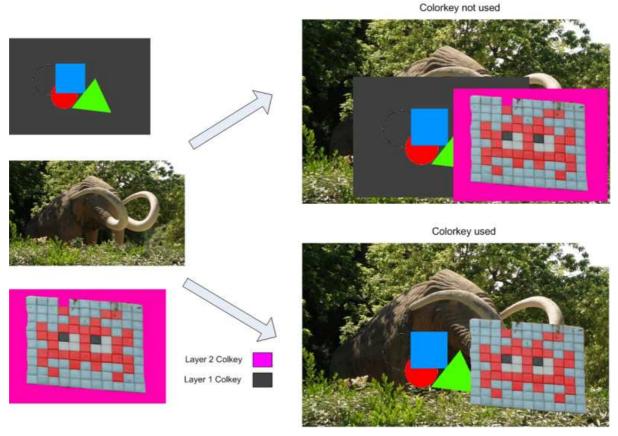

## 4.3.6.1 Basic Overlay (Color-keyed overlay)

The layers are overlayed so that the image data of the higher layer replaces the image data of the lower layer. The lower layer image data is however fetched from memory. In case the color key is used, any pixel that is matched to the color key is removed from the image and set to be transparent.

Color-keyed overlay

The color key (transparent color) can be set independently for each layer through the COLKEY parameter, however it cannot be applied to the master layer. If a transparent pixel is overlayed by a higher layer nontransparent pixel, it will be replaced by the higher layer.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 28/112

# 4.3.6.2 Alpha Blending

If Alpha blending is used, the two layers are combined using alpha compositing. Alpha compositing operation is defined on two pixels A and B, with the mixing factor alpha( $\alpha$ ) attached to the pixel A. The basic alpha operation defines a pixel C as

$$C = A * \alpha + B * (1 - \alpha)$$

The alpha blending operation results in an effect of transparent overlay. The pixel A appears overlayed over the pixel B with a transparency factor  $\alpha$ , where  $0 \le \alpha \le 1$ ,

The alpha operation is performed on each color component (R,G,B) independently.

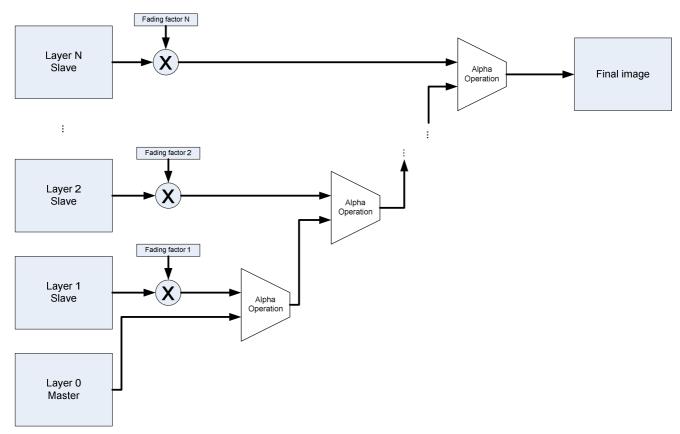

In UltiEVC, alpha blending can be performed between multiple layers, where overlay layers are consecutively blended into the result of the previous blending. The blending process starts with the master layer and the first overlay layer, and finishes with the last overlay layer.

Alpha blending between multiple layers

The equation used for blending of each color channel (red, green, or blue) in a particular overlay layer is:  $\alpha_i = \frac{\alpha_{yx}\alpha_{ch}}{256}$

$$\alpha_i = \frac{\alpha_i R_i R_{in}}{256}$$

$$R_i = \frac{\alpha_i C_i + (1 - \alpha_i) R_{i-1}}{256}$$

$$R_0 = C_0$$

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 29/112

For i>0, where  $R_i$  is the resulting pixel color for the current layer,  $\alpha_{px}$  is individual pixel alpha,  $\alpha_{q\bar{q}}$  is the overall fading alpha (layer fading factor),  $\alpha_i$  is the resultant per pixel alpha prescaled by the fading factor,  $C_i$  is the current layer pixel color, and  $R_{i-1}$  is the result of previous blending operation.

Image composited using alpha blending

Alpha information used in the blending process is an 8-bit number, from 0 to 255, allowing for 255 transparency levels, where 0xFF(255) generates a fully opaque pixel, and 0x0 stands for fully transparent pixel.

Note: The alpha value 0xFF is interpreted as a special case (255 is incremented to 256 in the calculation) to allow the calculation to produce a fully opaque pixel. That means that the step in alpha value from alpha = 0xFE to alpha = 0xFF is actually 2.

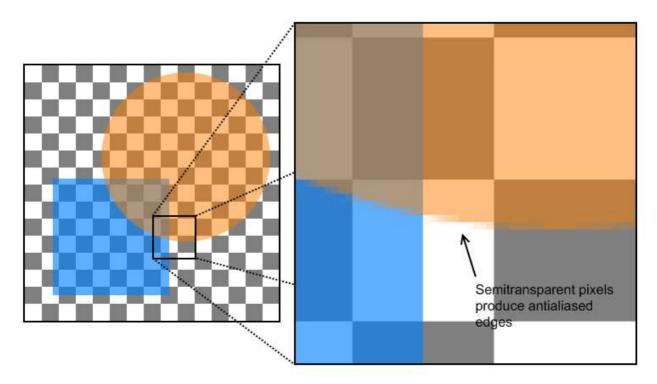

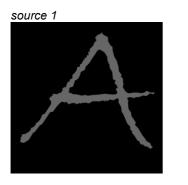

32-bit ARGB images have the alpha channel embedded in the image itself, allowing for individual alpha values,  $\alpha_{px}$ , for each pixel. This allows for advanced transparency effects, and is most prominently used for edge anti-aliasing, where the transparency of the boundary pixels is varied to create a smooth transition.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 30/112

Antialising through alpha blending

Images of a lower colordepth, and 24 bit RGB images without alpha information have no room for alpha factors and are interpreted as fully opaque ( $\alpha_{px}=255$ ). However, an 8-bit alpha channel can be attached to them by using dedicated alpha layers.

Each layer has an additional alpha prescaling factor, or a fading factor. The fading factor premultiplies the alpha channel of the layer (whether implied to opaque or defined by the pixel). This allows fading and definition of overall transparency for a single layer. The overall layer alpha  $\alpha_{\sigma h}$  is defined in the layer LALPHA parameter.

The master layer is always treated as completely opaque, and has no transparency.  $\alpha_{ch}$  and  $\alpha_{px}$  are set to 0xFF regardless of the actual setting. LALPHA is not defined on the master layer, hence  $R_0 = C_0$ .

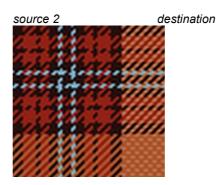

#### 4.3.6.3 Alpha mask layers

For 16-bit layers there is no space sufficient to add full alpha transparency information to the image. Also it may be desired to change the alpha channel without disturbing the original RGB data, 16 or 24 bit. For those purposes, Alpha mask layers are used.

Each slave layer can be used as the alpha mask layer for the layer with the previous index. When functioning in alpha mask mode, the layer fetches an 8-bit monochrome image. Each pixel of the monochrome image is attached as the alpha factor to the corresponding pixel of the layer displayed beneath it.

In order to have the pixel-by-pixel alignment of the color and the mask layer, the two visible rectangles have to be of the same size and the same position within the visible image. The LHOFF, LVOFF, LHRES and LVRES parameters of the two layers must always be kept identical between the two layers.

Areas outside of the alpha mask layer will be considered as having the alpha layer equal to 0, or completely transparent. If needed, the alpha mask layer can be moved around independently of the color layer, which will shift the transparency information (mask) over the underlying image.

## 4.3.7 Pixel color conversion and scrambling

Various flat panel displays require different color formats for image refresh. However, not all color formats are convenient for memory storage and operations in the image datapath and blending process. Some displays show colors by using a smaller number of bits, and compensate the remaining number of bits by pulse width modulation of individual pixels (FRC). Additionally, it is hard to create a blending pipeline to work with multiple/various color formats.

Pixel scrambling is a conversion process which translates the internal color format, or blender color format, to the external display color format. The pixel scrambler unit takes the result of the blender (in 8, 16 or 24 bit color) and translates it to the external display color format, pixel by pixel.

Pixel scrambling allows decoupling of the internal and the external color format. The internal color format is therefore aligned with the pipeline processing and software requirements.

UltiEVC supports pixel scrambling for the following combinations of internal and external color formats.

| External color formats | Internal color formats |       |       |

|------------------------|------------------------|-------|-------|

|                        | RGB8                   | RGB16 | RGB32 |

| RGB16                  | Yes                    | Yes   | Yes   |

Supported pixel scrambling combinations

# 4.3.8 Flat panel display control

For flat panel displays, the display control parameters define the timing of control signals, consisting of:

| <u> </u> |                                     |

|----------|-------------------------------------|

| Signal   | Function                            |

| disp_clk | Display clock                       |

| Vsync    | Vertical sync signal (frame start)  |

| Hsync    | Horizontal sync signal (line start) |

| Blank    | Blank/Pixel data valid signal       |

| pix_data | Pixel data                          |

The display clock is the driver for the synchronous logic of the flat panel display. It defines the time base of the display timing and the pixel data rate. The pixel data is output from the UltiEVC to the display synchronous to the display clock. Within the UltiEVC the output display clock can be inverted (new data can be output on rising or falling edge of the display clock) to ensure valid data sampling in the display.

Some displays do not use the blank (pixel valid) signal, but sample pixels on every active clock edge. For these displays, the clock must be active only when the valid pixel data is output. This functionality is supported through clock burst mode of the UltiEVC.

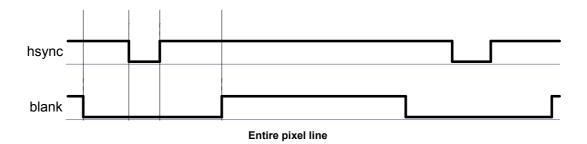

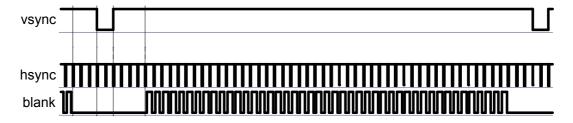

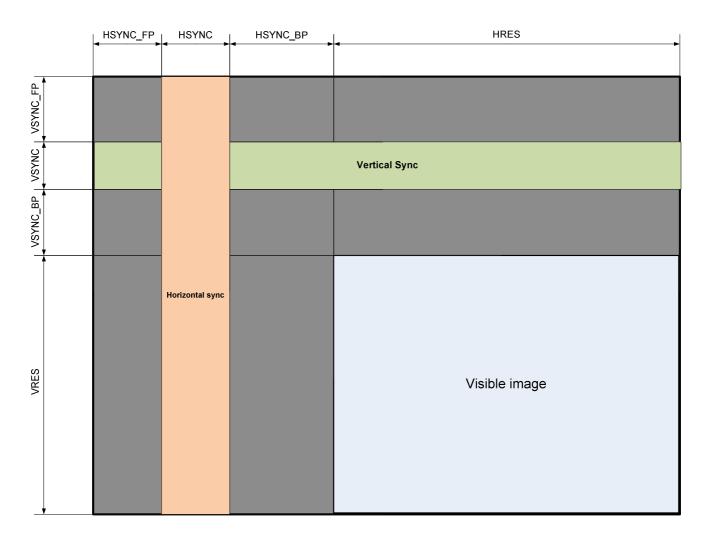

Flat panel displays are refreshed line by line. Therefore each frame consists of VRES line refresh cycles, where each line consists of HRES pixel data elements. HRES and VRES are the horizontal and vertical resolution, respectively.

Each line refresh has the following structure. For each line, all of the timing is expressed in periods of the display clock.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 32/112

The blank signal is asserted when valid pixel data is present on the pixel bus. The length of each blank impulse is equal to HRES periods of display clock, while the number of blank impulses in each frame is equal to VRES. The blank signal can be turned off, in which case it remains in inactive state.

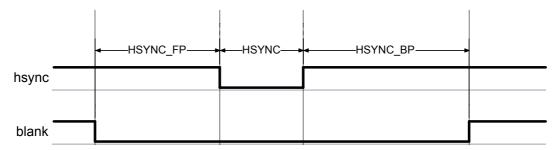

The hsync signal is used for line start detection. Length of hsync is always expressed in number of clock periods. Length of hsync is marked HSYNC on following picture. Each display can demand pauses between last pixel and assertion of hsync, or pause from deassertion of hsync to first pixel in new line. This intervals are also a expressed in clock periods and usually called hsync front porch (HSYNC FP on picture) and hsync back porch (HSYNC BP on picture).

Hsync front and back porches

The period of hsync signal can be calculated as HYNC\_FP + HSYNC + HSYNC\_BP + HRES. The hsync signal can be turned off, in which case it stays in inactive state.

The complete image frame consists of VRES line refresh cycles as shown below.

Full image frame

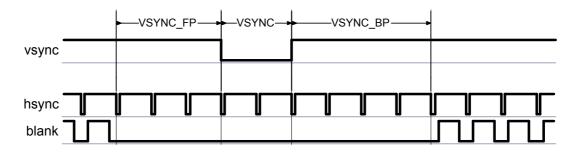

The vsync signal is used for frame start detection. Vsync timing parameters are expressed in number of hsync signal periods. In UltiEVC, the vsync signal always asserts and deasserts together with the asserting of the hsync signal. The length of vsync is marked VSYNC on the following picture.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 33/112

Each display can demand pauses between the last pixel line and the assertion of vsync, or a pause from deassertion of vsync to the first pixel line in the new frame. These intervals are also a multiple of the hsync signal period and are usually called vsync front porch (VSYNC\_FP on picture) and vsync back porch (VSYNC\_BP on picture). The vsync signal can be turned off, in which case it will remain in inactive state.

Vsync front and back porches

The overall refresh sequence can be visualised as the image being larger than the actual visible image, with horizontal and vertical sync areas in the nonvisible space.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 34/112

2D Visualization of flat panel display timing

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 35/112

# 4.3.9 Configuration and control

The registers are accessed through the AMBA APB interface. All registers are 32-bit and located on adjacent addresses.

The layer control registers accessed through the APB are shadowed in the EVC hardware. The update of the registers in the EVC hardware occurs automatically on each VSYNC. This prevents image artifacts which occur because of configuration changes during operation. Each frame is completely output using the same configuration, which prevents logic glitches.

The UltiEVC is controlled through an array of registers mapped within the AMBA APB address space of the core. All registers occupy 1 word (32 bits) of address space, even if their physical size is less, and are aligned to 1-word boundaries (The address is always a multiple of 4).

The register space is divided into a variable number of register banks. Each bank is 64 bytes in size.

Each register bank is assigned a specific function, and contains registers relevant to that function. The functions of register banks are summarized in the table below.

| Bank   | Function                              | Base address |

|--------|---------------------------------------|--------------|

| Bank 0 | Display control and timing parameters | 0x00         |

| Bank 1 | Master layer control parameters       | 0x40         |

| Bank 2 | Overlay layer 1 control parameters    | 0x80         |

| Bank 3 | Overlay layer 2 control parameters    | 0xC0         |

| Bank 4 | Overlay layer 3 control parameters    | 0x100        |

Bank 0 defines a separate set of registers, while banks 1 ... 4 define an identical set of registers, as each bank controls a generic image layer control structure.

For any register, the absolute AMBA address in the system is calculated as:

Register address = core base address + bank base address + register offset

### 4.3.9.1 Display parameter registers

The display control, signal and timing parameters are defined through 12 registers in bank 0. The register offset is calculated from the bank base address.

| Register | Bits | Access | Function                                    | Offset |

|----------|------|--------|---------------------------------------------|--------|

| HSY_FP   | 8    | R/W    | Horizontal sync front porch                 | 0x00   |

| HSY      | 8    | R/W    | Horizontal sync period                      | 0x04   |

| HSY_BP   | 8    | R/W    | Horizontal sync back porch                  | 80x0   |

| HRES     | 16   | R/W    | Horizontal resolution                       | 0x0C   |

| VSY_FP   | 8    | R/W    | Vertical sync front porch                   | 0x10   |

| VSY      | 8    | R/W    | Vertical sync                               | 0x14   |

| VSY_BP   | 8    | R/W    | Vertical sync back porch                    | 0x18   |

| VRES     | 16   | R/W    | Vertical resolution                         | 0x1C   |

| SCTRL    | 6    | R/W    | Signal enable & polarity control            | 0x20   |

| CLKCTRL  | 8    | R/W    | Clock selection and division control        | 0x24   |

| DCTRL    | 4    | R/W    | Display color depth and pixel merge control | 0x28   |

| PWRCTRL  | 4    | R/W    | Power control signals control               | 0x2C   |

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 36/112

**HSY FP**

Bank 0, offset 0x00

31 8 7 0

unused HSYNC\_FP

The HSY FP register contains the value of the horizontal front porch.

HSY\_FP[7:0] contains the HSYNC\_FP value, e.g. the number of display clock periods between the deassertion of blank signal and the assertion of hsync signal.

#### HSY

|        |     | Bank U, ottset uxu4 |

|--------|-----|---------------------|

| 31     | 8 7 | 0                   |

| unused |     | HSYNC               |

The HSY register contains the value of the horizontal sync. HSY[7:0] contain the HSYNC value, e.g. the number of display clock periods during which the hsync signal is asserted.

HSY BP

|   |        | Bank 0, offset 0x08 |

|---|--------|---------------------|

|   | 31 8   | 3 7 0               |

| ĺ | unused | HSYNC_BP            |

The HSY\_BP register contains the value of the horizontal back porch. HSY\_BP[7:0] contain the HSYNC\_BP value, e.g. the number of display clock periods between the deassertion of hsync signal and the assertion of blank signal.

**HRES**

|        | Bank 0, offset 0x0C |

|--------|---------------------|

| 31 16  | 15 0                |

| unused | HRES                |

The HRES register contains the value of the horizontal resolution. HRES[15:0] contain the HRES value, e.g. the number of pixels in a display line, and the number of display clock periods during which the blank signal is asserted.

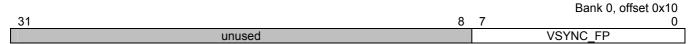

**VSY FP**

The VSY\_FP register contains the value of the vertical front porch.

VSY\_FP[7:0] contains the VSYNC\_FP value, e.g. the number of HSYNC periods between the last deassertion of blank signal in the previous frame and the assertion of vsync signal.

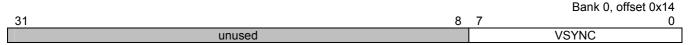

**VSY**

The VSY register contains the value of the vertical sync. VSY[7:0] contain the VSYNC value, e.g. the number of HSYNC periods during which the vsync signal is asserted.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 37/112

Bank 0 offeet 0x20

VSY BP

The VSY\_BP register contains the value of the vertical back porch. VSY\_BP[7:0] contain the VSYNC\_BP value, e.g. the number of display clock periods between the deassertion of the vsync signal and the first active line refresh cycle.

**VRES**

|        | Bank 0, offset 0x1C |

|--------|---------------------|

| 31 16  | 15 0                |

| Unused | VRES                |

The VRES register contains the value of the vertical resolution. VRES[15:0] contain the VRES value, e.g. the number of lines in a display frame, and the number of blank signal pulses within a display frame.

**SCTRL**

|        |   |       |      |       |      | Darik U, C | JIISEL UAZU |

|--------|---|-------|------|-------|------|------------|-------------|

| 31     | 6 | 5     | 4    | 3     | 2    | 1          | 0           |

| Unused |   | ENPOL | ENEN | HSPOL | HSEN | VSPOL      | VSEN        |

The SCTRL register defines whether the control signals VSYNC, HSYNC and BLANK(enable) are used, and what is their active polarity (value when the signal is asserted).

The VSEN, HSEN and ENEN flags define whether the VSYNC, HSYNC and BLANK(EN) signals are driven by the state machine or kept inactive. The VSPOL, HSPOL and ENPOL flags define the active state ("1" for active high, or "0" for active low) for VSYNC, HSYNC and BLANK(EN) signals, respectively.

| Flag  | Value | Behavior                                     |

|-------|-------|----------------------------------------------|

| VSEN  | 0     | VSYNC is disabled. Set to inactive state.    |

|       | 1     | VSYNC is enabled.                            |

| VSPOL | 0     | VSYNC is active low                          |

|       | 1     | VSYNC is active high                         |

| HSEN  | 0     | HSYNC is disabled. Set to inactive state.    |

|       | 1     | HSYNC is enabled.                            |

| HSPOL | 0     | HSYNC is active low                          |

|       | 1     | HSYNC is active high                         |

| ENEN  | 0     | BLANK/EN is disabled. Set to inactive state. |

|       | 1     | BLANK is enabled.                            |

| ENPOL | 0     | BLANK is active low                          |

|       | 1     | BLANK is active high                         |

**CLKCTRL**

|        |   |       |        |   |       |   | Bank 0, offset 0x24 |

|--------|---|-------|--------|---|-------|---|---------------------|

| 31     | 8 | 7     | 6      | 5 | 3     | 2 | 0                   |

| unused |   | CKINV | CKBRST |   | CKDIV |   | CKSEL               |

The CLKCTRL register defines the pixel clock frequency and behavior. Specific clock frequencies are generated within the UltiEVC, which can be later subjected to division to get the final pixel clock.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 38/112

Rank 0 offset 0x28

The flags CKSEL[2:0] define the base clock frequency.

| CKSEL[2:0] | Base clock frequency |

|------------|----------------------|

| 000        | 24 MHz               |

| 001        | 32 MHz               |

| 010        | 38 MHz               |

| 011        | 48 MHz               |

| 100        | 64 MHz               |

| 101        | 76 MHz               |

| 110        | 96 MHz               |

| 111        | Reserved             |

The flags CKDIV[2:0] define the division factor applied to the base clock frequency to obtain the final pixel clock frequency. (note here, that some division factors might generate already present base frequencies).

| CKDIV[2:0] | Base clock divider |  |  |  |

|------------|--------------------|--|--|--|

| 000        | 1 (no division)    |  |  |  |

| 001        | 2                  |  |  |  |

| 010        | 4                  |  |  |  |

| 011        | 8                  |  |  |  |

| 100        | Reserved           |  |  |  |

| 101        | Reserved           |  |  |  |

| 110        | Reserved           |  |  |  |

| 111        | Reserved           |  |  |  |

The CKBRST flag controls the clock behavior. When CKBRST is active, the clock will be active (toggling) only during the BLANK active period (pixel valid data period, even if blank signal is not enabled).

The CKINV flag controls clock polarity. When CKINV is high, the clock is inverted, and the pixel data will be synchronous to the falling edge of the display clock. Otherwise the data will be synchronous to the rising edge of the display clock.

| Flag    | Value | Behavior                                                     |  |  |  |  |

|---------|-------|--------------------------------------------------------------|--|--|--|--|

| CKBURST | 0     | risplay clock is free running.                               |  |  |  |  |

|         | 1     | Display clock is bursting only during blank periods.         |  |  |  |  |

| CKINV   | 0     | Display clock is normal, data synchronous to rising edge.    |  |  |  |  |

|         | 1     | Display clock is inverted, data synchronous to falling edge. |  |  |  |  |

### **DCTRL**

|        |   |   |        |   |       |   | Dank o, onset oxzo |

|--------|---|---|--------|---|-------|---|--------------------|

| 31     | 7 | 6 |        | 4 | 3     | 2 | 0                  |

| unused |   |   | BDEPTH |   | RGBBG |   | DCOLOR             |

|        |   |   |        |   |       |   |                    |

The DCTRL register defines the color depth and pixel scrambling settings for the current display. The display color depth and configuration is set through DCOLOR[2:0] parameter.

| DCOLOR[2:0]      | Bits per pixel | Available colors |

|------------------|----------------|------------------|

| 001              | 16             | 65536            |

| All other values | Reserved       |                  |

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 39/112

The RGBBG bit controls the color component order within the pixel. If set to "0", the order is RGB. If set to "1", the order is RBG.

| Flag  | Value | Behavior                |

|-------|-------|-------------------------|

| RGBBG | 0     | Color order RGB is used |

|       | 1     | Color order RBG is used |

The internal pixel format used by the blender (or largest BPP in layers) is set by the BDEPTH[2:0] parameter. Separation of the internal BPP (set by this parameter) and the external BPP (set by the DCOLOR) enables adapting output to any BPP or pixel format without changing internal hardware configuration.

| BDEPTH[2:0] | Bits per pixel | Available colors |

|-------------|----------------|------------------|

| 000         | Reserved       |                  |

| 001         | 8              | 256              |

| 010         | 16             | 65,536           |

| 011         | Reserved       |                  |

| 100         | 32             | 16,777,216       |

| 101         | Reserved       |                  |

| 110         | Reserved       |                  |

| 111         | Reserved       |                  |

Note: when UltiEVC is used in Alpha blending configuration, the BDEPTH parameter **must** be set to "100" as the blending color depth is always 32-bit when using the alpha blender.

#### **PWRCTRL**

|        |   |      |      | Dank U, U | IISELUXZU |

|--------|---|------|------|-----------|-----------|

| _ 31   | 4 | 3    | 2    | 1         | 0         |

| unused |   | BLEN | VEEN | VDEN      | VEN       |

The PWRCTRL register contains flags directly mapped to the external display control signals: enable backlight, enable VEE, enable VDD, and enable video signal.

The BLEN flag is mapped to BLIGHT EN external signal which controls the backlight and/or CCFL inverter.

The VEEN flag controls the VEE power control signal.

The VDEN flag controls the VDD power control signal.

The VEN flag controls the UltiEVC output. When the VEN flag is asserted, the display control state machine starts and the output signal tristate control is deactivated, starting the display refresh.

| Flag | Value | Behavior                                         |

|------|-------|--------------------------------------------------|

| VEN  | 0     | Video control signals are disabled and tristated |

|      | 1     | Video control signals are enabled and driven     |

| VDEN | 0     | VDD enable signal is deasserted                  |

|      | 1     | VDD enable signal is asserted                    |

| VEEN | 0     | VEE enable signal is deasserted                  |

|      | 1     | VEE enable signal is asserted                    |

| BLEN | 0     | Backlight enable signal is deasserted            |

|      | 1     | Backlight enable signal is asserted              |

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 40/112

# 4.3.9.2 Layer control registers

### **LBADDRn**

Banks 1..4, offset 0x0

31 BADDR

The LBADDRn contains the base address for an image layer. It contains an address in the video memory at which the first pixel of the layer's image is located.

The base address of the layer must be aligned to the color depth boundary. If color depth is 8-bit, the base address must be byte-aligned. For 16-bit pixels the address must be halfword-aligned. For 32 bit pixels the address must be word-aligned.

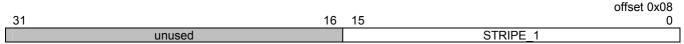

### **LSTRIPEn**

Banks 1..4, offset 0x04

31 0 LSTRIPE

The LSTRIPEn contains the stripe for an image layer and defines the image geometry. The LSTRIPE parameter is the length of a frame buffer line in bytes, decremented by 1.

The stripe is defined in bytes. The line length in pixels is derived by dividing the byte count with the BPP for the current layer. The stripe can be arbitrarily small and of any value, allowing linear memory organization for small images such as cursors.

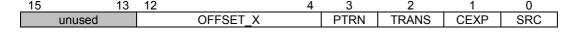

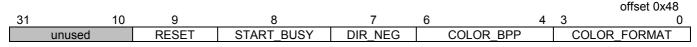

## **LCTRLn**

|        |       |      |      | Banks 14, offse | t 0x08 |

|--------|-------|------|------|-----------------|--------|

| 31 9   | 8     | 7    | 6    | 1 3             | 0      |

| unused | LYREN | CKEY | LBPP | LCOLF           |        |

The LCTRLn is the control register for an individual layer. It contains flags that control the layer's color depth, color format, and whether the layer is enabled. Additionally it contains control bits for the layer's memory fetcher and pipeline modules.

The LCOLF[3:0] value contains the information on the layer's color format.

| LCOLF[3:0] | Layer color format |

|------------|--------------------|

| 0000       | RGB                |

| 0001       | RGBA               |

| 0010       | Reserved           |

| 0011       | RGBAE              |

| 0100       | Reserved           |

| 0101       | Reserved           |

| 0110       | Reserved           |

| 0111       | Reserved           |

| 1000       | Reserved           |

| 1001       | Reserved           |

| 1010       | Reserved           |

| 1011       | Reserved           |

| 1100       | Reserved           |

| 1101       | Reserved           |

| 1110       | Reserved           |

| 1111       | Reserved           |

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 41/112

When LCOLF[3:0] is set to RGB, alpha information is neglected in the blending process, and the pixels are treated as 24-bit color. If alpha blending is disabled in the hardware configuration, this is the only available setting.

When LCOLF[3:0] is set to RGBA, the alpha information is used in the blending process. The alpha values attached to pixels are used in the blending process. For 16-bit layers, the alpha value is implicitly 0xFF. RGBA setting is available only for slave overlay layers.

When LCOLF[3:0] is set to RGBAE, the alpha information is used, but it is drawn from the adjacent upper overlay layer. If Layer 1 is set to be RGBAE, Layer 2 will be used as the alpha mask layer.

Note: the layer used as the alpha mask layer must be set to 8 BPP/RGB color. For most applications, the LHOFF, LVOFF, LHRES and LVRES values must match the values of the color layer which is being masked.

The LBPP[2:0] value defines what is the number of bits per pixel defined for the current layer.

| LBPP[2:0]            | Layer color depth          |

|----------------------|----------------------------|

| 000                  | Reserved                   |

| 001 8 bits per pixel |                            |

| 010                  | 16 bits per pixel          |

| 011                  | Reserved                   |

| 100                  | 32 bits per pixel (24 bpp) |

| 101                  | Reserved                   |

| 110                  | Reserved                   |

| 111                  | Reserved                   |

The LBPP defines the memory space occupied by a single pixel. The pixel formatting within the memory space is then further described by LCOLF.

The CKEY bit defines whether the color-key transparency is used on a layer, if the colorkey module is implemented within the layer's processing pipeline. In other case, this bit has no effect.

The LYREN bit defines whether the selected layer is active. If the layer is activated, then layer image data will be fetched from its memory area and shown on the screen. If not, the layer will be inactive, and the image data will not be fetched nor output to the screen.

| Flag  | Value | Behavior                                                        |  |

|-------|-------|-----------------------------------------------------------------|--|

| CKEY  | 0     | Colorkey is disabled. All colors are shown.                     |  |

|       | 1     | Colorkey is enabled. Transparent color is omitted from overlay. |  |

| LYREN | 0     | Layer is disabled.                                              |  |

|       | 1     | Layer is enabled, fetched and displayed.                        |  |

Note: when the master layer (Layer 0) is disabled, fetching from memory is disabled, but the Layer 0 outputs a rectangle filled with BASECOLOR, defined by the size of the display. Colorkey is undefined for Layer 0.

### **LBASECOLOR**

Bank 1, offset 0x0C

31 BASECOLOR

The BASECOLOR value defines the color being pumped into the master layer if the fetching of the image is disabled. The entire display image covered by the master layer will be set to pixels of the color written to the BASECOLOR register.

UM0011 (v1.00) – 14 July 2009 <u>www.exorint.net</u> 42/112

#### **LCOLKEYn**

Banks 2..4, offset 0x0C

COLKEY

The COLKEY value defines the transparent color within an individual overlay layer. If the colorkey module is not present in

The COLKEY value defines the transparent color within an individual overlay layer. If the colorkey module is not present in the pipeline configuration this register will have no effect. The written colorkey value is dependant on the color depth of the layer, the appropriate subrange of the register will always be used based on the colorkey depth and color format.

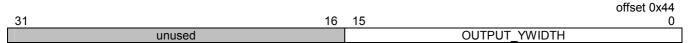

#### **LHRESn**

|        | Banks 14, offset 0x10 |

|--------|-----------------------|

| 31 16  | 15 0                  |

| unused | LHRES                 |

The LHRES register contains the value of the horizontal size for the layer. LHRES[15:0] contains the horizontal size of the overlay bounding rectangle in pixels. For layer 1 (master layer), this register has no effect as the master layer resolution is defined by the screen resolution.

#### **LVRESn**

|        | Banks 14, offset 0x14 |

|--------|-----------------------|

| 31 16  | 15 0                  |

| unused | LVRES                 |

The LVRES register contains the value of the vertical size for the layer. LHRES[15:0] contains the vertical size of the overlay bounding rectangle in pixels. For layer 1 (master layer), this register has no effect as the master layer resolution is defined by the screen resolution.

## LHOFFn

|        | Banks 14, offset 0x18 |

|--------|-----------------------|

| 31 16  | 15 0                  |

| unused | LHOFF                 |

The LHOFF register contains the value of the horizontal offset for the overlay bounding rectangle. LHOFF[15:0] contains the offset of the overlay bounding rectangle in pixels. For layer 1 (master layer), this register has no effect.

#### **LVOFFn**

|    |        |       | Banks 14, offset 0x1C |

|----|--------|-------|-----------------------|

| 31 | 16     | 15    | 0                     |

|    | unused | LVOFF |                       |

The LVOFF register contains the value of the vertical offset for the overlay bounding rectangle. LVOFF[15:0] contains the vertical size of the overlay bounding rectangle. For layer 1 (master layer), this register has no effect.

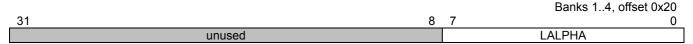

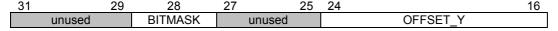

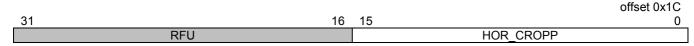

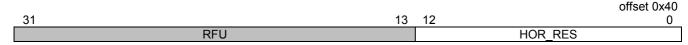

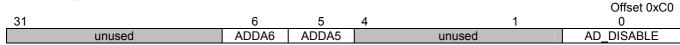

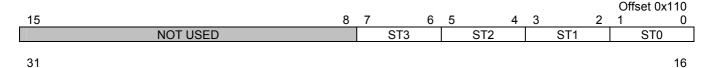

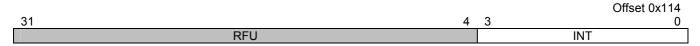

#### **LALPHAn**