## Linear IC converter

**CMOS**

# D/A Converter for Digital Tuning

(8-channel, 8-bit, on-chip OP amp, low-voltage)

## MB88347L

#### **■ DESCRIPTION**

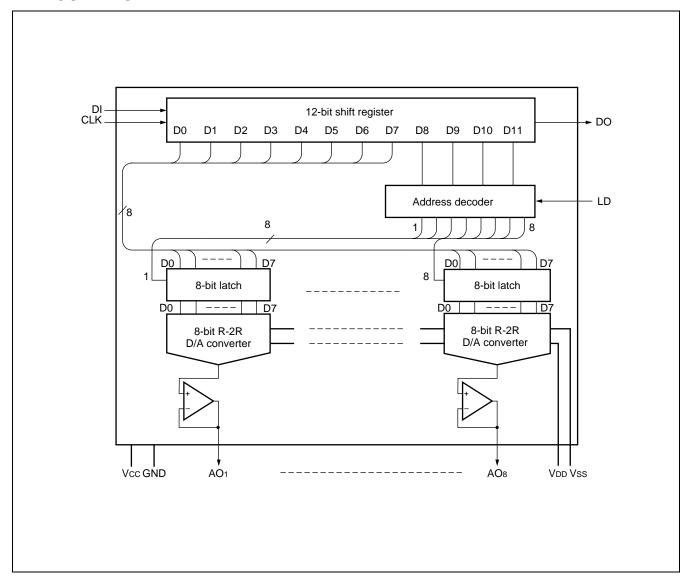

The MB88347L incorporates eight 8-bit D/A converter modules. This device operates at low supply voltage in the performance guarantee range from 2.7 to 3.6 V. It also contains an output amplifier, allowing driving at large current.

Since the MB88347L inputs data in serial mode, it requires only three control lines for data input and two or more MB88347L units can be cascaded.

The MB88347L is function and pin compatible with the MB88347 (5-volt supply voltage model). The MB88347L can therefore easily replace the MB88347 in a system, thereby reducing the system's voltage requirement.

The MB88347L is the best replacement for electronic variable resistors or screwdriver control resistors.

#### **■ FEATURES**

- Ultra-low power consumption (0.5 mW/ch: typical)

- Low voltage operation (Vcc = 2.7 to 3.6 V)

- Ultra-compact space-saving package (SSOP-16)

- Contains 8-channel R-2R type 8-bit D/A converter

- On-chip analog output amps (sink current max. 1.0 mA, source current max. 1.0 mA)

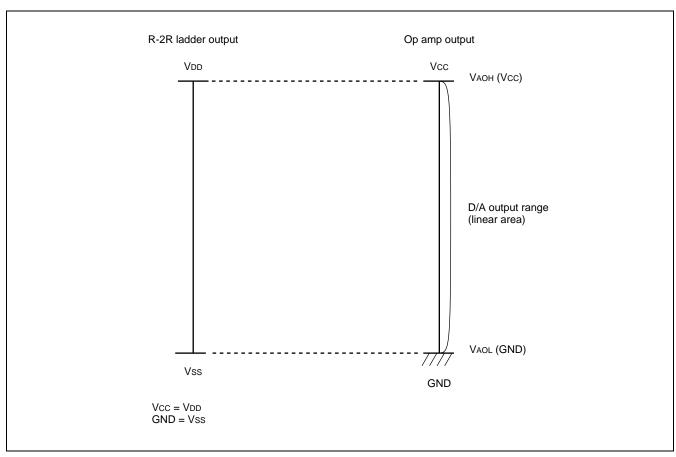

- Analog output range from 0 V to Vcc

- Two separate power supply/ground lines for MCU interface block/operational amplifier output buffer block and D/A converter block

- Serial data input, maximum operating speed 2.5 MHz

- CMOS process

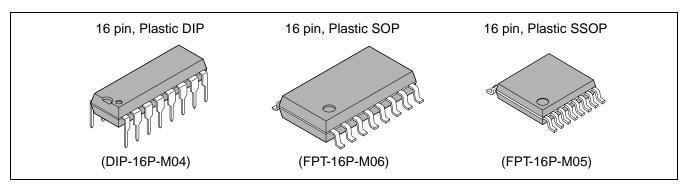

- Package lineup includes DIP 16-pin, SOP 16-pin, SSOP 16-pin

#### ■ PACKAGES

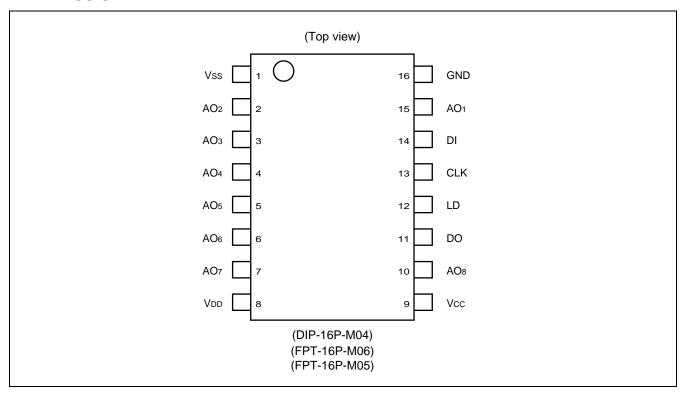

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin No.                          | Pin name                                             | I/O | Functions                                                                                                                                                                                                                |

|----------------------------------|------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

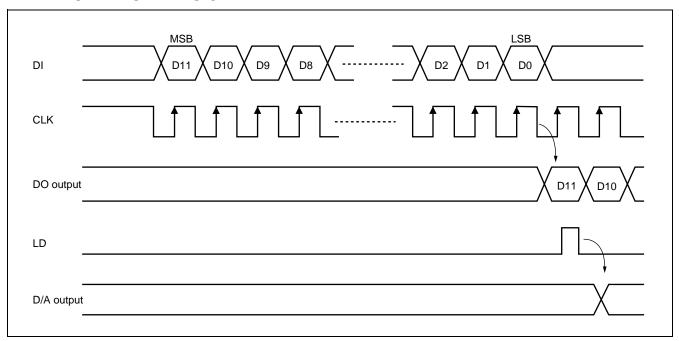

| 14                               | DI                                                   | I   | Serial data input pin. This pin inputs serial data with a data length of 12 bits. (Do not leave the pin floating.)                                                                                                       |

| 11                               | DO                                                   | 0   | This pin outputs the MSB data in the 12-bit shift register at the CLK falling edge.                                                                                                                                      |

| 13                               | CLK                                                  | I   | Shift clock input pin. The input signal from the DI pin enters the 12-bit shift register at the rising edge of the shift clock pulse. (Do not leave this pin floating.)                                                  |

| 12                               | LD                                                   | I   | When the LD pin inputs the High-level signal, shift register value is loaded to the decoder and the D/A output register. (Do not leave this pin floating. When data is not transferred, fix the pin to the "Low" level.) |

| 15<br>2<br>3<br>4<br>5<br>6<br>7 | AO1<br>AO2<br>AO3<br>AO4<br>AO5<br>AO6<br>AO7<br>AO8 | 0   | 8-bit D/A output with op amp.                                                                                                                                                                                            |

| 9                                | Vcc                                                  | _   | MCU interface and OP amp power-supply pin.                                                                                                                                                                               |

| 16                               | GND                                                  | _   | MCU interface and OP amp GND pin.                                                                                                                                                                                        |

| 8                                | Vdd                                                  | _   | D/A converter reference power (High) input pin.                                                                                                                                                                          |

| 1                                | Vss                                                  | _   | D/A converter reference power (Low) input pin.                                                                                                                                                                           |

### **■ BLOCK DIAGRAM**

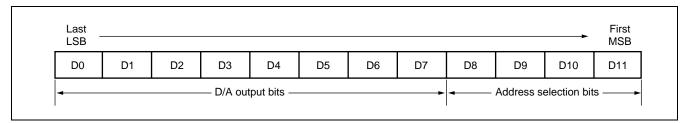

#### **■ DATA CONFIGURATION**

The MB88347L has a 12-bit shift register for chip control.

The 12-bit shift register must be used to set up data in the configuration shown below.

The data configuration has a total of 12 bits, for address selection and eight for D/A data output.

#### • D/A converter control signals

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D/A data output   |

|----|----|----|----|----|----|----|----|-------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | ≅ Vss             |

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | ≅ VLB × 1 + Vss   |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | ≅ VLB × 2 + Vss   |

|    | •  | •  | •  | •  | •  | •  | •  | · ·               |

| •  | •  | •  | •  | •  | •  | •  | •  | ·                 |

| 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | ≅ VLB × 254 + Vss |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | ≅ VLB × 255 + Vss |

Note: VLB = (VDD - VSS)/256

#### Address selection signals

| D8 | D9 | D10 | D11 | Address selection         |

|----|----|-----|-----|---------------------------|

| 0  | 0  | 0   | 0   | Don't Care                |

| 0  | 0  | 0   | 1   | AO <sub>1</sub> Selection |

| 0  | 0  | 1   | 0   | AO <sub>2</sub> Selection |

| 0  | 0  | 1   | 1   | AO <sub>3</sub> Selection |

| 0  | 1  | 0   | 0   | AO <sub>4</sub> Selection |

| 0  | 1  | 0   | 1   | AO <sub>5</sub> Selection |

| 0  | 1  | 1   | 0   | AO <sub>6</sub> Selection |

| 0  | 1  | 1   | 1   | AO <sub>7</sub> Selection |

| 1  | 0  | 0   | 0   | AO <sub>8</sub> Selection |

| 1  | 0  | 0   | 1   | Don't Care                |

| 1  | 0  | 1   | 0   | Don't Care                |

| 1  | 0  | 1   | 1   | Don't Care                |

| 1  | 1  | 0   | 0   | Don't Care                |

| 1  | 1  | 0   | 1   | Don't Care                |

| 1  | 1  | 1   | 0   | Don't Care                |

| 1  | 1  | 1   | 1   | Don't Care                |

#### **■ DATA SETTING TIMING CHART**

### ■ ANALOG OUTPUT VOLTAGE RANGE

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter             | Symbol | Conditions   | Rat         | Unit      |       |

|-----------------------|--------|--------------|-------------|-----------|-------|

| Parameter             | Symbol | Conditions   | Min.        | Max.      | Offic |

| Supply voltage        | Vcc    |              | -0.3        | 5.0       | V     |

| Supply voltage        | VDD    | Based on GND | -0.3*       | 5.0*      | V     |

| Input voltage         | Vin    | Ta = +25°C   | -0.3        | Vcc + 0.3 | V     |

| Output voltage        | Vouт   |              | -0.3        | Vcc + 0.3 | V     |

| Power consumption     | PD     | _            | _           | 250       | mW    |

| Operating temperature | Та     | _            | -20         | +85       | °C    |

| Storage temperature   | Tstg   | _            | <b>-</b> 55 | +150      | °C    |

<sup>\*:</sup>  $Vcc \ge Vdd$

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                         | Symbol   | Conditions        | Rat   | Unit       |       |  |

|-----------------------------------|----------|-------------------|-------|------------|-------|--|

| Farameter                         | Syllibol | Conditions        | Min.  | Max.       | Offic |  |

| Power supply voltage 1            | Vcc      | _                 | 2.7   | 3.6        | V     |  |

| Fower supply voltage 1            | GND      | _                 | Typic | Typical: 0 |       |  |

| Power supply voltage 2            | Vdd      | Vpp – Vss ≥ 2.0 V | 2.0   | Vcc        | V     |  |

| Fower supply voltage 2            | Vss      | VDD - VSS ≥ 2.0 V | GND   | Vcc -2.0   | V     |  |

| Analog output source current      | Ial      | Vcc = 3.0 V       | _     | 1.0        | mA    |  |

| Analog output sink current        | Іан      | Vcc = 3.0 V       | _     | 1.0        | mA    |  |

| Oscillation limit output capacity | Col      | _                 | _     | 1.0        | μF    |  |

| Digital data value range          | _        | _                 | #00   | #FF        | _     |  |

| Operating temperature             | Та       | _                 | -20   | +85        | °C    |  |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

> No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

#### (1) Digital block

(VDD, VCC = 2.7 V to 3.6 V (VCC  $\geq$  VDD), GND, Vss = 0 V, Ta = -20°C to +85°C)

| Parameter              | Symbol   | Pin name | Conditions                              |           | Unit |         |      |

|------------------------|----------|----------|-----------------------------------------|-----------|------|---------|------|

| Parameter              | Syllibol |          | Conditions                              | Min.      | Тур. | Max.    | Onit |

| Power supply voltage   | Vcc      |          | _                                       | 2.7       | 3.0  | 3.6     | V    |

| Power supply current 1 | lcc      | Vcc      | Operation at CLK = 1 MHz (with no load) | _         | 0.8  | 2.0     | mA   |

| Input leak current     | lilk     | CLK      | Vin = 0 V to Vcc                        | -10       | _    | 10      | μΑ   |

| L level input voltage  | VIL      | DI       | _                                       | _         | _    | 0.2 Vcc | V    |

| H level input voltage  | ViH      | LD       | _                                       | 0.8 Vcc   | _    | _       | V    |

| L level output voltage | Vol      | DO       | IoL = 2.5 mA                            | _         |      | 0.4     | V    |

| H level output voltage | Vон      | 00       | Іон = –400 μА                           | Vcc - 0.4 | _    | _       | V    |

#### (2) Analog block (1)

(VDD, VCC = 2.7 V to 3.6 V (VCC  $\geq$  VDD), GND, Vss = 0 V, Ta = -20°C to +85°C)

| Parameter                      | Symbol | Pin name   | Conditions                          |      | Unit |           |      |

|--------------------------------|--------|------------|-------------------------------------|------|------|-----------|------|

| raiailletei                    | Symbol |            | Conditions                          | Min. | Тур. | Max.      |      |

| Power consumption              | ldd    | VDD        | No load                             | _    | 0.6  | 1.0       | mA   |

| Analog voltage                 | VDD    | VDD        | Vpp – Vss ≥ 2.0 V                   | 2.0  | _    | Vcc       | V    |

| Analog voltage                 | Vss    | Vss        | V UU — V SS ≥ Z.U V                 | GND  | _    | Vcc - 2.0 | V    |

| Resolution                     | Res    |            | _                                   |      | 8    | _         | bits |

| Monotonic increase             | Rem    | AO1 to AO8 | No load                             | _    | 8    | _         | bits |

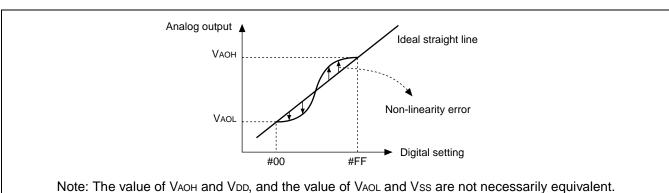

| Non-linearity error*1          | LE     | AOT IO AOS | $V_{DD} \le V_{CC} - 0.1 \text{ V}$ | -1.5 | _    | 1.5       | LSB  |

| Differential linearity error*2 | DLE    |            | Vss ≥ 0.1 V                         | -1.0 | _    | 1.0       | LSB  |

<sup>\*1:</sup> Deviation (error) in input/output curves with respect to an ideal straight line connecting output voltage at "00" and output voltage at "FF."

<sup>\*2:</sup> Deviation (error) in amplification with respect to theoretical increase in amplification per 1-bit increase in digital value.

7

### (3) Analog section (2)

$(Ta = -20^{\circ}C \text{ to } +85^{\circ}C)$

| Danamatan                | O. mala al         | Pin                | O a maliti a ma                                                                                                                                                                                                                 |                       | 11:5:4 |                       |      |

|--------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|-----------------------|------|

| Parameter                | Symbol             | name               | Conditions                                                                                                                                                                                                                      | Min.                  | Тур.   | Max.                  | Unit |

| Output minimum voltage 1 | VAOL1              |                    | $\begin{aligned} \text{VDD} &= \text{VCC} = 3.0 \text{ V} \\ \text{Vss} &= \text{GND} = 0.0 \text{ V} \\ \text{IAL} &= 0  \mu\text{A} \\ \text{Digital data} &= \#00 \end{aligned}$                                             | Vss                   | _      | Vss + 0.1             | V    |

| Output minimum voltage 2 | VAOL2              |                    | $\label{eq:DD} \begin{array}{l} \text{VDD} = \text{VCC} = 3.0 \text{ V} \\ \text{Vss} = \text{GND} = 0.0 \text{ V} \\ \text{IAL} = 500  \mu\text{A} \\ \text{Digital data} = \#00 \end{array}$                                  | Vss - 0.2             | Vss    | Vss + 0.2             | >    |

| Output minimum voltage 3 | V <sub>A</sub> OL3 |                    | $\begin{array}{c} \text{V}_{\text{DD}} = \text{V}_{\text{CC}} = 3.0 \text{ V} \\ \text{V}_{\text{SS}} = \text{GND} = 0.0 \text{ V} \\ \text{I}_{\text{AH}} = 500  \mu\text{A} \\ \text{Digital data} = \#00 \end{array}$        | Vss                   | _      | Vss + 0.2             | V    |

| Output minimum voltage 4 | VAOL4              |                    | $\begin{aligned} \text{V}_{\text{DD}} &= \text{V}_{\text{CC}} = 3.0 \text{ V} \\ \text{V}_{\text{SS}} &= \text{GND} = 0.0 \text{ V} \\ \text{I}_{\text{AL}} &= 1.0 \text{ mA} \\ \text{Digital data} &= \#00 \end{aligned}$     | Vss - 0.3             | Vss    | Vss + 0.3             | ٧    |

| Output minimum voltage 5 | VAOL5              | AO <sub>1</sub> to | V <sub>DD</sub> = V <sub>CC</sub> = 3.0 V<br>V <sub>SS</sub> = GND = 0.0 V<br>I <sub>AH</sub> = 1.0 mA<br>Digital data = #00                                                                                                    | Vss                   | _      | Vss + 0.3             | ٧    |

| Output maximum voltage 1 | Vaoh1              | AO8                | $\begin{aligned} \text{Vdd} &= \text{Vcc} = 3.0 \text{ V} \\ \text{Vss} &= \text{GND} = 0.0 \text{ V} \\ \text{IAL} &= 0  \mu\text{A} \\ \text{Digital data} &= \#\text{FF} \end{aligned}$                                      | VDD - 0.1             | _      | VDD                   | V    |

| Output maximum voltage 2 | Vаон2              |                    | $\begin{aligned} \text{Vdd} &= \text{Vcc} = 3.0 \text{ V} \\ \text{Vss} &= \text{GND} = 0.0 \text{ V} \\ \text{IAL} &= 500  \mu\text{A} \\ \text{Digital data} &= \#\text{FF} \end{aligned}$                                    | VDD - 0.2             | _      | VDD                   | V    |

| Output maximum voltage 3 | Vаонз              |                    | $\begin{array}{c} \text{V}_{\text{DD}} = \text{V}_{\text{CC}} = 3.0 \text{ V} \\ \text{V}_{\text{SS}} = \text{GND} = 0.0 \text{ V} \\ \text{I}_{\text{AH}} = 500  \mu\text{A} \\ \text{Digital data} = \#\text{FF} \end{array}$ | V <sub>DD</sub> - 0.2 | VDD    | V <sub>DD</sub> + 0.2 | V    |

| Output maximum voltage 4 | Vаон4              |                    | V <sub>DD</sub> = V <sub>CC</sub> = 3.0 V<br>V <sub>SS</sub> = GND = 0.0 V<br>I <sub>AL</sub> = 1.0 mA<br>Digital data = #FF                                                                                                    | VDD - 0.3             | _      | VDD                   | V    |

| Output maximum voltage 5 | V <sub>A</sub> OH5 |                    | VDD = VCC = 3.0 V<br>VSS = GND = 0.0 V<br>IAH = 1.0 mA<br>Digital data = #FF                                                                                                                                                    | VDD - 0.3             | VDD    | VDD + 0.3             | V    |

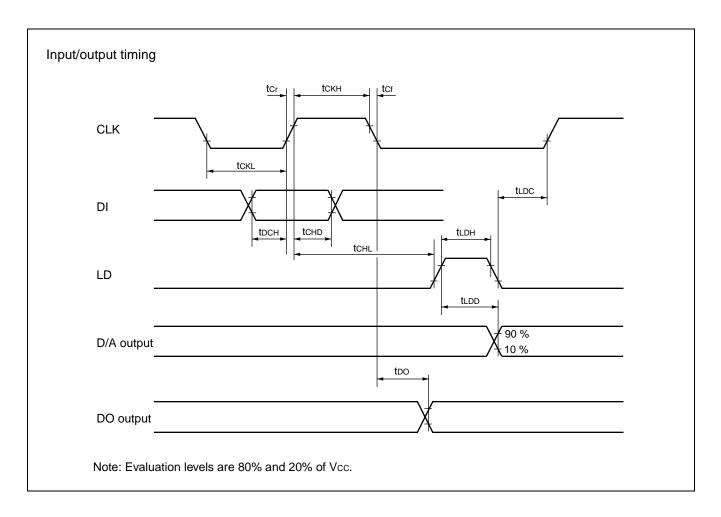

#### 2. AC Characteristics

(VDD, VCC = 2.7 V to 3.6 V (VCC  $\geq$  VDD), GND, Vss = 0 V, Ta =  $-20^{\circ}$ C to  $+85^{\circ}$ C)

| Parameter                          | Symbol     | Conditions                 | Rat  | ing  | - Unit |

|------------------------------------|------------|----------------------------|------|------|--------|

| Parameter                          | Symbol     | Conditions                 | Min. | Max. | - Onit |

| Clock L level pulse width          | tckl       | _                          | 200  | _    | ns     |

| Clock H level pulse width          | tскн       | _                          | 200  | _    | ns     |

| Clock rise time<br>Clock fall time | tCr<br>tCf | _                          | _    | 200  | ns     |

| Data setup time                    | tосн       | _                          | 30   | _    | ns     |

| Data hold time                     | tchd       | _                          | 60   | _    | ns     |

| Load setup time                    | tchl       | _                          | 200  | _    | ns     |

| Load hold time                     | tldc       | _                          | 100  | _    | ns     |

| Load H level pulse width           | tldh       | _                          | 100  | _    | ns     |

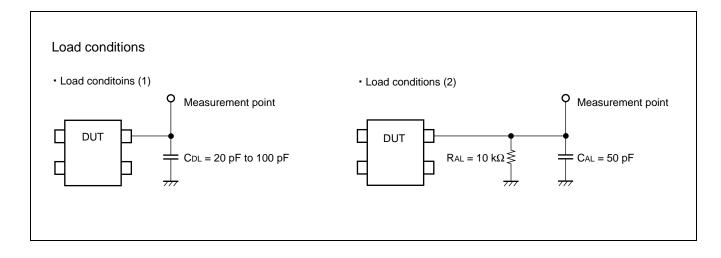

| Data output delay time             | tDO        | See "Load conditions (1)." | _    | 170  | ns     |

| D/A output settling time           | tldd       | See "Load conditions (2)." | _    | 200  | μS     |

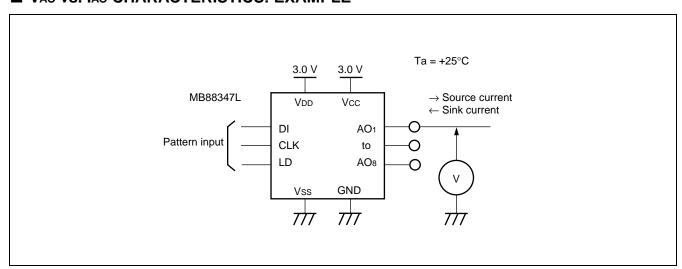

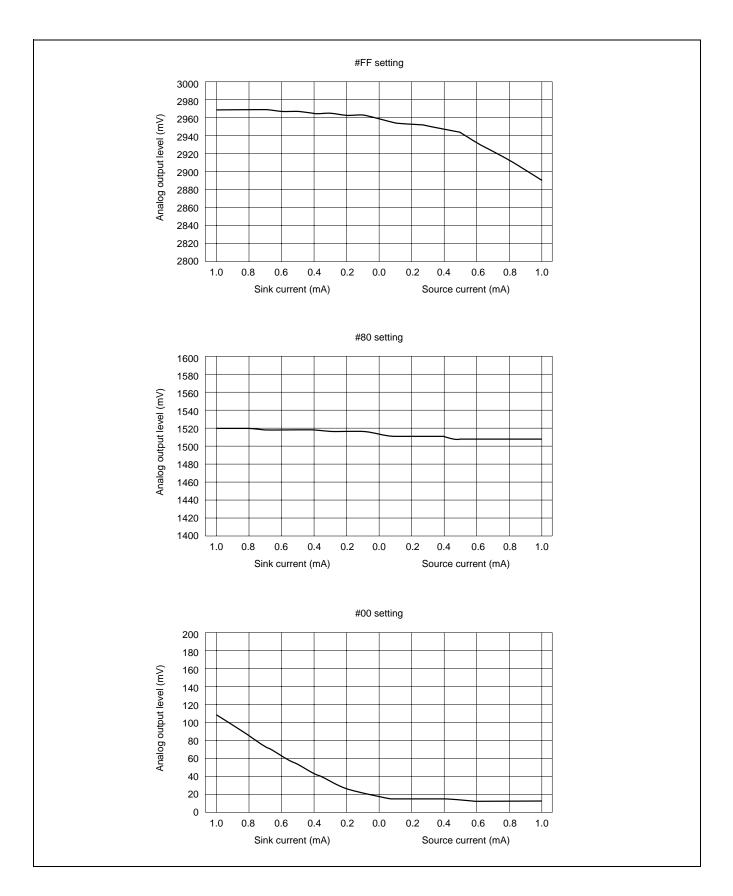

### ■ Vao vs. Iao CHARACTERISTICS: EXAMPLE

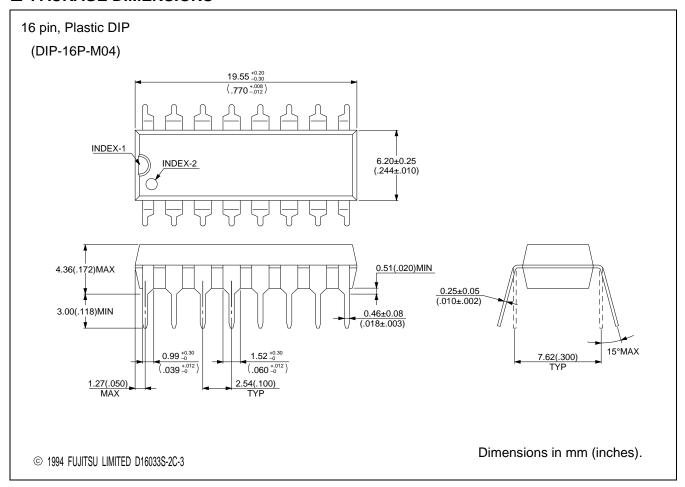

## **■** ORDERING INFORMATION

| Part number | Package                               | Remarks |

|-------------|---------------------------------------|---------|

| MB88347LP   | 16 pin, Plastic DIP<br>(DIP-16P-M04)  |         |

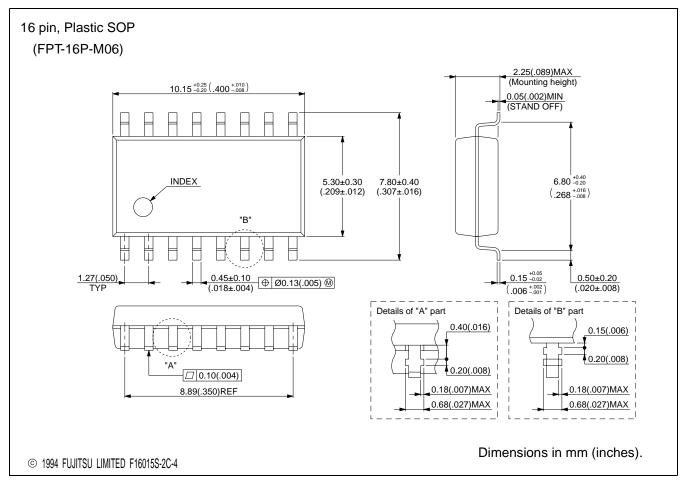

| MB88347LPF  | 16 pin, Plastic SOP<br>(FPT-16P-M06)  |         |

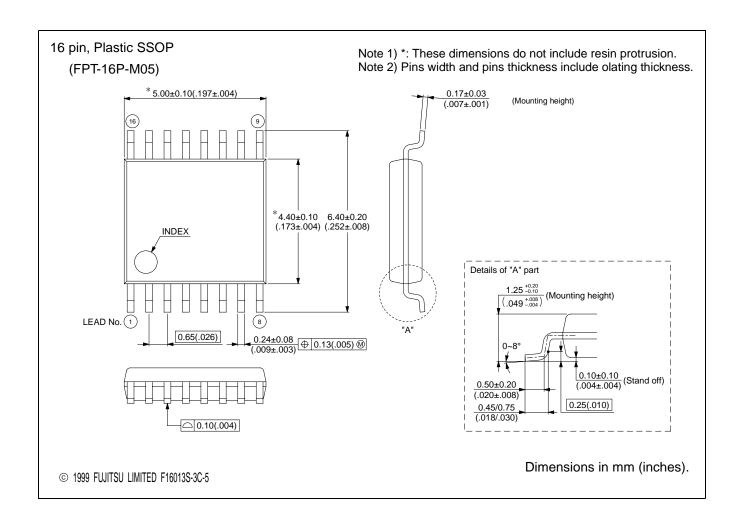

| MB88347LPFV | 16 pin, Plastic SSOP<br>(FPT-16P-M05) |         |

#### **■ PACKAGE DIMENSIONS**

(Continued)

(Continued)

### **FUJITSU MICROELECTRONICS LIMITED**

Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0722, Japan Tel: +81-3-5322-3347 Fax: +81-3-5322-3387 http://jp.fujitsu.com/fml/en/

For further information please contact:

#### **North and South America**

FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333

Sunnyvale, CA 94085-5401, U.S.A.

Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://www.fma.fujitsu.com/

#### Europe

FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122

Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/microelectronics/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 206 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu,Seoul 135-280 Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

http://www.fmk.fujitsu.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE LTD.

151 Lorong Chuan, #05-08 New Tech Park,

Singapore 556741

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. Rm.3102, Bund Center, No.222 Yan An Road(E), Shanghai 200002, China Tel: +86-21-6335-1560 Fax: +86-21-6335-1605 http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD.

10/F., World Commerce Centre, 11 Canton Road

Tsimshatsui, Kowloon

Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/tw

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.