# PCI-EXPRESS GEN 1, GEN 2, & GEN 3 TWO OUTPUT CLOCK GENERATOR WITH 25 MHz REFERENCE CLOCK

#### **Features**

- PCI-Express Gen 1, Gen 2 & Gen 3 compliant

- Supports Serial ATA (SATA) at 100 MHz

- Low power, differential outputs

- No termination resistor required

- Dedicated output enable hardware pins for each clock

- Dedicated hardware pins for spread spectrum and frequency control on differential outputs

- Up to two PCI-Express clocks

- 25 MHz reference clock

- 25 MHz crystal input or clock input

- Signal integrity tuning

- I<sup>2</sup>C support with readback capabilities

- Triangular spread spectrum profile for maximum electromagnetic interference (EMI) reduction

- Extended temperature -40 to 85 °C

- 3.3 V power supply

- 24-pin QFN package

## **Applications**

- Network attached storage

- Multi-function printer

- Wireless access point

- Routers

#### **Description**

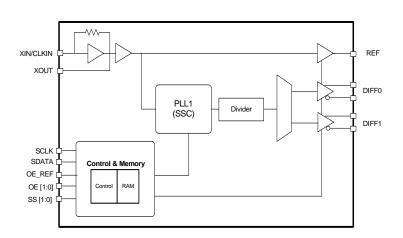

The Si52142 is a spread-spectrum enabled PCIe clock generator that can source two PCIe clocks and a 25 MHz reference clock. The device has three hardware output enable pins for enabling the respective outputs, and two hardware pins to control spread spectrum and frequency on PCIe clock outputs. In addition to the hardware control pins, I<sup>2</sup>C programmability is also available to dynamically control skew, edge rate, and amplitude on the true, compliment, or both differential signals on the PCIe clock outputs. This control feature enables optimal signal integrity as well as optimal EMI signature on the PCIe clock outputs. Refer to AN636 for signal integrity and configurability.

#### **Functional Block Diagram**

Patents pending

2

# TABLE OF CONTENTS

| <u>Section</u>                  | <u>Page</u> |

|---------------------------------|-------------|

| 1. Electrical Specifications    | 4           |

| 2. Functional Description       |             |

| 2.1. Crystal Recommendations    |             |

| 2.2. OÉ Pin Definition          |             |

| 2.3. OE Assertion               | 8           |

| 2.4. OE Deassertion             | 8           |

| 2.5. SS[1:0] Pin Definition     | 3           |

| 3. Test and Measurement Setup   |             |

| 4. Control Registers            |             |

| 4.1. I2C Interface              | 11          |

| 4.2. Data Protocol              |             |

| 5. Pin Descriptions: 24-Pin QFN |             |

| 6. Ordering Guide               |             |

| 7. Package Outline              |             |

| Document Change List            |             |

| Contact Information             |             |

3

# 1. Electrical Specifications

**Table 1. DC Electrical Specifications**

| Parameter                                        | Symbol               | Test Condition                                                             | Min                   | Тур | Max                   | Unit |

|--------------------------------------------------|----------------------|----------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| 3.3 V Operating Voltage                          | VDD core             | 3.3 ± 5%                                                                   | 3.135                 | 3.3 | 3.465                 | V    |

| 3.3 V Input High Voltage                         | V <sub>IH</sub>      | Control input pins                                                         | 2.0                   | _   | V <sub>DD</sub> + 0.3 | V    |

| 3.3 V Input Low Voltage                          | V <sub>IL</sub>      | Control input pins                                                         | V <sub>SS</sub> – 0.3 | _   | 0.8                   | V    |

| Input High Voltage                               | V <sub>IHI2C</sub>   | SDATA, SCLK                                                                | 2.2                   |     | _                     | V    |

| Input Low Voltage                                | V <sub>ILI2C</sub>   | SDATA, SCLK                                                                | _                     |     | 1.0                   | V    |

| Input High Leakage Current                       | I <sub>IH</sub>      | Except internal pull-down resistors, 0 < V <sub>IN</sub> < V <sub>DD</sub> | _                     | _   | 5                     | μА   |

| Input Low Leakage Current                        | I <sub>IL</sub>      | Except internal pull-up resistors, 0 < V <sub>IN</sub> < V <sub>DD</sub>   | <b>-</b> 5            | _   | _                     | μА   |

| 3.3 V Output High Voltage (Single-Ended Outputs) | V <sub>OH</sub>      | I <sub>OH</sub> = -1 mA                                                    | 2.4                   | 1   | _                     | V    |

| 3.3 V Output High Voltage (Single-Ended Outputs) | V <sub>OL</sub>      | I <sub>OL</sub> = 1 mA                                                     |                       | 1   | 0.4                   | V    |

| High-impedance Output Current                    | I <sub>OZ</sub>      |                                                                            | -10                   |     | 10                    | μA   |

| Input Pin Capacitance                            | C <sub>IN</sub>      |                                                                            | 1.5                   | _   | 5                     | pF   |

| Output Pin Capacitance                           | C <sub>OUT</sub>     |                                                                            |                       | _   | 6                     | pF   |

| Pin Inductance                                   | L <sub>IN</sub>      |                                                                            | _                     | _   | 7                     | nΗ   |

| Dynamic Supply Current                           | I <sub>DD_3.3V</sub> | All outputs enabled. Differential clocks with 5" traces and 2 pF load.     | _                     | _   | 40                    | mA   |

**Table 2. AC Electrical Specifications**

| Parameter                                                | Symbol                          | Condition                                      | Min  | Тур  | Max     | Unit |

|----------------------------------------------------------|---------------------------------|------------------------------------------------|------|------|---------|------|

| Crystal                                                  |                                 |                                                |      |      |         |      |

| Long-term Accuracy                                       | L <sub>ACC</sub>                | Measured at VDD/2 differential                 | _    | _    | 250     | ppm  |

| Clock Input                                              |                                 |                                                |      |      |         |      |

| Duty Cycle                                               | T <sub>DC</sub>                 | Measured at VDD/2                              | 45   | _    | 55      | %    |

| CLKIN Rising and Falling Slew Rate                       | T <sub>R</sub> /T <sub>F</sub>  | Measured between 0.2 $V_{DD}$ and 0.8 $V_{DD}$ | 0.5  | _    | 4.0     | V/ns |

| Cycle to Cycle Jitter                                    | T <sub>CCJ</sub>                | Measured at VDD/2                              | _    | _    | 250     | ps   |

| Long Term Jitter                                         | T <sub>LTJ</sub>                | Measured at VDD/2                              | _    | _    | 350     | ps   |

| Input High Voltage                                       | V <sub>IH</sub>                 | XIN/CLKIN pin                                  | 2    | _    | VDD+0.3 | V    |

| Input Low Voltage                                        | V <sub>IL</sub>                 | XIN/CLKIN pin                                  | _    | _    | 0.8     | V    |

| Input High Current                                       | I <sub>IH</sub>                 | XIN/CLKIN pin, VIN = VDD                       | _    | _    | 35      | μΑ   |

| Input Low Current                                        | I <sub>IL</sub>                 | XIN/CLKIN pin, 0 < VIN < 0.8                   | -35  | _    | _       | μA   |

| DIFF at 0.7 V                                            |                                 |                                                |      |      |         |      |

| Duty Cycle                                               | T <sub>DC</sub>                 | Measured at 0 V differential                   | 45   | _    | 55      | %    |

| Any Clock Skew from the Earliest Bank to the Latest Bank | T <sub>SKEW</sub>               | Measured at 0 V differential                   | _    | _    | 50      | ps   |

| Cycle to Cycle Jitter                                    | T <sub>CCJ</sub>                | Measured at 0 V differential                   | _    | 35   | 50      | ps   |

| PCIe Gen 1 Pk-Pk Jitter                                  | Pk-Pk                           | PCIe Gen 1                                     | 0    | 40   | 86      | ps   |

| PCIe Gen 2 Phase Jitter                                  | RMS <sub>GEN2</sub>             | 10 kHz < F < 1.5 MHz                           | 0    | 2    | 3.0     | ps   |

|                                                          |                                 | 1.5 MHz< F < Nyquist Rate                      | 0    | 2    | 3.1     | ps   |

| PCIe Gen 3 Phase Jitter                                  | RMS <sub>GEN3</sub>             | Includes PLL BW 2-4 MHz<br>(CDR = 10 MHz)      | 0    | 0.5  | 1.0     | ps   |

| Long Term Accuracy                                       | L <sub>ACC</sub>                | Measured at 0 V differential                   | _    | _    | 100     | ppm  |

| Rising/Falling Slew Rate                                 | T <sub>R</sub> / T <sub>F</sub> | Measured differentially from ±150 mV           | 1    | _    | 8       | V/ns |

| Voltage High                                             | V <sub>HIGH</sub>               |                                                | _    | _    | 1.15    | V    |

| Voltage Low                                              | $V_{LOW}$                       |                                                | -0.3 | _    | _       | V    |

| Crossing Point Voltage at 0.7 V Swing                    | V <sub>OX</sub>                 |                                                | 300  | _    | 550     | mV   |

| Spread Range                                             | SPR                             | Down spread                                    | _    | -0.5 | _       | %    |

| Modulation Frequency                                     | F <sub>MOD</sub>                |                                                | 30   | 31.5 | 33      | kHz  |

| Note: Visit www.pcisig.com for co                        | mplete PCIe s                   | pecifications.                                 |      | •    | •       |      |

**Table 2. AC Electrical Specifications (Continued)**

|                                 | Condition                                                                             | Min                                                                                                                                                           | Тур                                                                                                                                                                     | Max                                                                                                                                                                             | Unit                                                                                                                                                                                                                                                                                                               |

|---------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 |                                                                                       |                                                                                                                                                               |                                                                                                                                                                         |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                    |

| T <sub>DC</sub>                 | Measurement at 1.5 V                                                                  | 45                                                                                                                                                            | _                                                                                                                                                                       | 55                                                                                                                                                                              | %                                                                                                                                                                                                                                                                                                                  |

| T <sub>R</sub> / T <sub>F</sub> | Measured between 0.8 and 2.0 V                                                        | 1.0                                                                                                                                                           | _                                                                                                                                                                       | 4.0                                                                                                                                                                             | V/ns                                                                                                                                                                                                                                                                                                               |

| T <sub>CCJ</sub>                | Measurement at 1.5 V                                                                  | _                                                                                                                                                             | _                                                                                                                                                                       | 300                                                                                                                                                                             | ps                                                                                                                                                                                                                                                                                                                 |

| L <sub>ACC</sub>                | Measured at 1.5 V                                                                     | _                                                                                                                                                             | _                                                                                                                                                                       | 100                                                                                                                                                                             | ppm                                                                                                                                                                                                                                                                                                                |

|                                 |                                                                                       |                                                                                                                                                               |                                                                                                                                                                         |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                    |

| T <sub>STABLE</sub>             |                                                                                       | _                                                                                                                                                             | _                                                                                                                                                                       | 1.8                                                                                                                                                                             | ms                                                                                                                                                                                                                                                                                                                 |

| T <sub>SS</sub>                 |                                                                                       | 10.0                                                                                                                                                          | _                                                                                                                                                                       | _                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                 |

|                                 | T <sub>R</sub> / T <sub>F</sub> T <sub>CCJ</sub> L <sub>ACC</sub> T <sub>STABLE</sub> | T <sub>R</sub> /T <sub>F</sub> Measured between 0.8 and 2.0 V  T <sub>CCJ</sub> Measurement at 1.5 V  L <sub>ACC</sub> Measured at 1.5 V  T <sub>STABLE</sub> | T <sub>R</sub> /T <sub>F</sub> Measured between 0.8 and 2.0 V 1.0  T <sub>CCJ</sub> Measurement at 1.5 V —  L <sub>ACC</sub> Measured at 1.5 V —  T <sub>STABLE</sub> — | T <sub>R</sub> /T <sub>F</sub> Measured between 0.8 and 2.0 V 1.0 —  T <sub>CCJ</sub> Measurement at 1.5 V — —  L <sub>ACC</sub> Measured at 1.5 V — —  T <sub>STABLE</sub> — — | T <sub>R</sub> /T <sub>F</sub> Measured between 0.8 and 2.0 V         1.0         —         4.0           T <sub>CCJ</sub> Measurement at 1.5 V         —         —         300           L <sub>ACC</sub> Measured at 1.5 V         —         —         100           T <sub>STABLE</sub> —         —         1.8 |

**Table 3. Absolute Maximum Conditions**

| Parameter                         | Symbol             | Condition                   | Min  | Тур | Max | Unit     |

|-----------------------------------|--------------------|-----------------------------|------|-----|-----|----------|

| Main Supply Voltage               | $V_{DD_3.3V}$      | Functional                  | _    | _   | 4.6 | V        |

| Input Voltage                     | V <sub>IN</sub>    | Relative to V <sub>SS</sub> | -0.5 | 1   | 4.6 | $V_{DC}$ |

| Temperature, Storage              | T <sub>S</sub>     | Non-functional              | -65  | _   | 150 | °C       |

| Temperature, Operating Ambient    | T <sub>A</sub>     | Functional                  | -40  |     | 85  | °C       |

| Temperature, Junction             | T <sub>J</sub>     | Functional                  | _    | _   | 150 | °C       |

| Dissipation, Junction to Case     | Ø <sub>JC</sub>    | JEDEC (JESD 51)             | _    |     | 35  | °C/W     |

| Dissipation, Junction to Ambient  | Ø <sub>JA</sub>    | JEDEC (JESD 51)             | _    | _   | 37  | °C/W     |

| ESD Protection (Human Body Model) | ESD <sub>HBM</sub> | JEDEC (JESD 22-A114)        | 2000 | _   | _   | V        |

| Flammability Rating               | UL-94              | UL (Class)                  |      | V-0 |     |          |

**Note:** While using multiple power supplies, the voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is not required.

## 2. Functional Description

### 2.1. Crystal Recommendations

The clock device requires a parallel resonance crystal.

**Table 4. Crystal Recommendations**

| Frequency<br>(Fund) | Cut | Loading  | Load Cap | Shunt<br>Cap (max) | Motional (max) | Tolerance<br>(max) | Stability (max) | Aging (max) |

|---------------------|-----|----------|----------|--------------------|----------------|--------------------|-----------------|-------------|

| 25 MHz              | AT  | Parallel | 12–15 pF | 5 pF               | 0.016 pF       | 35 ppm             | 30 ppm          | 5 ppm       |

#### 2.1.1. Crystal Loading

Crystal loading is critical for ppm accuracy. In order to achieve low/zero ppm error, use the calculations in "2.1.2. Calculating Load Capacitors" to estimate the appropriate capacitive loading (CL).

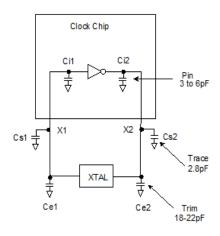

Figure 1 shows a typical crystal configuration using the two trim capacitors. It is important that the trim capacitors are in series with the crystal.

Figure 1. Crystal Capacitive Clarification

#### 2.1.2. Calculating Load Capacitors

In addition to the standard external trim capacitors, consider the trace capacitance and pin capacitance to calculate the crystal loading correctly. Again, the capacitance on each side is in series with the crystal. The total capacitance on both side is twice the specified crystal load capacitance (CL). Trim capacitors are calculated to provide equal capacitive loading on both sides.

Figure 2. Crystal Loading Example

Use the following formulas to calculate the trim capacitor values for Ce1 and Ce2.

Load Capacitance (each side)

$$Ce = 2 \times CL - (Cs + Ci)$$

Total Capacitance (as seen by the crystal)

CLe =

$$\frac{1}{\left(\frac{1}{Ce1 + Cs1 + Ci1} + \frac{1}{Ce2 + Cs2 + Ci2}\right)}$$

■ CL: Crystal load capacitance

■ CLe: Actual loading seen by crystal using standard value trim capacitors

Ce: External trim capacitors

Cs: Stray capacitance (terraced)

■ Ci: Internal capacitance (lead frame, bond wires, etc.)

#### 2.2. OE Pin Definition

The OE pins are active high inputs used to enable and disable the output clocks. To enable the output clock, the OE pin needs to be logic high and the  $I^2C$  output enable bit needs to be logic high. There are two methods to disable the output clocks: the OE is pulled to a logic low, or the  $I^2C$  enable bit is set to a logic low. The OE pins is required to be driven at all time and even though it has an internally 100 k $\Omega$  resistor.

#### 2.3. OE Assertion

The OE signals are active high input used for synchronous stopping and starting the output clocks respectively while the rest of the clock generator continues to function. The assertion of the OE signal by making it logic high causes stopped respective output clocks to resume normal operation. No short or stretched clock pulses are produced when the clock resumes. The maximum latency from the assertion to active outputs is no more than two to six output clock cycles.

#### 2.4. OE Deassertion

When the OE pin is deasserted by making its logic low, the corresponding output clocks are stopped cleanly, and the final output state is driven low.

## 2.5. SS[1:0] Pin Definition

SS[1:0] are active inputs used to select differential output frequency and enable spread of -0.5% on all DIFF outputs as per Table 5.

Table 5. SS0 and SS1 Frequency/Spread Selection

| SS1 | SS0 | Differential Differential Spread |            | Configuration |

|-----|-----|----------------------------------|------------|---------------|

| 0   | 0   | 100 MHz                          | Spread Off | Default       |

| 0   | 1   | 100 MHz -0.50%                   |            |               |

| 1   | 0   | 125 MHz                          | Spread Off |               |

| 1   | 1   | 200 MHz                          | Spread Off |               |

## 3. Test and Measurement Setup

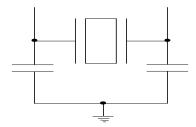

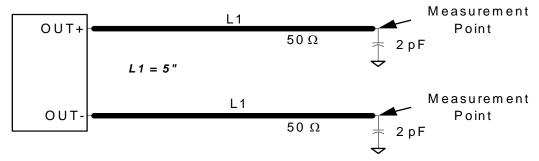

This diagram shows the test load configuration for the differential clock signals.

Figure 3. 0.7 V Differential Load Configuration

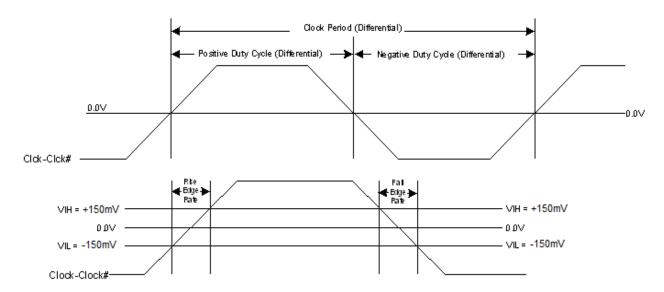

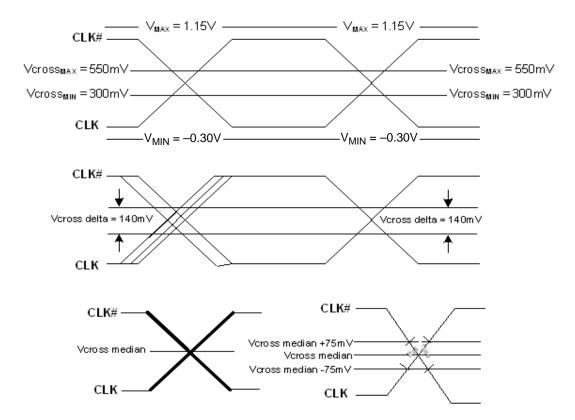

Figure 4. Differential Measurement for Differential Output Signals (for AC Parameters Measurement)

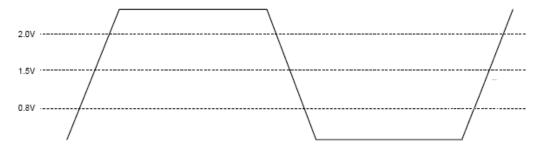

Figure 5. Single-ended Measurement for Differential Output Signals (for AC Parameters Measurement)

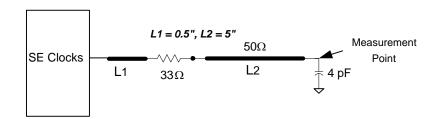

Figure 6. Single-ended Clocks with Single Load Configuration

Figure 7. Single-ended Output Signal (for AC Parameter Measurement)

## 4. Control Registers

## 4.1. I<sup>2</sup>C Interface

To enhance the flexibility and function of the clock synthesizer, an  $I^2C$  interface is provided. Through the  $I^2C$  Interface, various device functions, such as individual clock output buffers are individually enabled or disabled. The registers associated with the  $I^2C$  Interface initialize to their default setting at power-up. The use of this interface is optional. Clock device register changes are normally made at system initialization, if any are required. Power management functions can only be programed in program mode and not in normal operation modes.

#### 4.2. Data Protocol

The clock driver I<sup>2</sup>C protocol accepts byte write, byte read, block write, and block read operations from the controller. For block write/read operation, access the bytes in sequential order from lowest to highest (most significant bit first) with the ability to stop after any complete byte is transferred. For byte write and byte read operations, the system controller can access individually indexed bytes.

The block write and block read protocol is outlined in Table 6 while Table 7 outlines byte write and byte read protocol. The slave receiver address is 11010110 (D6h).

Table 6. Block Read and Block Write Protocol

|       | Block Write Protocol          |       | Block Read Protocol               |

|-------|-------------------------------|-------|-----------------------------------|

| Bit   | Description                   | Bit   | Description                       |

| 1     | Start                         | 1     | Start                             |

| 8:2   | Slave address—7 bits          | 8:2   | Slave address—7 bits              |

| 9     | Write                         | 9     | Write                             |

| 10    | Acknowledge from slave        | 10    | Acknowledge from slave            |

| 18:11 | Command Code—8 bits           | 18:11 | Command Code—8 bits               |

| 19    | Acknowledge from slave        | 19    | Acknowledge from slave            |

| 27:20 | Byte Count—8 bits             | 20    | Repeat start                      |

| 28    | Acknowledge from slave        | 27:21 | Slave address—7 bits              |

| 36:29 | Data byte 1—8 bits            | 28    | Read = 1                          |

| 37    | Acknowledge from slave        | 29    | Acknowledge from slave            |

| 45:38 | Data byte 2—8 bits            | 37:30 | Byte Count from slave—8 bits      |

| 46    | Acknowledge from slave        | 38    | Acknowledge                       |

|       | Data Byte /Slave Acknowledges | 46:39 | Data byte 1 from slave—8 bits     |

|       | Data Byte N—8 bits            | 47    | Acknowledge                       |

|       | Acknowledge from slave        | 55:48 | Data byte 2 from slave—8 bits     |

|       | Stop                          | 56    | Acknowledge                       |

|       |                               |       | Data bytes from slave/Acknowledge |

|       |                               |       | Data Byte N from slave–8 bits     |

|       |                               |       | NOT Acknowledge                   |

|       |                               |       | Stop                              |

Table 7. Byte Read and Byte Write Protocol

|       | Byte Write Protocol    |       | Byte Read Protocol     |

|-------|------------------------|-------|------------------------|

| Bit   | Description            | Bit   | Description            |

| 1     | Start                  | 1     | Start                  |

| 8:2   | Slave address–7 bits   | 8:2   | Slave address–7 bits   |

| 9     | Write                  | 9     | Write                  |

| 10    | Acknowledge from slave | 10    | Acknowledge from slave |

| 18:11 | Command Code–8 bits    | 18:11 | Command Code–8 bits    |

| 19    | Acknowledge from slave | 19    | Acknowledge from slave |

| 27:20 | Data byte–8 bits       | 20    | Repeated start         |

| 28    | Acknowledge from slave | 27:21 | Slave address–7 bits   |

| 29    | Stop                   | 28    | Read                   |

|       |                        | 29    | Acknowledge from slave |

|       |                        | 37:30 | Data from slave–8 bits |

|       |                        | 38    | NOT Acknowledge        |

|       |                        | 39    | Stop                   |

## Control Register 0. Byte 0

| Bit  | D7  | D6  | D5  | D4  | D3  | D2     | D1  | D0  |

|------|-----|-----|-----|-----|-----|--------|-----|-----|

| Name |     |     |     |     |     | REF_OE |     |     |

| Туре | R/W | R/W | R/W | R/W | R/W | R/W    | R/W | R/W |

Reset settings = 00000100

| Bit | Name     | Function                                                        |  |  |  |

|-----|----------|-----------------------------------------------------------------|--|--|--|

| 7:3 | Reserved |                                                                 |  |  |  |

| 2   | REF_OE   | Output Enable for REF.  0: Output disabled.  1: Output enabled. |  |  |  |

| 1:0 | Reserved |                                                                 |  |  |  |

## Control Register 1. Byte 1

| Bit  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name |     |     |     |     |     |     |     |     |

| Туре | R/W |

Reset settings = 00000000

| Bit | Name     | Function |

|-----|----------|----------|

| 7:0 | Reserved |          |

## Control Register 2. Byte 2

| Bit  | D7       | D6       | D5  | D4  | D3  | D2  | D1  | D0  |

|------|----------|----------|-----|-----|-----|-----|-----|-----|

| Name | DIFF0_OE | DIFF1_OE |     |     |     |     |     |     |

| Туре | R/W      | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |

Reset settings = 11000000

| Bit | Name     | Function                                |  |  |

|-----|----------|-----------------------------------------|--|--|

| 7   | DIFF0_OE | Output Enable for DIFF0.                |  |  |

|     |          | 0: Output disabled.  1: Output enabled. |  |  |

| 6   | DIFF1_OE | Output Enable for DIFF1.                |  |  |

|     |          | 0: Output disabled.  1: Output enabled. |  |  |

| 5:0 | Reserved |                                         |  |  |

## Control Register 3. Byte 3

| Bit  | D7            | D6 | D5  | D4  | D3             | D2  | D1  | D0 |

|------|---------------|----|-----|-----|----------------|-----|-----|----|

| Name | Rev Code[3:0] |    |     |     | Vendor ID[3:0] |     |     |    |

| Туре | R/W R/W R/W   |    | R/W | R/W | R/W            | R/W | R/W |    |

Reset settings = 00001000

| Bit | Name           | Function                    |  |

|-----|----------------|-----------------------------|--|

| 7:4 | Rev Code[3:0]  | Program Revision Code.      |  |

| 3:0 | Vendor ID[3:0] | Vendor Identification Code. |  |

## Control Register 4. Byte 4

| Bit  | D7      | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|------|---------|-----|-----|-----|-----|-----|-----|-----|

| Name | BC[7:0] |     |     |     |     |     |     |     |

| Туре | R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

Reset settings = 00000110

| Bit | Name    | Function             |  |

|-----|---------|----------------------|--|

| 7:0 | BC[7:0] | Byte Count Register. |  |

## Control Register 5. Byte 5

| Bit  | D7           | D6               | D5               | D4               | D3  | D2  | D1  | D0  |

|------|--------------|------------------|------------------|------------------|-----|-----|-----|-----|

| Name | DIFF_Amp_Sel | DIFF_Amp_Cntl[2] | DIFF_Amp_Cntl[1] | DIFF_Amp_Cntl[0] |     |     |     |     |

| Туре | R/W          | R/W              | R/W              | R/W              | R/W | R/W | R/W | R/W |

Reset settings = 11011000

| Bit | Name             | Function                                                                                                                                                    |  |  |  |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | DIFF_Amp_Sel     | Amplitude Control for DIFF Differential Outputs.  0: Differential outputs with Default amplitude.  1: Differential outputs amplitude is set by Byte 5[6:4]. |  |  |  |

| 6   | DIFF_Amp_Cntl[2] | DIFF Differential Outputs Amplitude Adjustment.                                                                                                             |  |  |  |

| 5   | DIFF_Amp_Cntl[1] | 000: 300 mV 001: 400 mV 010: 500 mV 011: 600 mV                                                                                                             |  |  |  |

| 4   | DIFF_Amp_Cntl[0] | 100: 700 mV 101: 800 mV 110: 900 mV 111: 1000 mV                                                                                                            |  |  |  |

| 3:0 | Reserved         |                                                                                                                                                             |  |  |  |

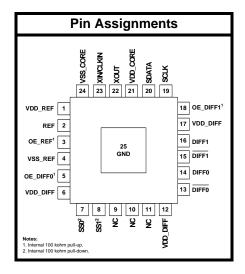

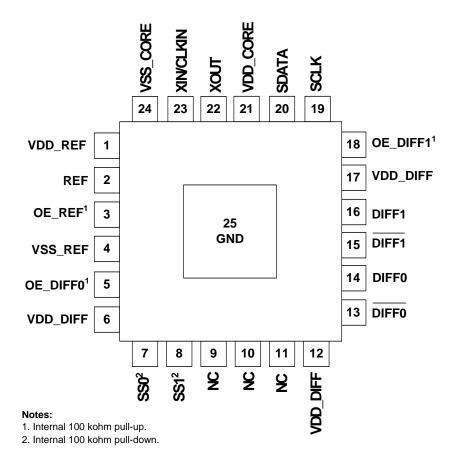

## 5. Pin Descriptions: 24-Pin QFN

Table 8. Si52142 24-Pin QFN Descriptions

| Pin# | Name     | Туре  | Description                                                                                                                                   |

|------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VDD_REF  | PWR   | 3.3 V power supply.                                                                                                                           |

| 2    | REF      | O, SE | 3.3 V, 25 MHz crystal reference clock.                                                                                                        |

| 3    | OE_REF   | I,PU  | Active high input pin to enable or disable REF clock (internal 100 $\mbox{k}\Omega$ pull-up).                                                 |

| 4    | VSS_REF  | GND   | Ground.                                                                                                                                       |

| 5    | OE_DIFF0 | I,PU  | Active high input pin to enable or disable DIFF0 clock (internal 100 $\mbox{k}\Omega$ pull-up).                                               |

| 6    | VDD_DIFF | PWR   | 3.3 V power supply.                                                                                                                           |

| 7    | SS0      | I, PD | 3.3 V tolerant latch-input for enabling Frequency/ Spread selection on DIFF0 and DIFF1 outputs. Refer to Table 1 on page 4 for SS[1:0] speci- |

| 8    | SS1      | I, PD | fications (internal 100 k $\Omega$ pull-down).                                                                                                |

| 9    | NC       | NC    | No Connect.                                                                                                                                   |

| 10   | NC       | NC    | No connect.                                                                                                                                   |

Table 8. Si52142 24-Pin QFN Descriptions (Continued)

| Pin# | Name      | Туре   | Description                                                                                     |

|------|-----------|--------|-------------------------------------------------------------------------------------------------|

| 11   | NC        | NC     | No connect.                                                                                     |

| 12   | VDD_DIFF  | PWR    | 3.3 V power supply.                                                                             |

| 13   | DIFF0     | O, DIF | 0.7 V, 100 MHz differential clock.                                                              |

| 14   | DIFF0     | O, DIF | 0.7 V, 100 MHz differential clock.                                                              |

| 15   | DIFF1     | O, DIF | 0.7 V, 100 MHz differential clock.                                                              |

| 16   | DIFF1     | O, DIF | 0.7 V, 100 MHz differential clock.                                                              |

| 17   | VDD_DIFF  | PWR    | 3.3 V power supply.                                                                             |

| 18   | OE_DIFF1  | I,PU   | Active high input pin to enable or disable DIFF1 clock (internal 100 $\mbox{k}\Omega$ pull-up). |

| 19   | SCLK      | I      | I <sup>2</sup> C SCLOCK.                                                                        |

| 20   | SDATA     | I/O    | I <sup>2</sup> C SDATA.                                                                         |

| 21   | VDD_CORE  | PWR    | 3.3 V power supply.                                                                             |

| 22   | XOUT      | 0      | 25.00 MHz Crystal output, Float XOUT if using only CLKIN (Clock input).                         |

| 23   | XIN/CLKIN | I      | 25.00 MHz Crystal input or 3.3 V, 25 MHz Clock Input.                                           |

| 24   | VSS_CORE  | GND    | Ground.                                                                                         |

| 25   | GND       | GND    | Ground for bottom pad of the IC.                                                                |

# 6. Ordering Guide

| Part Number     | Package Type             | Temperature            |

|-----------------|--------------------------|------------------------|

| Lead-free       |                          |                        |

| Si52142-A01AGM  | 24-pin QFN               | Extended, -40 to 85 °C |

| Si52142-A01AGMR | 24-pin QFN—Tape and Reel | Extended, -40 to 85 °C |

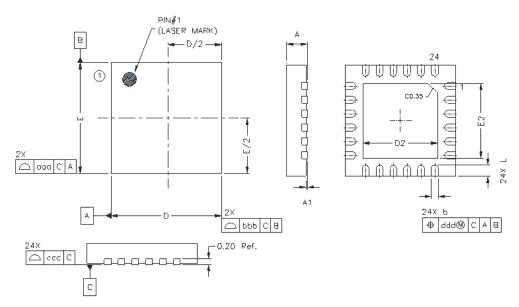

## 7. Package Outline

Figure 8 illustrates the package details for the Si52142. Table 9 lists the values for the dimensions shown in the illustration.

Figure 8. 24-Pin Quad Flat No Lead (QFN) Package

| rackage | Diagram | Dimensions      | Š                          |

|---------|---------|-----------------|----------------------------|

|         |         |                 |                            |

|         | rackage | rackage Diagram | Package Diagram Dimensions |

| Symbol | Millimeters |       |      |

|--------|-------------|-------|------|

|        | Min         | Nom   | Max  |

| А      | 0.70        | 0.75  | 0.80 |

| A1     | 0.00        | 0.025 | 0.05 |

| b      | 0.20        | 0.25  | 0.30 |

| D      | 4.00 BSC    |       |      |

| D2     | 2.60        | 2.70  | 2.80 |

| е      | 0.50 BSC    |       |      |

| E      | 4.00 BSC    |       |      |

| E2     | 2.60        | 2.70  | 2.80 |

| L      | 0.30        | 0.40  | 0.50 |

| aaa    | 0.10        |       |      |

| bbb    | 0.10        |       |      |

| ccc    | 0.08        |       |      |

| ddd    | 0.07        |       |      |

#### Notes:

- All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-220, variation VGGD-8.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## **DOCUMENT CHANGE LIST**

## **Revision 0.1 to Revision 1.0**

- Updated Features on page 1.

- Updated Description on page 1.

- Updated Table 1 on page 4.

- Updated Table 2 on page 5.

- Updated Section 2.1 on page 7.

- Updated Section 2.1.1 on page 7.

- Updated Section 4.1 on page 11.

- Updated Section 4.2 on page 11.

- Updated Pin Descriptions on page 16.

#### **Revision 1.0 to Revision 1.1**

Removed Moisture Sensitivity Level specification from Table 3.

Notes:

## Si52142

### **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

#### **Patent Notice**

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analog-intensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.