**Sound Processor Series for Car Audio**

# Sound Processors with Built-in 2-band Equalizer

BD37511FS,BD37512FS

No.10085EAT10

#### Description

BD37511FS, BD37512FS are sound processors built-in 2-band equalizer for car audio. The functions are stereo 4ch input selector(About BD37511FS, 3ch input selector are available), input-gain control, main volume, 4ch fader volume. Moreover, "Advanced switch circuit", that is ROHM original technology, can reduce various switching noise (ex. No-signal, low frequency likes 20Hz & large signal inputs). "Advanced switch" makes control of microcomputer easier, and can construct high quality car audio system.

#### Features

- 1) Reduce switching noise of mute, main volume, fader volume, bass, trebles by using advanced switch circuit [Possible to control all steps]

- 2) Built-in 1 differential input selector(BD37512FS) and 3 single-ended input selectors.

- 3) Built-in ground isolation amplifier inputs, ideal for external stereo input. (BD37512FS)

- 4) Decrease the number of external components by built-in 2-band equalizer filter.

- 5) It is possible for the bass, treble to the gain adjustment quantity of ±20dB and 1 dB step gain adjustment.

- 6) Bi-CMOS process is suitable for the design of low current and low energy. And it provides more quality for small scale regulator and heat in a set.

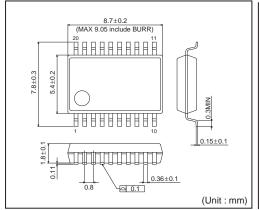

- 7) Package is SSOP-A20. Putting input-terminals together and output-terminals together can make PCB layout easier and can makes area of PCB smaller.

- 8) It is possible to control by 3.3V / 5V for I<sup>2</sup>C BUS.

#### Applications

It is the optimal for the car audio. Besides, it is possible to use for the audio equipment of mini Compo, micro Compo, TV etc with all kinds.

# ●Line up matrix

| Function       | BD37511FS | BD37512FS | Specifications                                                                           |

|----------------|-----------|-----------|------------------------------------------------------------------------------------------|

| lanut aalaatan | 0         | 0         | Stereo 3 input                                                                           |

| Input selector | ×         | 0         | Differential 1 input                                                                     |

| Input gain     | 0         | 0         | · 0~20dB                                                                                 |

| Mute           | 0         | 0         | Possible to use "Advanced switch" for prevention of switching noise.                     |

| Valuma         | 0         | 0         | · 0dB~-40dB (1dB step)                                                                   |

| Volume         | O         | O         | <ul> <li>Possible to use "Advanced switch" for prevention of switching noise.</li> </ul> |

|                |           |           | · -20~+20dB (1dB step)                                                                   |

| Bass           | 0         | 0         | • Q=1                                                                                    |

| Dass           | O         |           | • fo=100Hz                                                                               |

|                |           |           | <ul> <li>Possible to use advanced switch at changing gain</li> </ul>                     |

|                |           |           | · -20~+20dB (1dB step)                                                                   |

| Treble         | 0         | 0         | • Q=1                                                                                    |

| Hebie          | O         | O         | · fo=10kHz                                                                               |

|                |           |           | Possible to use advanced switch at changing gain                                         |

| Fader          | )         | 0         | • 0dB~-62dB(1dB step), -∞dB                                                              |

| rauei          | O         | O         | <ul> <li>Possible to use "Advanced switch" for prevention of switching noise.</li> </ul> |

# ● Absolute maximum ratings (Ta=25°C)

| Item                 | Symbol | Rating            | Unit |

|----------------------|--------|-------------------|------|

| Power supply Voltage | VCC    | 10.0              | V    |

| Input voltage        | Vin    | VCC+0.3∼GND-0.3   | V    |

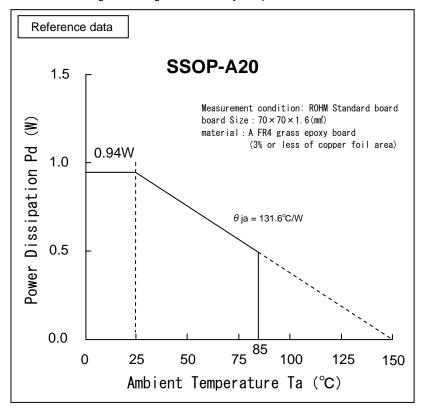

| Power Dissipation    | Pd     | 940 ※1            | mW   |

| Storage Temperature  | Tastg  | -55 <b>~</b> +150 | °C   |

<sup>\*</sup>This value decreases 7.5mW/°C for Ta=25°C or more.

ROHM standard board shall be mounted.

Thermal resistance  $\theta$ ja = 133(°C/W)

ROHM Standard board Size: 70×70×1.6(mm³)

Material: A FR4 grass epoxy board(3% or less of copper foil area)

# Operating conditions

| Item                 | Symbol | MIN | TYP | MAX | Unit |

|----------------------|--------|-----|-----|-----|------|

| Power supply Voltage | VCC    | 7.0 | _   | 9.5 | V    |

| Temperature          | Topr   | -40 | _   | +85 | °C   |

# • Electrical characteristics

(Unless specified particularly, Ta=25°C, VCC=8.5V, f=1kHz, Vin=1Vrms, Rg=600 $\Omega$ , R<sub>L</sub>=10k $\Omega$ , A input, Input gain 0dB, Mute off Volume 0dB. Tone control 0dB, Laudness 0dB, Fader 0dB)

| Mu        | Mute off, Volume 0dB, Tone control 0dB, Loudness 0dB, Fader 0dB) |                     |      |       |      |       |                                                                   |  |  |  |  |  |

|-----------|------------------------------------------------------------------|---------------------|------|-------|------|-------|-------------------------------------------------------------------|--|--|--|--|--|

| BLOCK     | Item                                                             | Symbol              |      | Limit |      | Unit  | Condition                                                         |  |  |  |  |  |

| BL(       | item                                                             | Symbol              | Min. | Тур.  | Max. | Offic | Condition                                                         |  |  |  |  |  |

|           | Current upon no signal                                           | ΙQ                  | _    | 15    | 30   | mA    | No signal                                                         |  |  |  |  |  |

|           | Voltage gain                                                     | G∨                  | -1.5 | 0     | 1.5  | dB    | Gv=20log(VOUT/VIN)                                                |  |  |  |  |  |

|           | Channel balance                                                  | CB                  | -1.5 | 0     | 1.5  | dB    | CB = GV1-GV2                                                      |  |  |  |  |  |

|           | Total harmonic distortion                                        | THD+N1              | 1    | 0.005 | 0.05 | %     | VOUT=1Vrms<br>BW=400-30KHz                                        |  |  |  |  |  |

|           | Output noise voltage *                                           | V <sub>NO1</sub>    | ı    | 6     | 25   | μVrms | $Rg = 0\Omega$<br>BW = IHF-A                                      |  |  |  |  |  |

| GENERAL   | Residual output noise voltage *                                  | V <sub>NOR</sub>    | -    | 2     | 10   | μVrms | Fader = -∞dB<br>Rg = 0Ω<br>BW = IHF-A                             |  |  |  |  |  |

|           | Cross-talk between channels *                                    | СТС                 | ı    | -100  | -90  | dB    | $Rg = 0\Omega$<br>CTC=20log(VOUT/VIN)<br>BW = IHF-A               |  |  |  |  |  |

|           | Ripple rejection                                                 | RR                  | -    | -70   | -40  | dB    | f=1kHz<br>VRR=100mVrms<br>RR=20log(VCC IN/VOUT)                   |  |  |  |  |  |

|           | Input impedance(A, B, C)                                         | R <sub>IN_S</sub>   | 70   | 100   | 130  | kΩ    |                                                                   |  |  |  |  |  |

|           | Input impedance (D) (BD37512FS)                                  | R <sub>IN_D</sub>   | 35   | 50    | 65   | kΩ    |                                                                   |  |  |  |  |  |

| SELECTOR  | Maximum input voltage                                            | V <sub>IM</sub>     | 2.1  | 2.3   | _    | Vrms  | VIM at THD+N(VOUT)=1%<br>BW=400-30KHz                             |  |  |  |  |  |

| NPUT SELE | Cross-talk between selectors *                                   | CTS                 | -    | -100  | -90  | dB    | Rg = 0Ω<br>CTS=20log(VOUT/VIN)<br>BW = IHF-A                      |  |  |  |  |  |

| - INP     | Common mode rejection ratio * (BD37512FS)                        | CMRR                | 50   | 65    | _    | dB    | DP1 and DN input DP2 and DN input CMRR=20log(VIN/VOUT) BW = IHF-A |  |  |  |  |  |

| GAIN      | Minimum input gain                                               | G <sub>IN MIN</sub> | -2   | 0     | +2   | dB    | Input gain 0dB<br>VIN=100mVrms<br>Gin=20log(VOUT/VIN)             |  |  |  |  |  |

| INPUT G   | Maximum input gain                                               | G <sub>IN MAX</sub> | 18   | 20    | 22   | dB    | Input gain 20dB<br>VIN=100mVrms<br>Gin=20log(VOUT/VIN)            |  |  |  |  |  |

|           | Gain set error                                                   | G <sub>IN ERR</sub> | -2   | 0     | +2   | dB    | GAIN=+1~+20dB                                                     |  |  |  |  |  |

| 충      |                         | 0 1 1               |      | Limit |      | 11.74 | 0 10                                                                   |

|--------|-------------------------|---------------------|------|-------|------|-------|------------------------------------------------------------------------|

| BLOCK  | Item                    | Symbol              | Min. | Тур.  | Max. | Unit  | Condition                                                              |

| MUTE   | Mute attenuation *      | G <sub>MUTE</sub>   | 1    | -105  | -85  | dB    | Mute ON Gmute=20log(VOUT/VIN) BW = IHF-A                               |

| VOLUME | Maximum attenuation     | G∨ MIN              | -43  | -40   | -37  | dB    | Volume = -40dB<br>Gv=20log(VOUT/VIN)                                   |

| 9      | Attenuation set error 1 | G <sub>V ERR1</sub> | -2   | 0     | 2    | dB    | GAIN & ATT=0dB~-15dB                                                   |

| _      | Attenuation set error 2 | G <sub>V ERR2</sub> | -3   | 0     | 3    | dB    | ATT=-16dB~-40dB                                                        |

|        | Maximum boost gain      | G <sub>B BST</sub>  | 18   | 20    | 22   | dB    | Gain=+20dB f=100Hz<br>VIN=100mVrms<br>G <sub>B</sub> =20log (VOUT/VIN) |

| BASS   | Maximum cut gain        | G <sub>B CUT</sub>  | -22  | -20   | -18  | dB    | Gain=-20dB f=100Hz<br>VIN=2Vrms<br>G <sub>B</sub> =20log (VOUT/VIN)    |

|        | Gain set error          | G <sub>B ERR</sub>  | -2   | 0     | 2    | dB    | Gain=-20~+20dB f=100Hz                                                 |

|        | Maximum boost gain      | G <sub>T BST</sub>  | 18   | 20    | 22   | dB    | Gain=+20dB f=10kHz<br>VIN=100mVrms<br>G <sub>T</sub> =20log (VOUT/VIN) |

| TREBLE | Maximum cut gain        | G <sub>т сит</sub>  | -22  | -20   | -18  | dB    | Gain=-20dB f=10kHz<br>VIN=2Vrms<br>G <sub>T</sub> =20log (VOUT/VIN)    |

|        | Gain set error          | G <sub>T ERR</sub>  | -2   | 0     | 2    | dB    | Gain=-20~+20dB<br>f=10kHz                                              |

|        | Maximum attenuation *   | G <sub>F MIN</sub>  | ı    | -100  | -90  | dB    | $Fader = -\infty dB$ $G_F=20log(VOUT/VIN)$ $BW = IHF-A$                |

|        | Attenuation set error 1 | G <sub>F ERR1</sub> | -2   | 0     | 2    | dB    | ATT=0∼-15dB                                                            |

| FADER  | Attenuation set error 2 | G <sub>F ERR2</sub> | -3   | 0     | 3    | dB    | ATT=-16~-47dB                                                          |

| FA     | Attenuation set error 3 | G <sub>F ERR3</sub> | -4   | 0     | 4    | dB    | ATT=-48~-62dB                                                          |

|        | Output impedance        | R <sub>OUT</sub>    | -    | _     | 50   | Ω     | VIN=100mVrms                                                           |

|        | Maximum output voltage  | V <sub>OM</sub>     | 2    | 2.2   | _    | Vrms  | THD+N=1%<br>BW=400-30KHz                                               |

VP-9690A(Average value detection, effective value display) filter by Matsushita Communication is used for \* measurement. Phase between input / output is same.

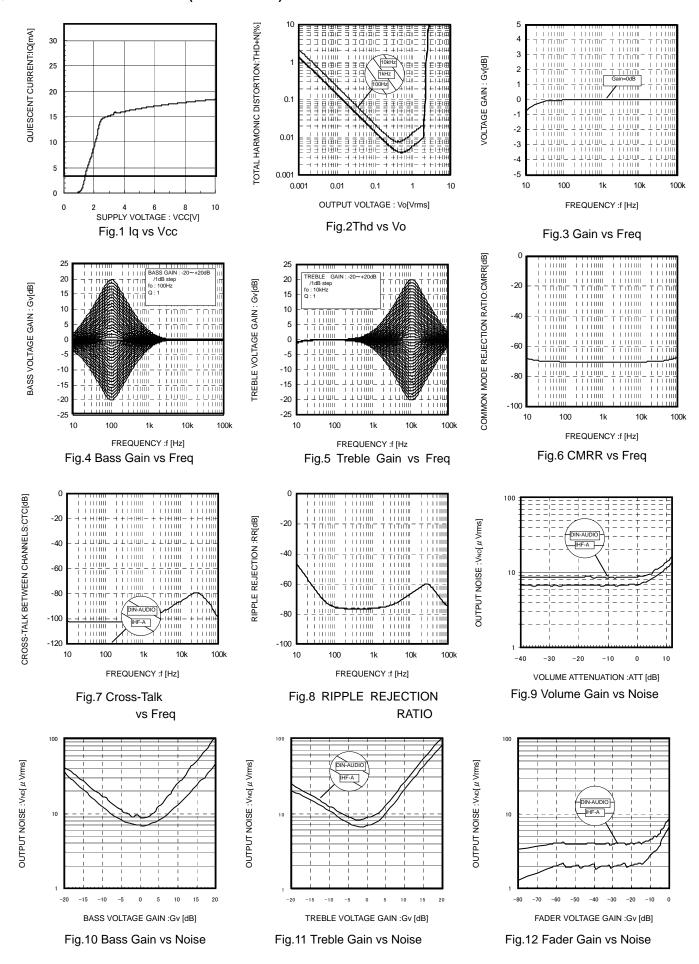

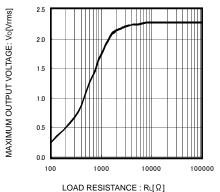

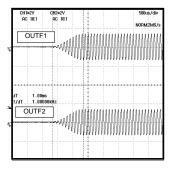

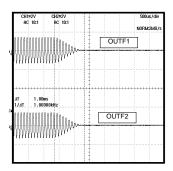

#### Electrical characteristic curves (Reference data)

Fig.13 Rload vs Vo Fig.14Advanced Switch 1

Fig. 15 Advanced Switch 2

# Block diagram and pin configuration

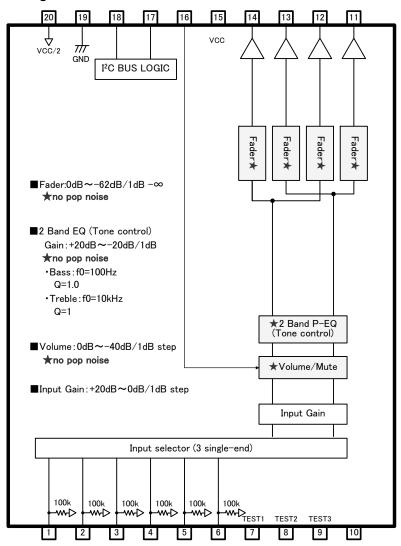

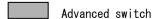

Fig. 16 BD37511FS

# **Descriptions of terminal**

| Description     | S OF LEFTINITIE  | 21                      |                 |                  |                                               |

|-----------------|------------------|-------------------------|-----------------|------------------|-----------------------------------------------|

| Terminal<br>No. | Terminal<br>Name | Description             | Terminal<br>No. | Terminal<br>Name | Description                                   |

| 1               | A1               | A input terminal of 1ch | 11              | OUTR2            | Rear output terminal of 2ch                   |

| 2               | A2               | A input terminal of 2ch | 12              | OUTR1            | Rear output terminal of 1ch                   |

| 3               | B1               | B input terminal of 1ch | 13              | 0UTF2            | Front output terminal of 2ch                  |

| 4               | B2               | B input terminal of 2ch | 14              | 0UTF1            | Front output terminal of 1ch                  |

| 5               | C1               | C input terminal of 1ch | 15              | VCC              | Power supply terminal                         |

| 6               | C2               | C input terminal of 2ch | 16              | MUTE             | External compulsory mute terminal             |

| 7               | TEST1            | Test Pin                | 17              | SCL              | I <sup>2</sup> C Communication clock terminal |

| 8               | TEST2            | Test Pin                | 18              | SDA              | I <sup>2</sup> C Communication data terminal  |

| 9               | TEST3            | Test Pin                | 19              | GND              | GND terminal                                  |

| 10              | N. C.            | No Connection           | 20              | FIL              | VCC/2 terminal                                |

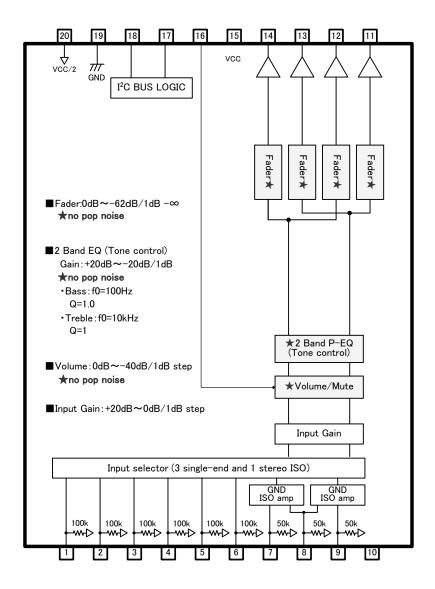

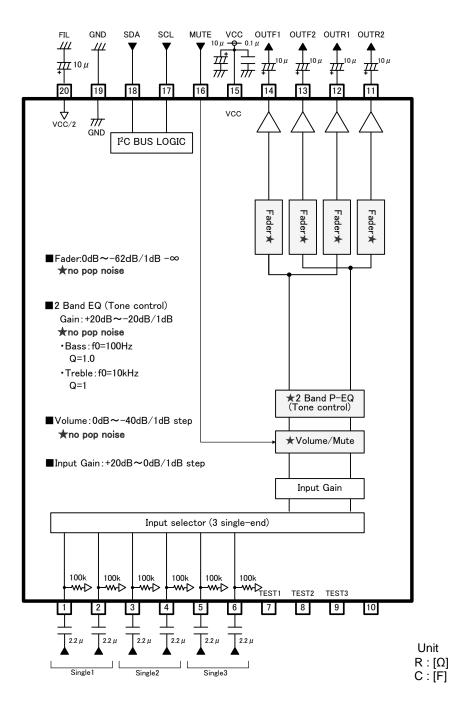

Fig.17 BD37512FS

**Descriptions of terminal**

| Descriptions of terminal |                  |                                  |                 |                  |                                               |  |  |  |  |  |  |

|--------------------------|------------------|----------------------------------|-----------------|------------------|-----------------------------------------------|--|--|--|--|--|--|

| Terminal<br>No.          | Terminal<br>Name | Description                      | Terminal<br>No. | Terminal<br>Name | Description                                   |  |  |  |  |  |  |

| 1                        | <b>A</b> 1       | A input terminal of 1ch          | 11              | OUTR2            | Rear output terminal of 2ch                   |  |  |  |  |  |  |

| 2                        | A2               | A input terminal of 2ch          | 12              | OUTR1            | Rear output terminal of 1ch                   |  |  |  |  |  |  |

| 3                        | B1               | B input terminal of 1ch          | 13              | 0UTF2            | Front output terminal of 2ch                  |  |  |  |  |  |  |

| 4                        | B2               | B input terminal of 2ch          | 14              | 0UTF1            | Front output terminal of 1ch                  |  |  |  |  |  |  |

| 5                        | C1               | C input terminal of 1ch          | 15              | VCC              | Power supply terminal                         |  |  |  |  |  |  |

| 6                        | C2               | C input terminal of 2ch          | 16              | MUTE             | External compulsory mute terminal             |  |  |  |  |  |  |

| 7                        | DP1              | D positive input terminal of 1ch | 17              | SCL              | I <sup>2</sup> C Communication clock terminal |  |  |  |  |  |  |

| 8                        | DN               | D negative input terminal        | 18              | SDA              | I <sup>2</sup> C Communication data terminal  |  |  |  |  |  |  |

| 9                        | DP2              | D positive input terminal of 2ch | 19              | GND              | GND terminal                                  |  |  |  |  |  |  |

| 10                       | N. C.            | No Connection                    | 20              | FIL              | VCC/2 terminal                                |  |  |  |  |  |  |

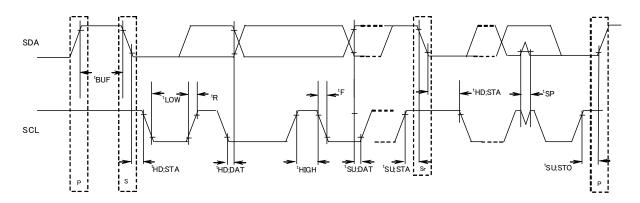

# **●Timming Chart**

# CONTROL SIGNAL SPECIFICATION

# (1) Electrical specifications and timing for bus lines and I/O stages

Fig.18 Definition of timing on the I<sup>2</sup>C-bus

Table 1 Characteristics of the SDA and SCL bus lines for I<sup>2</sup>C-bus devices

|   | Parameter                                                                                   | Cumbal  | Fast-mod | Unit |      |

|---|---------------------------------------------------------------------------------------------|---------|----------|------|------|

|   | Parameter                                                                                   | Symbol  | Min.     | Max. | Unit |

| 1 | SCL clock frequency                                                                         | f SCL   | 0        | 400  | kHz  |

| 2 | Bus free time between a STOP and START condition                                            | tBUF    | 1.3      | _    | μS   |

| 3 | Hold time (repeated) START condition. After this period, the first clock pulse is generated | tHD;STA | 0.6      | _    | μS   |

| 4 | LOW period of the SCL clock                                                                 | tLOW    | 1.3      | _    | μS   |

| 5 | HIGH period of the SCL clock                                                                | tHIGH   | 0.6      | _    | μS   |

| 6 | Set-up time for a repeated START condition                                                  | tSU;STA | 0.6      | _    | μS   |

| 7 | Data hold time:                                                                             | tHD;DAT | 0.7*     | _    | μS   |

| 8 | Data set-up time                                                                            | tSU;DAT | 700      | _    | ns   |

| 9 | Set-up time for STOP condition                                                              | tSU;STO | 0.6      | _    | μS   |

All values referred to VIH min. and VIL max. Levels (see Table 2).

<sup>\*</sup> A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the VIH min. of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

About 7(tHD;DAT), 8(tSU;DAT), make it the setup which a margin is fully in .

Table 2 Characteristics of the SDA and SCL I/O stages for I<sup>2</sup>C-bus devices

|    | Parameter                                                               | Cumbal | Fast-mode | Unit |       |

|----|-------------------------------------------------------------------------|--------|-----------|------|-------|

|    | Parameter                                                               | Symbol | Min.      | Max. | Offic |

| 10 | LOW level input voltage:                                                | VIL    | -0.3      | 1    | V     |

| 11 | HIGH level input voltage:                                               | VIH    | 2.3       | 5    | V     |

| 12 | Pulse width of spikes which must be suppressed by the input filter.     | tSP    | 0         | 50   | ns    |

| 13 | LOW level output voltage: at 3mA sink current                           | VOL1   | 0         | 0.4  | V     |

| 14 | Input current each I/O pin with an input voltage between 0.4V and 4.5V. | li     | -10       | 10   | μA    |

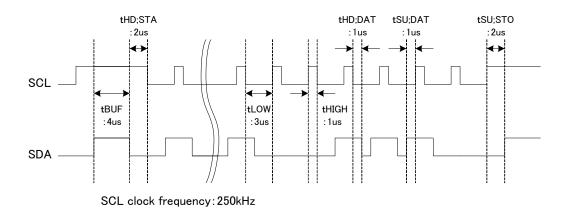

Fig.19 A command timing example in the I2C data transmission

# (2) I<sup>2</sup>C BUS FORMAT

|   |                                                  | MSB LSB                                                                          | MSB LS |            | LSB         | MSB   |                    | LSB             |      |         |   |

|---|--------------------------------------------------|----------------------------------------------------------------------------------|--------|------------|-------------|-------|--------------------|-----------------|------|---------|---|

|   | S                                                | Slave Address                                                                    | Α      | Select     | Address     | Α     |                    | Data            | Α    | Р       |   |

| 1 | bit                                              | 8bit                                                                             | 1bit 8 |            | 8bit        | 1bit  |                    | 8bit            | 1bit | 1bit    | • |

|   |                                                  | S                                                                                | = St   | art condit | ions (Reco  | gniti | on of a            | start bit)      |      |         |   |

|   |                                                  | Slave Address = Recognition of slave address. 7 bits in upper order are voluntar |        |            |             |       |                    |                 |      | untary. |   |

|   | The least significant bit is "L" due to writing. |                                                                                  |        |            |             |       |                    |                 |      |         |   |

|   |                                                  | Α                                                                                | = AC   | KNOWLEDGE  | bit (Recogn | nitio | n of a             | cknowledgement) |      |         |   |

|   |                                                  | Select Address                                                                   | = Se   | lect every | of volume,  | bas   | s and <sup>-</sup> | treble.         |      |         |   |

|   |                                                  | Data = Data on every volume and tone.                                            |        |            |             |       |                    |                 |      |         |   |

|   |                                                  | Р                                                                                |        |            |             |       |                    |                 |      |         |   |

# (3) I<sup>2</sup>C BUS Interface Protocol

1) Basic form

| S | SI  | ave Address | Α | Select | A Data |    |    | Α   | Р |  |  |

|---|-----|-------------|---|--------|--------|----|----|-----|---|--|--|

|   | MSB | LSB         |   | MSB    | LSB    | MS | SB | LSB |   |  |  |

2) Automatic increment (Select Address increases (+1) according to the number of data.)

| S | Slave Address | Α | Select Address | Α | Data1   | Α | Data2   | Α |   | DataN  | Α | Р |

|---|---------------|---|----------------|---|---------|---|---------|---|---|--------|---|---|

|   | MSB LSB       | M | SB LSB         | M | ISB LSB |   | MSB LSB |   | М | SB LSB |   |   |

(Example) ①Data1 shall be set as data of address specified by Select Address.

②Data2 shall be set as data of address specified by Select Address +1.

3DataN shall be set as data of address specified by Select Address +N-1.

3) Configuration unavailable for transmission (In this case, only Select Address1 is set.)

| S | Slave | Address | Α     | Select     | Address1    | Α   | Data     | Α    | Select    | Address 2  | Α  | Dat   | ta  | Α  | Р |

|---|-------|---------|-------|------------|-------------|-----|----------|------|-----------|------------|----|-------|-----|----|---|

|   | MSB   | L;      | SB    | MSB        | LSB         | M   | SB LSB   |      | MSB       | LSB        | M  | ISB   | LSB |    |   |

|   |       | (1      | lote) | ) If any ( | data is tra | nsm | itted as | Sel  | ect Addr  | ess 2 next | to | data, | it  | is |   |

|   |       |         |       | recogn     | ized as dat | a,  | not as S | eled | ct Addres | ss 2.      |    |       |     |    |   |

### (4) Slave address

| MSB |    |    | LSB |    |            |    |     |     |

|-----|----|----|-----|----|------------|----|-----|-----|

| A6  | A5 | A4 | A3  | A2 | <b>A</b> 1 | A0 | R/W |     |

| 1   | 0  | 0  | 0   | 0  | 0          | 0  | 0   | 80H |

# (5) Select Address & Data

| 14              | Select           | MSB                          |    |                    | Da                            | ata      |           |                   | LSB                |

|-----------------|------------------|------------------------------|----|--------------------|-------------------------------|----------|-----------|-------------------|--------------------|

| Items           | Address<br>(hex) | D7                           | D6 | D5                 | D4                            | D3       | D2        | D1                | D0                 |

| Initial setup 1 | 01               | Advanced<br>switch<br>ON/OFF | 0  | time               | d switch<br>e of<br>one/Fader | 0        | 0         | Advance<br>time o | d switch<br>f Mute |

| Input Selector  | 04               | 0                            | 0  | 0                  | 0                             | 0        | In        | put select        | or                 |

| Input gain      | 06               | Mute<br>ON/OFF               | 0  | 0 Input Gain       |                               |          |           |                   |                    |

| Volume gain     | 20               | 1                            | 0  | Volume Attenuation |                               |          |           |                   |                    |

| Fader 1ch Front | 28               | 1                            | 0  |                    |                               | Fader At | tenuation |                   |                    |

| Fader 2ch Front | 29               | 1                            | 0  |                    |                               | Fader At | tenuation |                   |                    |

| Fader 1ch Rear  | 2A               | 1                            | 0  |                    |                               | Fader At | tenuation |                   |                    |

| Fader 2ch Rear  | 2B               | 1                            | 0  |                    |                               | Fader At | tenuation |                   |                    |

| Bass gain       | 51               | Bass<br>Boost/<br>Cut        | 0  | 0                  |                               |          | Bass Gain |                   |                    |

| Treble gain     | 57               | Treble<br>Boost/<br>Cut      | 0  | O Treble Gain      |                               |          |           |                   |                    |

| System Reset    | FE               | 1                            | 0  | 0 0 0 0 0 1        |                               |          |           |                   |                    |

#### Note

- 1. In function changing of the hatching part, it works Advanced switch.

- 2. When changing a tone into the cut from the boost, or the cut and the boost, always go via the condition of the tone 0dB.

- 3. Upon continuous data transfer, the Select Address is circulated by the automatic increment function, as shown below.

- 4. For the function of input selector etc, it is not corresponded for advanced switch. Therefore, please apply mute on the side of a set when changes these setting.

- 5. When using mute function of this IC at the time of changing input selector, please switch mute ON/OFF for waiting advanced-mute time.

#### Select address 01 (hex)

| Mode     | MSB                | Ad۱ | /anced      | swite | ch tim | e of N | Mute | LSB |

|----------|--------------------|-----|-------------|-------|--------|--------|------|-----|

| Wode     | D7                 | D6  | D5          | D4    | D3     | D2     | D1   | D0  |

| 0.6msec  | Advanced           |     |             |       |        |        | 0    | 0   |

| 1.2msec  | Advanced<br>Switch | 0   | Advanced sw |       | 0      | 0      | 0    | 1   |

| 2. 4msec | ON/OFF             | U   | of Volume/  |       |        | 0      | 1    | 0   |

| 4.8msec  | ON/ OFF            |     |             |       |        |        | 1    | 1   |

| Mode      | MSB                |    |    | nced so |    |    | of      | LSB      |

|-----------|--------------------|----|----|---------|----|----|---------|----------|

|           | D7                 | D6 | D5 | D4      | D3 | D2 | D1      | D0       |

| 4.6 msec  | Advanced           |    | 0  | 0       | 0  | 0  |         |          |

| 9.3 msec  | Advanced<br>Switch | 0  | 0  | 1       |    |    | Advance | d switch |

| 18.6 msec | ON/OFF             |    | 1  | 0       |    | U  | Time o  | of Mute  |

| 37.2 msec | ON/OIT             |    | 1  | 1       |    |    |         |          |

| Mode | MSB | SB Advanced switch ON/OFF |                      |            |    |    |         |          |  |  |

|------|-----|---------------------------|----------------------|------------|----|----|---------|----------|--|--|

| Mode | D7  | D6                        | D5                   | D4         | D3 | D2 | D1      | D0       |  |  |

| 0FF  | 0   | 0                         | Advanced switch time |            | 0  | 0  | Advance | d switch |  |  |

| ON   | 1   | U                         | of Volume/           | Tone/Fader | U  | U  | Time o  | of Mute  |  |  |

# Select address 04(hex)

| Mode       | MSB |    | In | put Se | lecto | r  |    | LSB |

|------------|-----|----|----|--------|-------|----|----|-----|

| WOUG       | D7  | D6 | D5 | D4     | D3    | D2 | D1 | D0  |

| A          |     |    |    |        |       | 0  | 0  | 0   |

| В          |     |    |    |        |       | 0  | 0  | 1   |

| C          |     |    |    |        |       | 0  | 1  | 0   |

| D          | 0   | 0  | 0  | 0      | 0     | 1  | 0  | 0   |

| SHORT      |     |    |    |        |       | 1  | 0  | 1   |

| INPUT MUTE |     |    |    |        |       | 1  | 1  | 0   |

| INFUL MULE |     |    |    |        |       | 1  | 1  | 1   |

(D is available only BD37512FS.)

:Initial condition

**SHORT**: The input impedance of each input terminal is lowered from  $100k\Omega$  (TYP) to  $6~k\Omega$  (TYP).

(For quick charge of coupling capacitor)

$\textbf{INPUT MUTE}: \ \ \text{Mute is done at the input signal in the part of Input Selector}.$

Select address 06 (hex)

| Coin        | MSB         |    |    | Input | Gain |    |    | LSB   |

|-------------|-------------|----|----|-------|------|----|----|-------|

| Gain        | D7          | D6 | D5 | D4    | D3   | D2 | D1 | DO DO |

| 0dB         |             |    |    | 0     | 0    | 0  | 0  | 0     |

| 1dB         | 7           |    |    | 0     | 0    | 0  | 0  | 1     |

| 2dB         |             |    |    | 0     | 0    | 0  | 1  | 0     |

| 3dB         |             |    |    | 0     | 0    | 0  | 1  | 1     |

| 4dB         |             |    |    | 0     | 0    | 1  | 0  | 0     |

| 5dB         |             |    |    | 0     | 0    | 1  | 0  | 1     |

| 6dB         | 7           |    |    | 0     | 0    | 1  | 1  | 0     |

| 7dB         |             |    |    | 0     | 0    | 1  | 1  | 1     |

| 8dB         |             |    |    | 0     | 1    | 0  | 0  | 0     |

| 9dB         |             |    |    | 0     | 1    | 0  | 0  | 1     |

| 10dB        |             | 0  | 0  | 0     | 1    | 0  | 1  | 0     |

| 11dB        | Mute        |    |    | 0     | 1    | 0  | 1  | 1     |

| 12dB        | ON/OFF      |    |    | 0     | 1    | 1  | 0  | 0     |

| 13dB        |             |    |    | 0     | 1    | 1  | 0  | 1     |

| 14dB        |             |    |    | 0     | 1    | 1  | 1  | 0     |

| 15dB        |             |    |    | 0     | 1    | 1  | 1  | 1     |

| 16dB        | 7           |    |    | 1     | 0    | 0  | 0  | 0     |

| 17dB        |             |    |    | 1     | 0    | 0  | 0  | 1     |

| 18dB        | 7           |    |    | 1     | 0    | 0  | 1  | 0     |

| 19dB        | 7           |    |    | 1     | 0    | 0  | 1  | 1     |

| 20dB        | 7           |    |    | 1     | 0    | 1  | 0  | 0     |

|             |             |    |    | 1     | 1    | 0  | 1  | 1     |

| Prohibition | Prohibition |    |    | :     | :    | :  | :  | :     |

|             |             |    |    | 1     | 1    | 1  | 1  | 1     |

| Mode | MSB |     |    | Mute | LSB |            |    |    |

|------|-----|-----|----|------|-----|------------|----|----|

| Wode | D7  | D6  | D5 | D4   | D3  | D2         | D1 | D0 |

| 0FF  | 0   | 0   | ٥  |      |     | Innut Coin |    |    |

| ON   | 1   | ] 0 | U  |      |     | Input Gain |    |    |

:Initial condition

Select address 20 (hex)

| Gain & ATT  | MSB |    | Vo | I Att | enuat i | on |    | LSB |   |

|-------------|-----|----|----|-------|---------|----|----|-----|---|

| uaiii & Aii | D7  | D6 | D5 | D4    | D3      | D2 | D1 | D0  |   |

| 0dB         |     |    | 0  | 0     | 0       | 0  | 0  | 0   |   |

| -1dB        |     |    | 0  | 0     | 0       | 0  | 0  | 1   |   |

| -2dB        |     |    | 0  | 0     | 0       | 0  | 1  | 0   |   |

|             |     |    | •  | •     |         | •  | •  | •   |   |

| •           |     | 0  | •  | •     | •       | •  | •  | •   |   |

| •           |     |    |    | •     | •       | •  | •  | •   | • |

| -38dB       | 1   |    | 1  | 0     | 0       | 1  | 1  | 0   |   |

| -39dB       |     |    | 1  | 0     | 0       | 1  | 1  | 1   |   |

| -40dB       |     |    | 1  | 0     | 1       | 0  | 0  | 0   |   |

|             |     |    | 1  | 0     | 1       | 0  | 0  | 1   |   |

| Prohibition |     |    | :  | :     | • •     | •  | :  | :   |   |

| FIGHTDICION |     |    | 1  | 1     | 1       | 1  | 1  | 0   |   |

|             |     |    | 1  | 1     | 1       | 1  | 1  | 1   |   |

XIn case sending prohibited data, −40dB is set.

Select address 28, 29, 2A, 2B (hex)

| Gain & ATT | MSB |    | Fac | ler At | tenuat | ion |    | LSB |

|------------|-----|----|-----|--------|--------|-----|----|-----|

| dain & Aii | D7  | D6 | D5  | D4     | D3     | D2  | D1 | D0  |

| 0dB        |     |    | 0   | 0      | 0      | 0   | 0  | 0   |

| −1dB       |     |    | 0   | 0      | 0      | 0   | 0  | 1   |

| −2dB       |     |    | 0   | 0      | 0      | 0   | 1  | 0   |

| •          |     |    | •   | •      | •      | •   | •  | •   |

| •          | 1   | 0  | •   | -      | •      | •   | •  | •   |

| •          |     |    | •   | •      | •      | •   | •  | •   |

| -61dB      |     |    | 1   | 1      | 1      | 1   | 0  | 1   |

| -62dB      |     |    | 1   | 1      | 1      | 1   | 1  | 0   |

| -∞dB       |     |    | 1   | 1      | 1      | 1   | 1  | 1   |

: Initial condition

Select address 51, 57 (hex)

| Gain         | MSB          |    | Ba | ss/Tre | ble G | ain |    | LSB |

|--------------|--------------|----|----|--------|-------|-----|----|-----|

| uaiii        | D7           | D6 | D5 | D4     | D3    | D2  | D1 | D0  |

| 0dB          |              |    |    | 0      | 0     | 0   | 0  | 0   |

| 1dB          |              |    |    | 0      | 0     | 0   | 0  | 1   |

| 2dB          |              |    |    | 0      | 0     | 0   | 1  | 0   |

| 3dB          |              |    |    | 0      | 0     | 0   | 1  | 1   |

| 4dB          |              |    |    | 0      | 0     | 1   | 0  | 0   |

| 5dB          |              |    |    | 0      | 0     | 1   | 0  | 1   |

| 6dB          |              |    |    | 0      | 0     | 1   | 1  | 0   |

| 7dB          |              |    |    | 0      | 0     | 1   | 1  | 1   |

| 8dB          |              |    |    | 0      | 1     | 0   | 0  | 0   |

| 9dB          |              |    |    | 0      | 1     | 0   | 0  | 1   |

| 10dB         |              |    |    | 0      | 1     | 0   | 1  | 0   |

| 11dB         | Bass/        |    |    | 0      | 1     | 0   | 1  | 1   |

| 12dB         | Treble Boost | 0  | 0  | 0      | 1     | 1   | 0  | 0   |

| 13dB         | /cut         |    |    | 0      | 1     | 1   | 0  | 1   |

| 14dB         | 7 (4)        |    |    | 0      | 1     | 1   | 1  | 0   |

| 15dB         |              |    |    | 0      | 1     | 1   | 1  | 1   |

| 16dB         |              |    |    | 1      | 0     | 0   | 0  | 0   |

| 17dB         |              |    |    | 1      | 0     | 0   | 0  | 1   |

| 18dB         |              |    |    | 1      | 0     | 0   | 1  | 0   |

| 19dB         |              |    |    | 1      | 0     | 0   | 1  | 1   |

| 20dB         |              |    |    | 1      | 0     | 1   | 0  | 0   |

|              |              |    |    | 1      | 0     | 1   | 0  | 1   |

| Prohibition  |              |    |    | :      | :     | :   | :  | :   |

| רוטווטונוטוו |              |    |    | 1      | 1     | 1   | 1  | 0   |

|              |              |    |    | 1      | 1     | 1   | 1  | 1   |

※In case sending prohibited data, OdB is set.

| Mode  | MSB |     | Bass/ | LSB      |    |    |    |    |

|-------|-----|-----|-------|----------|----|----|----|----|

| Wode  | D7  | D6  | D5    | D4       | D3 | D2 | D1 | D0 |

| Boost | 0   | 0   | 0     | Bass/Tre |    |    |    |    |

| Cut   | 1   | ] " | "     | ble Gain |    |    |    |    |

:Initial condition

#### (6) About power on reset

At on of supply voltage circuit made initialization inside IC is built-in. Please send data to all address as initial data at supply voltage on. And please supply mute at set side until this initial data is sent.

| l+om                                  | Cumbal |      | Limit |      | Unit   | Condition                   |  |  |

|---------------------------------------|--------|------|-------|------|--------|-----------------------------|--|--|

| Item                                  | Symbol | Min. | Тур.  | Max. | UIII L |                             |  |  |

| Rise time of VCC                      | Trise  | 20   | _     | _    | usec   | VCC rise time from OV to 3V |  |  |

| VCC voltage of release power on reset | Vpor   | _    | 4. 1  | _    | ٧      |                             |  |  |

# (7) About external compulsory mute terminal

Mute is possible forcibly than the outside after input again department, by the setting of the MUTE terminal.

| Mute Voltage Condition | Mode     |

|------------------------|----------|

| GND∼1. 0V              | MUTE ON  |

| 2. 3V~VCC              | MUTE OFF |

Establish the voltage of MUTE in the condition to have been defined.

Volume / Fader volume attenuation of the details

| (dB)        | D7 | D6 | D5 | D4 | D3      | D2 | D1 | D0 |         | (dB) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------|----|----|----|----|---------|----|----|----|---------|------|----|----|----|----|----|----|----|----|

| 0           |    |    | 0  | 0  | 0       | 0  | 0  | 0  |         | -32  |    |    | 1  | 0  | 0  | 0  | 0  | 0  |

| -1          |    |    | 0  | 0  | 0       | 0  | 0  | 1  |         | -33  |    |    | 1  | 0  | 0  | 0  | 0  | 1  |

| -2          |    |    | 0  | 0  | 0       | 0  | 1  | 0  |         | -34  |    |    | 1  | 0  | 0  | 0  | 1  | 0  |

| -3          |    |    | 0  | 0  | 0       | 0  | 1  | 1  |         | -35  |    |    | 1  | 0  | 0  | 0  | 1  | 1  |

| -4          |    |    | 0  | 0  | 0       | 1  | 0  | 0  |         | -36  |    |    | 1  | 0  | 0  | 1  | 0  | 0  |

| -5          |    |    | 0  | 0  | 0       | 1  | 0  | 1  |         | -37  |    |    | 1  | 0  | 0  | 1  | 0  | 1  |

| -6          |    |    | 0  | 0  | 0       | 1  | 1  | 0  |         | -38  |    |    | 1  | 0  | 0  | 1  | 1  | 0  |

| -7          |    |    | 0  | 0  | 0       | 1  | 1  | 1  |         | -39  |    |    | 1  | 0  | 0  | 1  | 1  | 1  |

| -8          |    |    | 0  | 0  | 1       | 0  | 0  | 0  |         | -40  |    |    | 1  | 0  | 1  | 0  | 0  | 0  |

| -9          |    |    | 0  | 0  | 1       | 0  | 0  | 1  |         | -41  |    |    | 1  | 0  | 1  | 0  | 0  | 1  |

| -10         |    |    | 0  | 0  | 1       | 0  | 1  | 0  |         | -42  |    |    | 1  | 0  | 1  | 0  | 1  | 0  |

| -11         |    |    | 0  | 0  | 1       | 0  | 1  | 1  |         | -43  |    |    | 1  | 0  | 1  | 0  | 1  | 1  |

| -12         |    |    | 0  | 0  | 1       | 1  | 0  | 0  |         | -44  |    |    | 1  | 0  | 1  | 1  | 0  | 0  |

| -13         |    |    | 0  | 0  | 1       | 1  | 0  | 1  |         | -45  |    |    | 1  | 0  | 1  | 1  | 0  | 1  |

| -14         |    |    |    | 0  | 0       | 1  | 1  | 1  | 1 0 -46 | -46  |    |    | 1  | 0  | 1  | 1  | 1  | 0  |

| -15         | 1  | 0  | 0  | 0  | 1       | 1  | 1  | 1  |         | -47  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  |

| -16         | '  | U  | 0  | 1  | 0       | 0  | 0  | 0  |         | -48  | '  | U  | 1  | 1  | 0  | 0  | 0  | 0  |

| -17         |    |    | 0  | 1  | 0       | 0  | 0  | 1  |         | -49  |    |    | 1  | 1  | 0  | 0  | 0  | 1  |

| -18         |    |    | 0  | 1  | 0       | 0  | 1  | 0  |         | -50  |    |    | 1  | 1  | 0  | 0  | 1  | 0  |

| -19         |    |    | 0  | 1  | 0       | 0  | 1  | 1  |         | -51  |    |    | 1  | 1  | 0  | 0  | 1  | 1  |

| -20         |    |    | 0  | 1  | 0       | 1  | 0  | 0  |         | -52  |    |    | 1  | 1  | 0  | 1  | 0  | 0  |

| -21         |    | Ì  | 0  | 1  | 0       | 1  | 0  | 1  |         | -53  |    |    | 1  | 1  | 0  | 1  | 0  | 1  |

| -22         |    |    | 0  | 1  | 0       | 1  | 1  | 0  |         | -54  |    |    | 1  | 1  | 0  | 1  | 1  | 0  |

| -23         |    | Ì  | 0  | 1  | 0       | 1  | 1  | 1  |         | -55  |    |    | 1  | 1  | 0  | 1  | 1  | 1  |

| -24         |    |    | 0  | 1  | 1       | 0  | 0  | 0  |         | -56  |    |    | 1  | 1  | 1  | 0  | 0  | 0  |

| -25         |    | Ì  | 0  | 1  | 1       | 0  | 0  | 1  |         | -57  |    |    | 1  | 1  | 1  | 0  | 0  | 1  |

| -26         |    |    | 0  | 1  | 1       | 0  | 1  | 0  |         | -58  |    |    | 1  | 1  | 1  | 0  | 1  | 0  |

| -27         |    | ì  | 0  | 1  | 1       | 0  | 1  | 1  |         | -59  |    |    | 1  | 1  | 1  | 0  | 1  | 1  |

| -28         |    |    | 0  | 1  | 1       | 1  | 0  | 0  |         | -60  |    |    | 1  | 1  | 1  | 1  | 0  | 0  |

| -29         |    |    | 0  | 1  | 1       | 1  | 0  | 1  |         | -61  |    |    | 1  | 1  | 1  | 1  | 0  | 1  |

| -30         |    |    | 0  | 1  | 1       | 1  | 1  | 0  |         | -62  |    |    | 1  | 1  | 1  | 1  | 1  | 0  |

| -31         |    |    | 0  | 1  | 1       | 1  | 1  | 1  |         | -∞   |    |    | 1  | 1  | 1  | 1  | 1  | 1  |

| About Value |    |    |    |    | . AdD . | 40 | ID |    | ملطما   |      |    |    |    |    |    |    |    |    |

About Volume attenuation, only  $0dB \sim -40dB$  are available.

: Initial condition

#### Application circuit

Fig. 20 BD37511FS

#### Notes on wiring

- ① Please connect the decoupling capacitor of a power supply in the shortest distance as much as possible to GND.

- 2 Lines of GND shall be one-point connected.

- ③ Wiring pattern of Digital shall be away from that of analog unit and cross-talk shall not be acceptable. ④ Lines of SCL and SDA of I<sup>2</sup>C BUS shall not be parallel if possible.

- The lines shall be shielded, if they are adjacent to each other.

- (5) Lines of analog input shall not be parallel if possible. The lines shall be shielded, if they are adjacent to each other.

- 6 About TEST pin(7,8,9pin), please use with OPEN.

Fig. 21 BD37512FS

#### Notes on wiring

- ① Please connect the decoupling capacitor of a power supply in the shortest distance as much as possible to GND.

- Z Lines of GND shall be one-point connected.

- ③ Wiring pattern of Digital shall be away from that of analog unit and cross-talk shall not be acceptable.

- 4 Lines of SCL and SDA of  $I^2C$  BUS shall not be parallel if possible. The lines shall be shielded, if they are adjacent to each other.

- ⑤ Lines of analog input shall not be parallel if possible. The lines shall be shielded, if they are adjacent to each other.

# ●Interfaces

| Terminal             | Terminal                         | Terminal | Equivalent Circuit                                   | Terminal Description                                                                                                                                   |

|----------------------|----------------------------------|----------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.                  | Name                             | Voltage  | Vcc O                                                | A terminal for signal input. The input impedance is 100kΩ(typ).                                                                                        |

| 2                    | A1<br>A2                         |          | <b>↓</b> •                                           |                                                                                                                                                        |

| 3<br>4               | B1<br>B2                         | 4. 25    | 7 ≥ 100k                                             |                                                                                                                                                        |

| 5<br>6               | C1<br>C2                         |          | GND $\downarrow$                                     |                                                                                                                                                        |

| 7 9                  | DP1<br>DP1                       | 4. 25    | VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>VCC | A terminal for positive input of ground isolation amplifier. (BD37512FS) The input impedance is $50k\Omega$ (typ).                                     |

| 8                    | DN                               | 4. 25    | VCC                                                  | A terminal for negative input of ground isolation amplifier. (BD37512FS) The input impedance is 12.5kΩ (typ).                                          |

| 16                   | MUTE                             | _        | Voc<br>O<br>D<br>D<br>1.65V                          | A terminal for external compulsory mute. If terminal voltage is High level, the mute is off. And if the terminal voltage is Low level, the mute is on. |

| 11<br>12<br>13<br>14 | OUTR2<br>OUTR1<br>OUTF2<br>OUTF1 | 4. 25    | Vcc<br>GND<br>GND                                    | A terminal for fader and Subwoofer output.                                                                                                             |

The figure in the pin explanation and input/output equivalent circuit is reference value, it doesn't guarantee the value.

| Terminal    | Terminal                | Terminal       | Equivalent Circuit                                                                            | Terminal Description                                                                                                                                           |

|-------------|-------------------------|----------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.         | Name<br>VCC             | Voltage<br>8.5 |                                                                                               | Power supply terminal.                                                                                                                                         |

| 17          | SCL                     | _              | VCC<br>O<br>O<br>I.65V                                                                        | A terminal for clock input of I <sup>2</sup> C BUS communication.                                                                                              |

| 18          | SDA                     | _              | Vcc<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O | A terminal for data input of I <sup>2</sup> C BUS communication.                                                                                               |

| 19          | GND                     | 0              |                                                                                               | Ground terminal.                                                                                                                                               |

| 20          | FIL                     | 4. 25          | VCC  A  Solv  GND                                                                             | Voltage for reference bias of analog<br>signal system. The simple precharge<br>circuit and simple discharge circuit for<br>an external capacitor are built in. |

| 7<br>8<br>9 | TEST1<br>TEST2<br>TEST3 | -              |                                                                                               | TEST terminal. (BD37511FS)                                                                                                                                     |

The figure in the pin explanation and input/output equivalent circuit is reference value, it doesn't guarantee the value.

#### Notes for use

# 1. Absolute maximum rating voltage

When it impressed the voltage on VCC more than the absolute maximum rating voltage, circuit currents increase rapidly, and there is absolutely a case to reach characteristic deterioration and destruction of a device. In particular in a serge examination of a set, when it is expected the impressing serge at VCC terminal (15pin), please do not impress the large and over the absolute maximum rating voltage (including a operating voltage + serge ingredient (around 14V)).

#### 2. About a signal input part

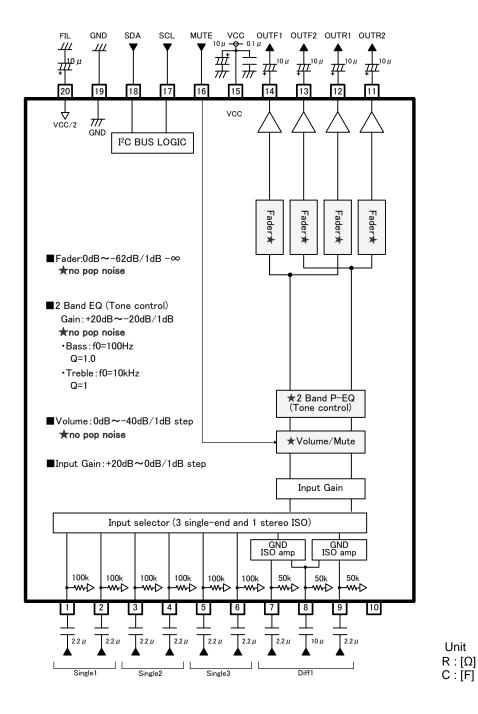

#### 1) About constant set up of input coupling capacitor

In the signal input terminal, the constant setting of input coupling capacitor C(F) be sufficient input impedance  $R_{IN}(\Omega)$  inside IC and please decide. The first HPF characteristic of RC is composed.

#### 2) About the input selector SHORT

SHORT mode is the command which makes switch  $S_{SH}$  =0N an input selector part and input impedance RIN of all terminals, and makes resistance small. Switch  $S_{SH}$  is OFF when not choosing a SHORT command. A constant time becomes small at the time of this command twisting to the resistance inside the capacitor

A constant time becomes small at the time of this command twisting to the resistance inside the capacitor connected outside and LSI. The charge time of a capacitor becomes short.

Since SHORT mode turns ON the switch of S<sub>SH</sub> and makes it low impedance, please use it at the time of a non-signal.

#### 3. About Mute terminal(11pin) when power supply is off

Any voltage shall not be supplied to Mute terminal (16pin) when power-supply is off. Please insert a resistor (about  $2.2k\Omega$ ) to Mute terminal in series, if voltage is supplied to mute terminal in case. (Please refer Application Circuit Diagram.)

#### 4. About TEST Pin

About TEST Pin, please use with OPEN. About BD37511FS, 7, 8,9pin is TEST Pin.

#### ●Thermal Derating Curve

About the thermal design by the IC

Characteristics of an IC have a great deal to do with the temperature at which it is used, and exceeding absolute maximum ratings may degrade and destroy elements. Careful consideration must be given to the heat of the IC from the two standpoints of immediate damage and long-term reliability of operation.

Fig.22 Temperature Derating Curve

Note) Values are actual measurements and are not guaranteed.

Power dissipation values vary according to the board on which the IC is mounted.

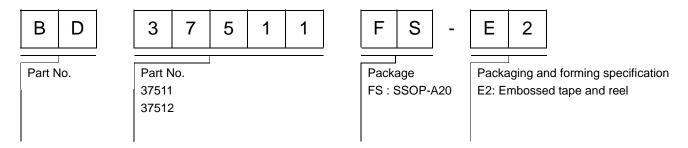

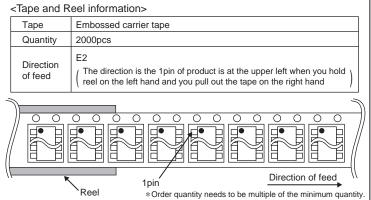

# Ordering part number

# SSOP-A20

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/