# 400 MHz Low Power 2:8 Fan-Out Buffer with Universal Inputs and Outputs

Check for Samples: CDCUN1208LP

#### **FEATURES**

- Support PCIE gen1, gen2, gen3

- Configuration Options (via pins or SPI/I<sup>2</sup>C):

- Input Type (HCSL, LVDS, LVCMOS)

- Output Type (HCSL, LVDS, LVCMOS)

- Signal Edge Rate (Slow, Medium, Fast)

- Clock Input Divide Value (/1, /2, /4, /8) IN2 only

- Low Power Consumption and Power Management Features Including 1.8V Operation and Output Enable Control

- Integrated Voltage Regulators Improve PSNR

- Excellent Additive Jitter Performance

- 200 fs RMS (10kHz-20MHz), LVDS at 100MHz

- 160 fs RMS (10kHz-20MHz), HCSL at 100MHz

- Maximum Operating Frequency:

- Differential Mode: up to 400 MHz

- LVCMOS Mode: up to 250 MHz

- ESD Protection Exceeds 2kV HBM, 500V CDM

- Industrial Temperature Range (-40°C to 85°C)

- Wide Supply Range (1.8V, 2.5V, or 3.3V)

#### **APPLICATIONS**

- Communications Systems (Ethernet, PCI Express)

- Computing Systems (Ethernet, PCIe, USB)

- Consumer (Set top boxes, video equipment)

- Office Automation

## **DESCRIPTION**

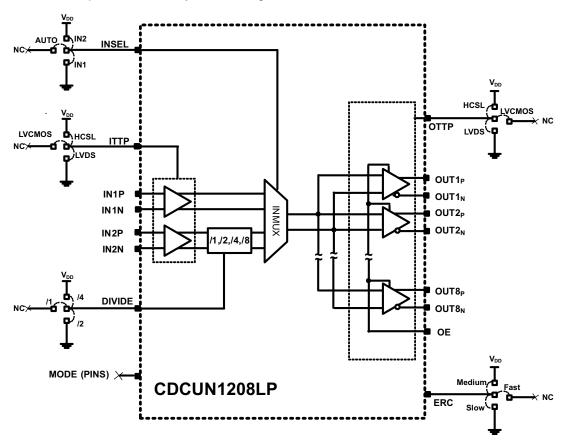

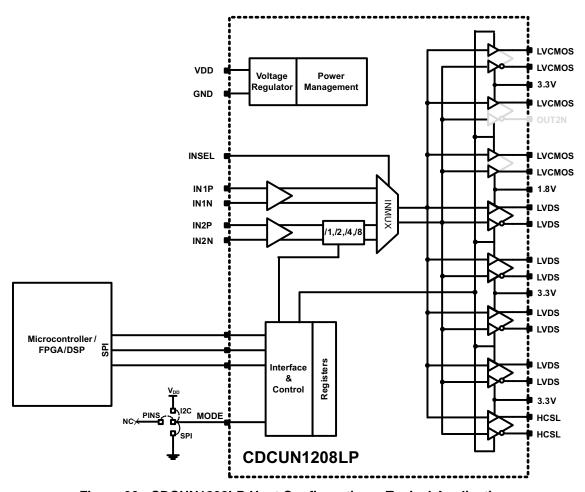

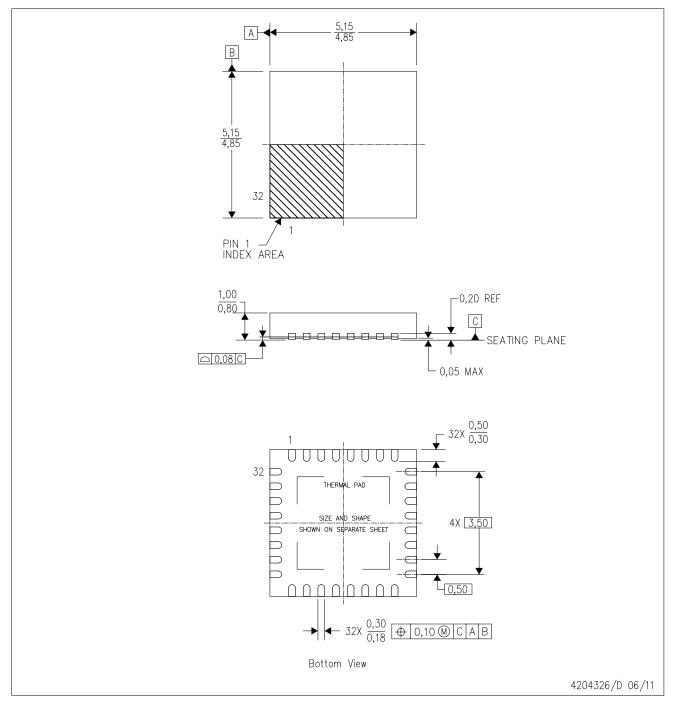

The CDCUN1208LP is a 2:8 fan-out buffer featuring a wide operating supply range, two universal differential/single-ended inputs, and universal outputs (HCSL, LVDS, or LVCMOS) with edge rate control. The clock buffer supports PCIE gen1, gen2 and gen3. One of the device inputs includes a divider that provides divide values of /1, /2, /4, or /8. The CDCUN1208LP is offered in a 32 pin QFN package reducing the solution footprint. The device is flexible and easy to use. The state of certain pins determines device configuration at power up. Alternately, the CDCUN1208LP provides a SPI/I<sup>2</sup>C port with which a host processor controls device settings. The CDCUN1208LP delivers excellent additive jitter performance, and low power consumption. The output section includes four dedicated supply pins enabling the operation of output ports from different power supply domains. This provides the ability to clock devices switching at different LVCMOS levels without the need for external logic level translation circuitry.

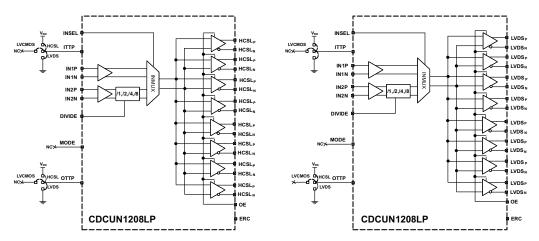

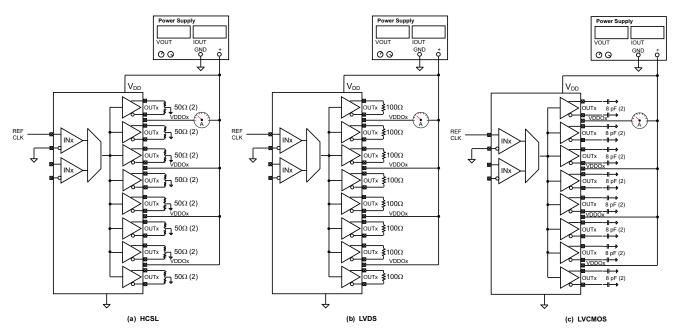

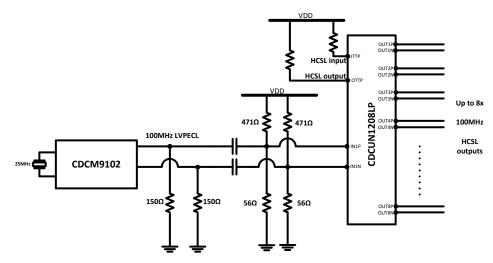

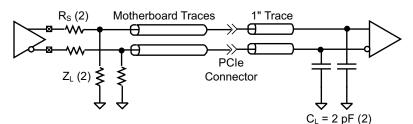

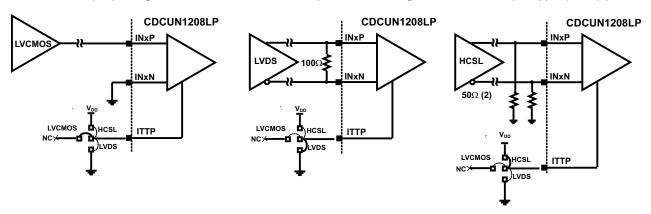

Figure 1. CDCUN1208LP Applications – HCSL and LVDS Fan-Out Buffer Mode

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

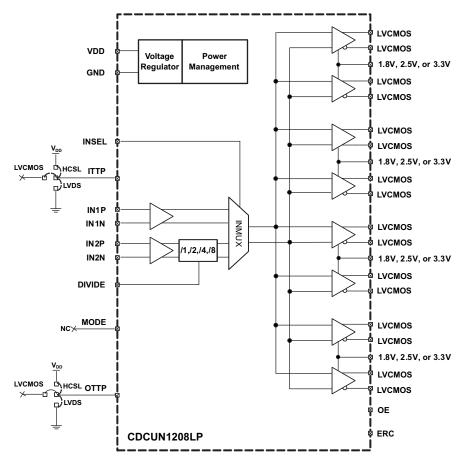

Figure 2. CDCUN1208LP Typical Application Example - LVCMOS Output Mode

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

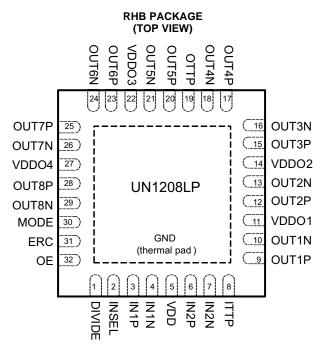

## PIN FUNCTIONS(1)

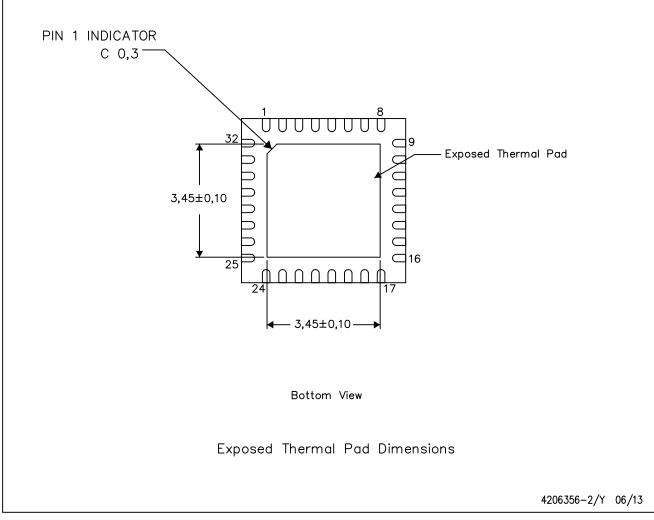

| NAME   | PIN<br>NUMBER | DESCRIPTION                                                                                                                                                                                                                                                                                       |

|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND    | Thermal Pad   | Power supply ground and thermal relief                                                                                                                                                                                                                                                            |

| VDD    | 5             | Device Power Supply, Provides power to the input section and clock distribution section. Use a power supply voltage that corresponds to the switching levels of clock input(s) (i.e. 1.8V, 2.5V, or 3.3V).                                                                                        |

| MODE   | 30            | Device Control Mode Select  OPEN = Device Configured via pins (Pin Mode)  HIGH = Device Configured via I <sup>2</sup> C  LOW = Device Configured via SPI  Note: For information on control via the serial interface (I <sup>2</sup> C/ SPI), see DEVICE CONTROL USING THE HOST INTERFACE section. |

| DIVIDE | 1             | Input Divider Pin Control (HIGH = /4, LOW = /2, OPEN = /1)                                                                                                                                                                                                                                        |

| OE     | 32            | Device Output Enable HIGH = Enable, LOW = Disable                                                                                                                                                                                                                                                 |

| ERC    | 31            | Output Edge Rate Control HIGH = Medium, LOW = Slow, OPEN = Fast                                                                                                                                                                                                                                   |

| INSEL  | 2             | Input Multiplexer Control                                                                                                                                                                                                                                                                         |

| ITTP   | 8             | Input Type Select (HIGH = HCSL, LOW = LVDS, OPEN = LVCMOS)                                                                                                                                                                                                                                        |

| IN1P   | 3             | Universal Input 1 – Positive Terminal                                                                                                                                                                                                                                                             |

| IN1N   | 4             | Universal Input 1 – Negative Terminal, Ground if using IN1 in single-ended mode                                                                                                                                                                                                                   |

| IN2P   | 6             | Universal Input 2 – Positive Terminal                                                                                                                                                                                                                                                             |

| IN2N   | 7             | Universal Input 2 – Negative Terminal, Ground if using IN2 in single-ended mode                                                                                                                                                                                                                   |

| OTTP   | 19            | Output Type Select (HIGH = HCSL, LOW = LVDS, OPEN = LVCMOS)                                                                                                                                                                                                                                       |

| OUT1P  | 9             | Output 1 – Positive Terminal                                                                                                                                                                                                                                                                      |

| OUT1N  | 10            | Output 1 – Negative Terminal                                                                                                                                                                                                                                                                      |

| VDDO1  | 11            | Output Power Supply – OUT1, OUT2                                                                                                                                                                                                                                                                  |

| OUT2P  | 12            | Output 2 – Positive Terminal                                                                                                                                                                                                                                                                      |

(1) This pin list applies to operation of the device in pin mode. In host mode, certain pins take on an alternate function as outlined in Table 9.

Product Folder Links: CDCUN1208LP

## PIN FUNCTIONS<sup>(1)</sup> (continued)

| NAME  | PIN<br>NUMBER | DESCRIPTION                                                                                                                     |

|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

| OUT2N | 13            | Output 2 – Negative Terminal                                                                                                    |

| VDDO2 | 14            | Output Power Supply – OUT3, OUT4; Output bank OUT1 – OUT4 regulator power supply (apply power if any of OUT1 – OUT4 are needed) |

| OUT3P | 15            | Output 3 – Positive Terminal                                                                                                    |

| OUT3N | 16            | Output 3 – Negative Terminal                                                                                                    |

| OUT4P | 17            | Output 4 – Positive Terminal                                                                                                    |

| OUT4N | 18            | Output 4 – Negative Terminal                                                                                                    |

| OUT5P | 20            | Output 5 – Positive Terminal                                                                                                    |

| OUT5N | 21            | Output 5 – Negative Terminal                                                                                                    |

| VDDO3 | 22            | Output Power Supply - OUT5, OUT6                                                                                                |

| OUT6P | 23            | Output 6 – Positive Terminal                                                                                                    |

| OUT6N | 24            | Output 6 – Negative Terminal                                                                                                    |

| OUT7P | 25            | Output 7 – Positive Terminal                                                                                                    |

| OUT7N | 26            | Output 7 – Negative Terminal                                                                                                    |

| VDDO4 | 27            | Output Power Supply – OUT7, OUT8 Output bank OUT5 – OUT8 regulator power supply (apply power if any of OUT5 – OUT8 are needed)  |

| OUT8P | 28            | Output 8 – Positive Terminal                                                                                                    |

| OUT8N | 29            | Output 8 – Negative Terminal                                                                                                    |

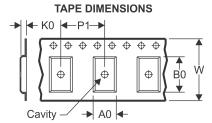

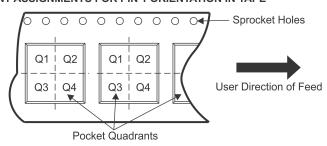

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGED DEVICES | FEATURES                                      |

|----------------|------------------|-----------------------------------------------|

| -40°C to 85°C  | CDCUN1208LPRHBT  | 32-pin QFN (RHB) package, small tape and reel |

| –40°C to 85°C  | CDCUN1208LPRHBR  | 32-pin QFN (RHB) package, tape and reel       |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                     | VALUE                           | UNIT |

|------------------|-------------------------------------|---------------------------------|------|

| $V_{DDxx}$       | Supply voltage range <sup>(2)</sup> | -0.5 to 4.6                     | V    |

| V <sub>IN</sub>  | Input voltage range (3)             | -0.5 to V <sub>DDlx</sub> + 0.5 | V    |

| V <sub>OUT</sub> | Output voltage range (3)            | $-0.5$ to $V_{DDOx} + 0.5$      | V    |

| I <sub>IN</sub>  | Input current                       | 20                              | mA   |

| I <sub>OUT</sub> | Output current                      | 50                              | mA   |

| T <sub>STG</sub> | Storage temperature range           | -65 to 150                      | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All supply voltages must be supplied simultaneously

<sup>(3)</sup> The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

#### THERMAL INFORMATION

|                  |                                              | CDCUN1208LP |       |

|------------------|----------------------------------------------|-------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | QFN32       | UNITS |

|                  |                                              | 32 PINS     |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 32.5        |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 24.2        |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 6.6         | 90044 |

| Ψлт              | Junction-to-top characterization parameter   | 0.3         | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter | 6.6         |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 1.6         |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### RECOMMENDED OPERATING CONDITIONS

$T_{\Delta} = -40^{\circ}C \text{ TO } 85^{\circ}C$

|                 |                            |           | MIN   | NOM | MAX   | UNIT |

|-----------------|----------------------------|-----------|-------|-----|-------|------|

| POWER           | SUPPLIES <sup>(1)(2)</sup> |           |       |     |       |      |

| V <sub>DD</sub> | DC Power Supply - Core     | 1.8V Mode | 1.7   | 1.8 | 1.9   | V    |

| $V_{DDOx}$      | DC Power Supply - Output   | 1.8V Mode | 1.7   | 1.8 | 1.9   | V    |

| $V_{DD}$        | DC Power Supply - Core     | 2.5V Mode | 2.375 | 2.5 | 2.625 | V    |

| $V_{DDOx}$      | DC Power Supply - Output   | 2.5V Mode | 2.375 | 2.5 | 2.625 | V    |

| $V_{DD}$        | DC Power Supply - Core     | 3.3V Mode | 2.97  | 3.3 | 3.63  | V    |

| $V_{DDOx}$      | DC Power Supply - Output   | 3.3V Mode | 2.97  | 3.3 | 3.63  | V    |

| TEMPER          | RATURE                     |           |       |     | ,     |      |

| T <sub>A</sub>  | Free- Air Temperature      |           | -40   |     | 85    | °C   |

<sup>(1)</sup> For proper device operation, the core power supply voltage (pin 5) must be applied either before the application of any output power supply or simultaneously with the application of the output power supplies. The application of an output power supply prior to the application of the core power supply could result in improper device behavior.

Table 1. CDCUN1208LP Power Consumption ( $T_A = -40$ °C to 85°C)

|                              |        | DE | ICE SE | TTINGS | (See Tab | le 2) <sup>(1)</sup> |        | TEST                                                           |                                                                   | MAX CURRENT                                    | MAX CURRENT                                 |      |

|------------------------------|--------|----|--------|--------|----------|----------------------|--------|----------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|------|

| PARAMETER                    | MODE   | OE | ERC    | ОТТР   | INSEL    | ITTP                 | PD Bit | CONFIGURATION                                                  | DESCRIPTION                                                       | $V_{DD}=1.8V$ $f_{OUT}=f_{in}=100 \text{ MHz}$ | $V_{DD} = 3.3V$ $f_{OUT} = f_{in} = 100MHz$ | UNIT |

| I <sub>PD1.8,3.3</sub>       | L or H | L  | х      | x      | x        | L                    | н      | Host Configuration<br>Mode<br>(see Host<br>Configuration Mode) | Device Power Down                                                 | 3                                              | 4                                           | mA   |

| I <sub>CORE1.8,3.3</sub>     | 0      | L  | Х      | Х      | Х        | L                    | Х      | Figure 19a,b,c                                                 | Device Outputs Off                                                | 26                                             | 35                                          | mA   |

| I <sub>HCSL1.8,3.3</sub>     | 0      | Н  | 0      | Н      | L        | 0                    | х      | Figure 19a                                                     | HCSL Buffer Current<br>Consumption (2)                            | 23                                             | 23                                          | mA   |

| I <sub>LVDS1.8,3.3</sub>     | 0      | Н  | 0      | L      | L        | 0                    | х      | Figure 19b                                                     | LVDS Buffer Current<br>Consumption (2)                            | 9                                              | 9                                           | mA   |

| I <sub>LVCMOS1.8,3.3</sub>   | 0      | Н  | 0      | 0      | L        | 0                    | х      | Figure 19c                                                     | LVCMOS Buffer<br>Current Consumption<br>(one side) <sup>(2)</sup> | 8                                              | 11                                          | mA   |

| I <sub>DEV-HCSL1.8,3.3</sub> | 0      | Н  | 0      | Н      | L        | 0                    | х      | Figure 19a                                                     | Device Current<br>Consumption – HCSL<br>Mode                      | 200                                            | 200                                         | mA   |

| I <sub>DEV-LVDS1.8,3.3</sub> | 0      | I  | 0      | L      | L        | 0                    | х      | Figure 19b                                                     | Device Current<br>Consumption – LVDS<br>Mode                      | 80                                             | 90                                          | mA   |

<sup>(1)</sup> H = Input High, L = Input Low; O = Input Open

Copyright © 2012–2013, Texas Instruments Incorporated

<sup>(2)</sup> A minimum V<sub>DD</sub> slew rate of 6500V/s should be obtained to ensure proper device functionality in Pin Mode. If the ambient temperature of the device is >0°C, the slew rate can be as slow as 5000V/s. In Host Mode (I<sup>2</sup>C/SPI), the V<sub>DD</sub> slew rate is not limited, if the Reset bit gets toggled after V<sub>DD</sub> ramp.

<sup>(2)</sup> Buffer current consumption values represent the average of the current drawn by V<sub>DDO1</sub>, V<sub>DDO2</sub>, V<sub>DDO3</sub>, and V<sub>DDO4</sub> divided by 8 (differential mode) or 16 (single-ended mode).

## Table 1. CDCUN1208LP Power Consumption ( $T_A = -40^{\circ}\text{C}$ to 85°C) (continued)

|                                | DEVICE SETTINGS (See Table 2) <sup>(1)</sup> |    |     |      |       |      |        | TEST          |                                                | MAX CURRENT                                          | MAX CURRENT                                 |      |

|--------------------------------|----------------------------------------------|----|-----|------|-------|------|--------|---------------|------------------------------------------------|------------------------------------------------------|---------------------------------------------|------|

| PARAMETER                      | MODE                                         | OE | ERC | ОТТР | INSEL | ITTP | PD Bit | CONFIGURATION | DESCRIPTION                                    | $V_{DD} = 1.8V$ $f_{OUT} = f_{in} = 100 \text{ MHz}$ | $V_{DD} = 3.3V$ $f_{OUT} = f_{in} = 100MHz$ | UNIT |

| I <sub>DEV-LVCMOS1.8,3.3</sub> | 0                                            | Н  | 0   | 0    | L     | 0    | ×      | Figure 19c    | Device Current<br>Consumption –<br>LVCMOS Mode | 130                                                  | 210                                         | mA   |

## DIGITAL INPUT ELECTRICAL CHARACTERISTICS – OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), MODE

$T_{\Delta} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$

|                       | PARAMETER                       | TEST CONDITIONS                                                    | MIN  | TYP MAX | UNIT |

|-----------------------|---------------------------------|--------------------------------------------------------------------|------|---------|------|

| LVCMOS I              | NPUT                            |                                                                    | ,    | 1       |      |

| V <sub>IL1.8</sub>    | Low level LVCMOS input voltage  | V <sub>DD</sub> = 1.8 V                                            |      | 0.7     | V    |

| V <sub>IH1.8</sub>    | High level LVCMOS input voltage | V <sub>DD</sub> = 1.8 V                                            | 1.35 |         | V    |

| V <sub>IOPEN1.8</sub> | OPEN level LVCMOS input voltage | V <sub>DD</sub> = 1.8 V                                            | 0.75 | 1.2     | V    |

| $V_{\text{IL}2.5}$    | Low level LVCMOS input voltage  | V <sub>DD</sub> = 2.5 V                                            |      | 0.7     | V    |

| V <sub>IH2.5</sub>    | High level LVCMOS input voltage | V <sub>DD</sub> = 2.5 V                                            | 1.71 |         | V    |

| V <sub>IOPEN2.5</sub> | OPEN level LVCMOS input voltage | V <sub>DD</sub> = 2.5 V                                            | 1.0  | 1.6     | V    |

| V <sub>IL3.3</sub>    | Low level LVCMOS input voltage  | V <sub>DD</sub> = 3.3 V                                            |      | 1.0     | V    |

| V <sub>IH3.3</sub>    | High level LVCMOS input voltage | V <sub>DD</sub> = 3.3 V                                            | 2.3  |         | V    |

| V <sub>IOPEN3.3</sub> | OPEN level LVCMOS input voltage | V <sub>DD</sub> = 3.3 V                                            | 1.3  | 1.9     | V    |

| I <sub>IL</sub>       | Low level LVCMOS input current  | $V_{DD} = V_{DDmax}, V_{ILCMOS} = 0 V$                             |      | -120    | μΑ   |

| I <sub>IH</sub>       | High level LVCMOS input current | V <sub>DD</sub> = V <sub>DDmax</sub> , V <sub>IHCMOS</sub> = 1.9 V |      | 65      | μΑ   |

| C <sub>I</sub>        | LVCMOS Input capacitance        |                                                                    |      | 6       | pF   |

| V <sub>IK</sub>       | Digital input clamp voltage     | $V_{DD} = 1.7V, I_I = -18 \text{ mA}$                              |      | -1.2    | V    |

## **UNIVERSAL INPUT (IN1, IN2) CHARACTERISTICS**

$V_{DD} = 1.8V, 2.5V, 3.3V, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$

|                      | PARAMETER                 | TEST CONDITIONS                                    | MIN                 | TYP MAX               | UNIT |

|----------------------|---------------------------|----------------------------------------------------|---------------------|-----------------------|------|

| SINGLE-E             | NDED MODE                 |                                                    |                     |                       |      |

| f <sub>IN1,2</sub>   | Input frequency           | Single ended <sup>(1)</sup>                        | 0.008               | 250                   | MHz  |

| V <sub>IH</sub>      | Input voltage - high      | 250 MHz                                            | $0.7 \times V_{DD}$ | $V_{DD}$              | V    |

| V <sub>IL</sub>      | Input voltage - low       | 250 MHz                                            |                     | 0.2 × V <sub>DD</sub> | V    |

| DIFFEREN             | NTIAL MODE                | ,                                                  | •                   |                       |      |

| f <sub>INDIFF</sub>  | Input frequency           |                                                    | 0.008               | 400                   | MHz  |

| 1) /                 | land and a                | V <sub>DD</sub> = 2.5 V, 3.3 V                     | 0.15                | 1.6                   | V    |

| V <sub>IN-DIFF</sub> | Input swing               | V <sub>DD</sub> = 1.8 V                            | 0.15                | 1                     | V    |

|                      |                           | ITTP = LVDS, V <sub>DD</sub> = 3.3 V               | 0.8                 | 2.5                   |      |

| $V_{CM}$             | Input common mode voltage | ITTP = LVDS, V <sub>DD</sub> = 2.5 V, 1.8 V        | 0.8                 | V <sub>DD</sub> - 0.3 | V    |

|                      |                           | ITTP = HCSL                                        | -0.15               | 0.75                  |      |

| GENERAL              | CHARACTERISTICS           |                                                    |                     |                       |      |

| I <sub>IH</sub>      | Input current - high      | V <sub>DD</sub> = 3.63 V, V <sub>IH</sub> = 3.63 V |                     | 30                    | μA   |

| I <sub>IL</sub>      | Input current - low       | V <sub>DD</sub> = 3.63 V, V <sub>IL</sub> = 0 V    |                     | -30                   | μA   |

| ΔV/ΔΤ                | Input edge rate           | 20%–80%                                            | 0.75                |                       | V/ns |

| DC <sub>IN</sub>     | Input duty cycle          |                                                    | 40                  | 60%                   |      |

| C <sub>IN</sub>      | Input capacitance         |                                                    |                     | 3.5                   | pF   |

<sup>(1)</sup> When using an input in single-ended mode, ground the negative terminal (IN1N and/or IN2N) and drive the positive terminal (IN1P and/or IN2P).

Product Folder Links : CDCUN1208LP

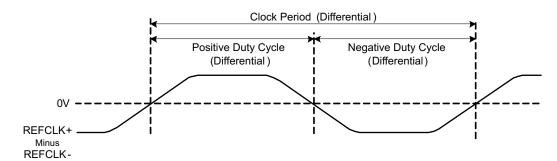

## **CLOCK OUTPUT BUFFER CHARACTERISTICS (OUTPUT MODE = LVDS)**

Unless otherwise noted,  $V_{DDOX} = 1.8V$ , 2.5V, 3.3V;  $T_A = -40$ °C to 85°C. See Figure 9, Figure 10, and Figure 11.

|                                    | PARAMETER                                                  | TEST CONDITIONS                                                                                     | MIN   | TYP | MAX   | UNIT      |

|------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------|-----|-------|-----------|

| f <sub>OUT</sub>                   | Output frequency                                           |                                                                                                     | 0.008 |     | 400   | MHz       |

| V                                  | Output common mode voltage,<br>VDDOx = 2.5/3.3 V           | R <sub>L</sub> = 100 Ω                                                                              | 1.125 | 1.2 | 1.275 | V         |

| V <sub>CM</sub>                    | Output common mode voltage,<br>VDDOx = 1.8 V               | R <sub>L</sub> = 100 Ω                                                                              |       | 0.9 |       | V         |

| V <sub>OD</sub>                    | Differential output voltage                                | $R_L = 100 \Omega$ , single-ended Pk-Pk                                                             | 250   | 400 | 550   | mV        |

| $\Delta V_{OD}$                    | Change in magnitude of VOD for complementary output states | R <sub>L</sub> = 100 Ω                                                                              | -50   |     | 50    | mV        |

| V <sub>ring</sub>                  | Output overshoot and undershoot                            | Percentage of output amplitude VOD                                                                  |       |     | 20%   |           |

| Vos                                | Output AC common mode                                      | $V_{IN, DIFF, PP} = 0.9V, R_L = 100 \Omega, 2 pF$                                                   |       |     | 150   | mVP-P     |

| т                                  | Additive jitter <sup>(1)</sup>                             | $f_{out}$ = 100 MHz, 10k-20M integration bandwidth, $R_L$ = 100 $\Omega$                            |       |     | 200   | fs, rms   |

| T <sub>ADDJIT</sub>                | Additive litter                                            | $f_{out}$ = 400 MHz, 10k-20M integration bandwidth, $R_L$ = 100 $\Omega$                            |       |     | 180   | 15, 11115 |

|                                    |                                                            | ERC = Slow, 20% to 80%, $Z_L = 100\Omega$ , 1pF, $V_{DDOx} = 3.3V$                                  |       | 800 |       |           |

|                                    |                                                            | ERC = Slow, 20% to 80%, $Z_L = 100\Omega$ , 1pF, $V_{DDOx} = 1.8V$                                  |       | 700 |       |           |

| t <sub>R</sub> /t <sub>F</sub>     | Output rise/fall time                                      | ERC = Medium., 20% to 80%, $Z_L = 100\Omega$ , 1pF, $V_{DDOx} = 3.3V$                               | 600   |     |       | ps        |

|                                    |                                                            | ERC = Medium., 20% to 80%, $Z_L = 100\Omega$ , 1pF, $V_{DDOx} = 1.8V$                               |       | 500 |       |           |

|                                    |                                                            | ERC = Fast, 20% to 80%, Z <sub>L</sub> = 100Ω, 1 pF                                                 |       | 300 |       |           |

| ODC                                | Output Duty Cycle                                          | 50/50 Input duty cycle                                                                              | 45%   |     | 55%   |           |

| I <sub>SP</sub><br>I <sub>SN</sub> | Output Short Circuit Current (single ended)                | Shorted to GND                                                                                      | -24   |     | 24    | mA        |

| I <sub>PN</sub>                    | Output Short Circuit Current (differential)                | Complementary outputs shorted together                                                              |       |     | 12    | mA        |

| _                                  | Description Dalay                                          | ERC set to high rate. Input $t_r$ , $t_f > 0.6$ V/ns, $R_L = 100\Omega$ , $V_{DD} = 2.5$ V, $3.3$ V |       |     | 3.3   |           |

| T <sub>DLYO</sub>                  | Propagation Delay                                          | ERC set to high rate. Input $t_r$ , $t_f > 0.6$ V/ns, $R_L = 100\Omega$ , $V_{DD} = 1.8$ V          |       |     | 3.8   | ns        |

| t <sub>SKEW</sub>                  | Skew between outputs                                       | ERC set to high rate. Input $t_r$ , $t_f$ > 0.6 V/ns, Equal VDDOx, $R_L$ = $100\Omega$              |       | 35  | 50    | ps        |

| t <sub>OE</sub>                    | Output enable to stable clock output                       | Pin mode. f <sub>out</sub> = 100 MHz, device in active mode with outputs disabled, OE asserted      |       | 20  |       | μs        |

| t <sub>PD</sub>                    | PD de-asserted to stable clock output                      | Host mode, f <sub>out</sub> = 100 MHz, device in power down mode, PD de-asserted                    |       | 20  |       | μs        |

| t <sub>PU</sub>                    | Time from power applied to stable clock output (2)         | Pin mode, $f_{out}$ = 100 MHz, OE asserted, measured from time $V_{DD}$ is valid to stable output.  |       | 1   |       | ms        |

<sup>(1)</sup>  $t_{Rfin} = t_{Ffin} > 0.6 \text{ V/ns.}$ (2) Parameter depends significantly on power supply design and supply voltage rise time.

## **CLOCK OUTPUT BUFFER CHARACTERISTICS (OUTPUT MODE = HCSL)**

Unless otherwise noted,  $V_{DDOx} = 1.8V$ , 2.5V, 3.3V;  $T_A = -40^{\circ}$ C to 85°C. See Figure 12, Figure 13, and Figure 14. Supporting PCIE gen1, gen2, gen3.

|                      | PARAMETER                                                              | TEST CONDITIONS                                                                                   | MIN   | TYP | MAX  | UNIT       |

|----------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------|-----|------|------------|

| f <sub>OUT</sub>     | Output frequency                                                       |                                                                                                   | 0.008 |     | 400  | MHz        |

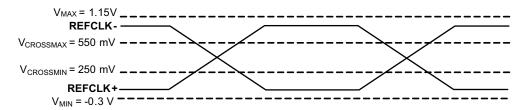

| Vmax                 | Absolute maximum output voltage <sup>(1)</sup>                         | See Figure 3                                                                                      |       |     | 1.15 | V          |

| Vmin                 | Absolute minimum output voltage <sup>(2)</sup>                         | See Figure 3                                                                                      | -0.3  |     |      | V          |

| \/                   | Single ended output voltage –                                          | $R_L$ = single ended to GND = 50 $\Omega$ , $C_L$ = 2pF, VDDOx = 2.5V, 3.3V See Figure 12         | 600   |     |      | m\/        |

| V <sub>OH</sub>      | high <sup>(3)</sup>                                                    | $R_L$ = single ended to GND = 50 $\Omega$ , $C_L$ = 2pF, VDDOx = 1.8V See Figure 12               | 550   |     |      | mV         |

| V <sub>OL</sub>      | Single ended output voltage – low <sup>(3)</sup>                       | $R_L$ = single ended to GND = 50 $\Omega$ , $C_L$ = 2pF, See Figure 12                            |       |     | 150  | mV         |

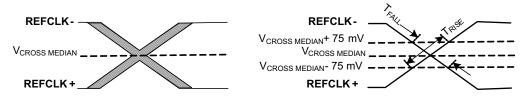

| V <sub>CROSS</sub>   | Output crossing point voltage (3)                                      | See Figure 3                                                                                      | 250   |     | 550  | mV         |

| V <sub>CROSSΔ</sub>  | V <sub>CROSS</sub> Total variation <sup>(3)</sup>                      | See Figure 4                                                                                      |       |     | 140  | mV         |

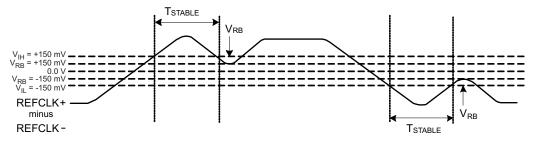

| V <sub>RB</sub>      | Ring back voltage margin <sup>(3)</sup>                                | See Figure 5                                                                                      | -100  |     | 100  | mV         |

| T <sub>STABLE</sub>  | Time before V <sub>RB</sub> is Allowed <sup>(3)</sup> , <sup>(4)</sup> | See Figure 5                                                                                      | 500   |     |      | ps         |

| V <sub>OS</sub>      | Output AC common mode                                                  | $V_{IN,\;DIFF,\;PP}$ = 0.9V, $R_L$ = single ended to GND = 50 $\Omega$ , 2 pF                     |       | 75  | 125  | $mV_{P-P}$ |

| T <sub>jitHCSL</sub> | Additive jitter, input set to HCSL <sup>(5)</sup>                      | f <sub>OUT</sub> = 100 MHz, 10k-20M integration bandwidth.<br>Differential Measurement            |       |     | 380  | fs, rms    |

| T <sub>jitLVDS</sub> | Additive jitter, input set to LVDS <sup>(5)</sup>                      | f <sub>OUT</sub> = 100 MHz, 10k-20M integration bandwidth.<br>Differential Measurement            |       |     | 280  | fs, rms    |

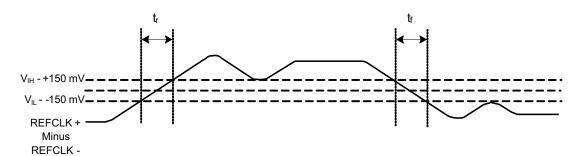

|                      |                                                                        | Slow, +150mV differential, See Figure 6, V <sub>DDOx</sub> = 3.3V                                 |       | 300 |      |            |

|                      |                                                                        | Slow, +150mV differential, See Figure 6, V <sub>DDOx</sub> = 1.8V                                 |       | 230 |      |            |

| $t_R/t_F$            | Output rise/fall time (6)                                              | Med., +150mV differential, See Figure 6, V <sub>DDOx</sub> = 3.3V                                 |       | 240 |      | ps         |

|                      |                                                                        | Med., +150mV differential, See Figure 6, V <sub>DDOx</sub> = 1.8V                                 |       | 180 |      |            |

|                      |                                                                        | Fast, +150mV differential, See Figure 6                                                           |       | 140 |      |            |

| TM <sub>RF</sub>     | Output rise/fall time matching                                         | See Figure 7                                                                                      |       |     | 20%  |            |

| ODC                  | Output duty cycle <sup>(7)</sup>                                       | Differential Measurement, See Figure 8                                                            | 45%   |     | 55%  |            |

| T <sub>DLYO</sub>    | Propagation delay                                                      | ERC set to high rate. Input $t_r$ , $t_f > 0.6$ V/ns, $V_{DD} = 2.5$ V, 3.3V                      |       |     | 3.8  | ns         |

| 52.0                 | , ,                                                                    | ERC set to high rate. Input $t_r$ , $t_f > 0.6$ V/ns, $V_{DD} = 1.8$ V                            |       |     | 4.3  |            |

| t <sub>SKEW</sub>    | Skew between outputs <sup>(8)</sup>                                    | Differential Measurement, Input t <sub>r</sub> , t <sub>f</sub> > 0.6 V/ns                        |       | 35  | 50   | ps         |

| t <sub>OE</sub>      | Output enable to stable clock output                                   | Pin mode, f <sub>out</sub> = 100 MHz, device in active mode with outputs disabled, OE asserted    |       | 2   |      | μs         |

| t <sub>PD</sub>      | PD de-asserted to stable clock output                                  | Host mode, f <sub>out</sub> = 100 MHz, device in power down mode, PD de-asserted                  |       | 15  |      | μs         |

| t <sub>PU</sub>      | Time from power applied to stable clock output (9)                     | Pin mode, $f_{out} = 100$ MHz, OE asserted, measured from time $V_{DD}$ is valid to stable output |       | 1   |      | ms         |

- (1) Single-ended measurement includes overshoot. Measurement is taken at load capacitors C<sub>L</sub> (see Figure 12).

- (2) Single-ended measurement, includes undershoot Measurement is taken at load capacitors  $\bar{C}_L$  (see Figure 12).

- (3) Measurement is taken at load capacitors C<sub>L</sub> (see Figure 12). If VDDOx = 1.8V, the specified minimum V<sub>OH</sub> is 550 mV.

- (4) TSTABLE is the time the differential clock must maintain a minimum ±150 mV differential voltage after rising/falling edges before it is allowed to droop back into the VRB ±100 mV differential range. See Figure 5.

- (5)  $t_{Rfin} = t_{Ffin} \ge 0.6 \text{ V/ns}.$

- (6) Measured from -150 mV to +150 mV on the differential waveform. The signal must be monotonic through the measurement region for rise and fall time. The 300 mV measurement window is centered on the differential zero crossing. Slow is 0.53V/ns, medium is 1.05V/ns, and fast is 2.1V/ns. The PCIe CEM spec. has a window of 0.6V/ns to 4V/ns.

- (7) Assumes input duty cycle = 50%.

- (8) Skew measured between identical output types with identical loads, identical output power supplies, and identical edge rate settings.

- (9) Parameter depends significantly on power supply design and supply voltage rise time.

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

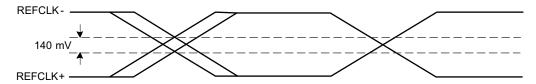

Figure 3. HCSL Crossing Point Voltage

Figure 4. HCSL Variation of VCROSS over all Rising Clock Edges

Figure 5. HCSL Ring Back Margin and Timing

Figure 6. HCSL Rise Fall Time and Edge Speed

Figure 7. HCSL Rise Fall Time Matching

Copyright © 2012–2013, Texas Instruments Incorporated

Figure 8. HCSL Duty Cycle

10

## CLOCK OUTPUT BUFFER ELECTRICAL CHARACTERISTICS (OUTPUT MODE = LVCMOS)

Unless otherwise noted,  $V_{DDOx}$  as shown in Table sections,  $T_A = -40$ °C to 85°C. ERC = Fast. For test configurations, see Figure 15 and Figure 16.

|                                     | PARAMETER                                          | TEST CONDITIONS                                                                                    | MIN    | TYP | MAX | UNIT     |

|-------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-----|-----|----------|

| 3.3V MODE                           | <u> </u>                                           |                                                                                                    | •      |     |     |          |

| f <sub>out</sub>                    | Output frequency range                             |                                                                                                    | 0.0008 |     | 250 | MHz      |

|                                     |                                                    | V <sub>DDOx</sub> = 2.97 V, I <sub>OH</sub> = -0.1 mA (All ERC Settings)                           | 2.9    | 2.9 |     | V        |

|                                     |                                                    | $V_{DDOx} = 2.97 \text{ V}, I_{OH} = -5 \text{ mA (ERC = SLOW)}$                                   | 0.4    |     |     | .,       |

| \ /                                 | LVCMOS High-level output                           | $V_{DDOx} = 2.97 \text{ V}, I_{OH} = -8 \text{ mA (ERC = MED, FAST)}$                              | 2.4    |     |     | V        |

| $V_{OH}$                            | voltage                                            | $V_{DDOx} = 2.97 \text{ V}, I_{OH} = -6 \text{ mA (ERC = SLOW)}$                                   |        | 2.2 |     |          |

|                                     |                                                    | $V_{DDOx} = 2.97 \text{ V}, I_{OH} = -10 \text{ mA (ERC = MED)}$                                   | 2.2    |     |     | V        |

|                                     |                                                    | $V_{DDOx} = 2.97 \text{ V}, I_{OH} = -12 \text{ mA (ERC = FAST)}$                                  |        |     |     |          |

|                                     |                                                    | V <sub>DDOx</sub> = 2.97 V, I <sub>OL</sub> = 0.1 mA (All ERC Settings)                            |        |     | 0.1 | V        |

|                                     |                                                    | $V_{DDOx} = 2.97 \text{ V}, I_{OL} = 5 \text{ mA (ERC = SLOW)}$                                    |        |     | 0.5 | 5 V      |

| \/                                  | LVCMOS Low-level output                            | $V_{DDOx} = 2.97 \text{ V}, I_{OL} = 8 \text{ mA (ERC = MED, FAST)}$                               |        |     | 0.5 |          |

| V <sub>OL</sub>                     | voltage                                            | $V_{DDOx} = 2.97 \text{ V}, I_{OL} = 6 \text{ mA (ERC = SLOW)}$                                    |        |     |     |          |

|                                     |                                                    | $V_{DDOx} = 2.97 \text{ V}, I_{OL} = 10 \text{ mA (ERC = MED)}$                                    |        | 0.8 |     | V        |

|                                     |                                                    | $V_{DDOx} = 2.97 \text{ V}, I_{OL} = 12 \text{ mA (ERC = FAST)}$                                   |        |     |     | <u></u>  |

|                                     | LVCMOS High-level output current                   | $V_{DDOx} = 3.3 \text{ V}, V_{O} = 0.5 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      | -73    |     |     |          |

| I <sub>OH</sub>                     |                                                    | $V_{DDOx} = 3.3 \text{ V}, V_{O} = 1.0 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      | -64    |     | mA  |          |

|                                     |                                                    | V <sub>DDOx</sub> = 3.3 V, V <sub>O</sub> = 1.65 V; T <sub>A</sub> = 25°C                          |        | -49 |     |          |

|                                     |                                                    | $V_{DDOx} = 3.3 \text{ V}, V_{O} = 2.8 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      |        | 78  |     |          |

| $I_{OL}$                            | LVCMOS Low-level output<br>current                 | $V_{DDOx} = 3.3 \text{ V}, V_{O} = 2.3 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      | 72     |     |     | mA       |

|                                     |                                                    | $V_{DDOx} = 3.3 \text{ V}, V_{O} = 1.65 \text{ V}; T_{A} = 25^{\circ}\text{C}$                     |        | 58  |     |          |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay                                  |                                                                                                    |        | 5   |     | ns       |

|                                     |                                                    | ERC = Slow, 20% to 80%, $f_{out}$ = 100 MHz, $C_L$ = 8 pF                                          |        | 1.2 |     | V/ns     |

| t <sub>SLEW-RATE</sub>              | Output rise/fall slew rate                         | ERC = Medium 20% to 80%, $f_{out}$ = 100 MHz, $C_L$ = 8 pF                                         |        | 3   |     | <u> </u> |

|                                     |                                                    | ERC = Fast, 20% to 80%, f <sub>out</sub> = 250 MHz, C <sub>L</sub> = 8 pF                          |        | 6   |     | <u> </u> |

| t <sub>jitt-add</sub>               | Additive Jitter                                    | f <sub>OUT</sub> = 100 MHz, 10k-20M integration bandwidth                                          |        |     | 280 | fs       |

| t <sub>sk(o)</sub>                  | Output Skew <sup>(1)</sup>                         |                                                                                                    | 90     |     | ps  |          |

| odc                                 | Output Duty Cycle (2), (3)                         | f <sub>OUT</sub> = 100 MHz; Pdiv = 1                                                               | 45%    |     | 55% |          |

| t <sub>OE</sub>                     | Output enable to stable clock output               | Pin mode. f <sub>out</sub> = 100 MHz, device in active mode with outputs disabled, OE asserted     | 2      |     | μs  |          |

| t <sub>PD</sub>                     | PD de-asserted to stable clock output              | Host mode, f <sub>out</sub> = 100 MHz, device in power down mode, PD de-asserted                   | 10     |     | μs  |          |

| t <sub>PU</sub>                     | Time from power applied to stable clock output (4) | Pin mode, $f_{out}$ = 100 MHz, OE asserted, measured from time $V_{DD}$ is valid to stable output. |        | 1   |     | ms       |

The  $t_{sk(o)}$  specification is only valid for equal loading with identical edge rates and output supply voltages.. Assumes 50% duty cycle at the input(s) odc depends on output rise and fall time  $(t_R/t_F)$ .

Parameter depends significantly on power supply design and supply voltage rise time.

## CLOCK OUTPUT BUFFER ELECTRICAL CHARACTERISTICS (OUTPUT MODE = LVCMOS) (Continued)

Unless otherwise noted,  $V_{DDOx}$  as shown in Table sections,  $T_A = -40^{\circ}\text{C}$  to 85°C. ERC = Fast. For test configurations, see Figure 15 and Figure 16.

|                                     | PARAMETER                                          | TEST CONDITIONS                                                                                                  | MIN               | TYP | MAX | UNIT |

|-------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|------|

| 2.5V MODE                           | Ē                                                  |                                                                                                                  | 1                 |     | ,   |      |

| f <sub>out</sub>                    | Output frequency range                             |                                                                                                                  | 0.00<br>08        |     | 250 | MHz  |

|                                     |                                                    | V <sub>DDOx</sub> = 2.375 V, I <sub>OH</sub> = -0.1 mA (All ERC Settings)                                        | 2.2               |     |     |      |

|                                     |                                                    | $V_{DDOx} = 2.375 \text{ V}, I_{OH} = -4 \text{ mA (ERC = SLOW)}$                                                | 4.7               | 4.7 |     | .,   |

| $V_{OH}$                            | LVCMOS High-level output voltage                   | $V_{DDOx} = 2.375 \text{ V}, I_{OH} = -6 \text{ mA (ERC = MED, FAST)}$                                           | 1.7               |     |     | V    |

|                                     | Voltage                                            | $V_{DDOx} = 2.375 \text{ V}, I_{OH} = -5 \text{ mA (ERC = SLOW)}$                                                | 4.0               |     |     | .,   |

|                                     |                                                    | $V_{DDOx} = 2.375 \text{ V}, I_{OH} = -8 \text{ mA (ERC = MED, FAST)}$                                           | 1.6               |     |     | V    |

|                                     |                                                    | V <sub>DDOx</sub> = 2.375 V, I <sub>OL</sub> = 0.1 mA (All ERC Settings)                                         |                   |     | 0.1 | V    |

|                                     |                                                    | $V_{DDOx} = 2.375 \text{ V}, I_{OH} = 4 \text{ mA (ERC = SLOW)}$                                                 |                   |     | 0.5 | V    |

| $V_{OL}$                            | LVCMOS Low-level output voltage                    | $V_{DDOx} = 2.375 \text{ V}, I_{OH} = 6 \text{ mA (ERC = MED, FAST)}$                                            |                   |     |     |      |

|                                     | Voltage                                            | $V_{DDOx} = 2.375 \text{ V}, I_{OH} = 5 \text{ mA (ERC = SLOW)}$                                                 |                   |     | 0.7 | V    |

|                                     |                                                    | V <sub>DDOx</sub> = 2.375 V, I <sub>OL</sub> = 10 mA (ERC = MED, FAST)                                           |                   |     |     |      |

|                                     | LVCMOS High-level output current                   | V <sub>DDOx</sub> = 2.5 V, V <sub>O</sub> = 0.5 V; T <sub>A</sub> = 25°C                                         | -45<br>-39<br>-32 |     |     |      |

| I <sub>OH</sub>                     |                                                    | $V_{DDOx} = 2.5 \text{ V}, V_{O} = 0.9 \text{ V}; T_{A} = 25^{\circ}\text{C}$                                    |                   |     | mA  |      |

|                                     |                                                    | $V_{DDOx} = 2.5 \text{ V}, V_{O} = 1.25 \text{ V}; T_{A} = 25^{\circ}\text{C}$                                   |                   |     |     |      |

|                                     | LVCMOS Low-level output current                    | $V_{DDOx} = 2.5 \text{ V}, V_{O} = 2.0 \text{ V}; T_{A} = 25^{\circ}\text{C}$                                    | 50                |     |     |      |

| $I_{OL}$                            |                                                    | output $V_{DDOx} = 2.5 \text{ V}, V_{O} = 1.65 \text{ V}; T_{A} = 25^{\circ}\text{C}$ 47                         |                   |     | mA  |      |

|                                     |                                                    | $V_{DDOx} = 2.5 \text{ V}, V_{O} = 1.25 \text{ V}; T_{A} = 25^{\circ}\text{C}$                                   | 40                |     |     |      |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay                                  |                                                                                                                  |                   | 5.5 |     | ns   |

|                                     |                                                    | ERC = Slow, 20% to 80%, f <sub>out</sub> = 100 MHz, C <sub>L</sub> = 8 pF                                        |                   | 8.0 |     |      |

| t <sub>SLEW-RATE</sub>              | Output rise/fall slew rate                         | ERC = Medium 20% to 80%, f <sub>out</sub> = 100 MHz, C <sub>L</sub> = 8 pF                                       |                   | 1.4 | 1.4 |      |

|                                     |                                                    | ERC = Fast, 20% to 80%, f <sub>out</sub> = 250 MHz, C <sub>L</sub> = 8 pF                                        | 4                 |     |     |      |

| t <sub>jitt-add</sub>               | Additive jitter                                    | f <sub>OUT</sub> = 100 MHz, 10k-20M integration bandwidth                                                        |                   |     | 280 | fs   |

| t <sub>sk(o)</sub>                  | Output skew <sup>(1)</sup>                         |                                                                                                                  |                   |     | 90  | ps   |

| odc                                 | Output Duty Cycle (2)(3)                           | f <sub>OUT</sub> = 100 MHz; Pdiv = 1                                                                             | 45%               |     | 55% |      |

| t <sub>OE</sub>                     | Output enable to stable clock output               | Pin mode. f <sub>out</sub> = 100 MHz, device in active mode with outputs disabled, OE asserted                   | 2                 |     | μs  |      |

| t <sub>PD</sub>                     | PD de-asserted to stable clock output              | Host mode, f <sub>out</sub> = 100 MHz, device in power down mode, PD de-asserted                                 |                   | 10  |     | μs   |

| t <sub>PU</sub>                     | Time from power applied to stable clock output (4) | Pin mode, f <sub>out</sub> = 100 MHz, OE asserted, measured from time V <sub>DD</sub> is valid to stable output. |                   | 1   |     | ms   |

<sup>(1)</sup> The  $t_{sk(0)}$  specification is only valid for equal loading with identical edge rates and output supply voltages.. (2) Assumes 50% duty cycle at the input(s)

odc depends on output rise and fall time (t<sub>R</sub>/t<sub>F</sub>).

Parameter depends significantly on power supply design and supply voltage rise time.

## CLOCK OUTPUT BUFFER ELECTRICAL CHARACTERISTICS (OUTPUT MODE = LVCMOS) (Continued)

Unless otherwise noted,  $V_{DDOx}$  as shown in Table sections,  $T_A = -40$ °C to 85°C. ERC = Fast. For test configurations, see Figure 15 and Figure 16.

|                           | PARAMETER                                                     | TEST CONDITIONS                                                                                    | MIN      | TYP | MAX | UNITS |

|---------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------|-----|-----|-------|

| 1.8V MODE                 | <u> </u>                                                      |                                                                                                    | •        |     | ',  |       |

| f <sub>out</sub>          | Output Frequency Range                                        |                                                                                                    | 0.0008   |     | 250 | MHz   |

|                           |                                                               | V <sub>DDOx</sub> = 1.7 V, I <sub>OH</sub> = -0.1 mA (All ERC Settings)                            | 1.6      |     |     |       |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OH} = -1.5 \text{ mA (ERC = SLOW)}$                                  |          |     |     |       |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OH} = -3 \text{ mA (ERC = MED)}$                                     | 1.4      | 1.4 |     | V     |

| $V_{OH}$                  | LVCMOS High-level output voltage                              | $V_{DDOx} = 1.7 \text{ V}, I_{OH} = -4 \text{ mA (ERC = FAST)}$                                    |          |     |     |       |

|                           | vollage                                                       | $V_{DDOx} = 1.7 \text{ V}, I_{OH} = -3 \text{ mA (ERC = SLOW)}$                                    |          |     |     |       |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OH} = -5 \text{ mA (ERC = MED)}$                                     | 1.1      |     |     | V     |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OH} = -8 \text{ mA (ERC = FAST)}$                                    |          |     |     |       |

|                           |                                                               | V <sub>DDOx</sub> = 1.7 V, I <sub>OL</sub> = 0.1 mA (All ERC Settings)                             |          |     | 0.1 | V     |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OL} = 2 \text{ mA (ERC = SLOW)}$                                     |          |     |     | V     |

|                           | LVCMOS Low-level output voltage                               | $V_{DDOx} = 1.7 \text{ V}, I_{OL} = 3 \text{ mA (ERC = MED)}$                                      |          |     | 0.3 |       |

| $V_{OL}$                  |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OL} = 4 \text{ mA (ERC = FAST)}$                                     |          |     |     |       |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OL} = 3 \text{ mA (ERC = SLOW)}$                                     |          |     |     | V     |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OL} = 5 \text{ mA (ERC = MED)}$                                      | 0.6      |     | 0.6 |       |

|                           |                                                               | $V_{DDOx} = 1.7 \text{ V}, I_{OL} = 8 \text{ mA (ERC} = \text{FAST)}$                              |          |     |     |       |

| Land                      | LVCMOS High-level output                                      | $V_{DDOx} = 1.8 \text{ V}, V_{O} = 0.5 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      | -23      |     | mA  |       |

| I <sub>OH</sub>           | current                                                       | $V_{DDOx} = 1.8 \text{ V}, V_{O} = 0.9 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      |          | -18 |     | IIIA  |

|                           | LVCMOS Low-level output current                               | $V_{DDOx} = 1.8 \text{ V}, V_{O} = 1.4 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      | 27<br>23 |     |     | mA    |

| l <sub>OL</sub>           |                                                               | $V_{DDOx} = 1.8 \text{ V}, V_{O} = 0.9 \text{ V}; T_{A} = 25^{\circ}\text{C}$                      |          |     | mA  |       |

| $t_{\rm PLH},t_{\rm PHL}$ | Propagation delay                                             |                                                                                                    |          | 6.8 |     | ns    |

|                           |                                                               | ERC = Slow, 20% to 80%, $f_{out}$ = 100 MHz, $C_L$ = 8 pF                                          |          | 0.5 |     |       |

| t <sub>SLEW-RATE</sub>    | Output rise/fall slew rate                                    | ERC = Medium 20% to 80%, $f_{out}$ = 100 MHz, $C_L$ = 8 pF                                         |          | 0.8 |     | V/ns  |

|                           |                                                               | ERC = Fast, 20% to 80%, $f_{out}$ = 250 MHz, $C_L$ = 8 pF                                          | 2.7      |     |     |       |

| t <sub>jitt-add</sub>     | Additive jitter                                               | f <sub>OUT</sub> = 100 MHz, 10k-20M integration bandwidth                                          |          |     | 350 | fs    |

| t <sub>sk(o)</sub>        | Output skew <sup>(1)</sup>                                    |                                                                                                    | 130      |     | ps  |       |

| odc                       | Output duty cycle (2), (3)                                    | f <sub>OUT</sub> = 100 MHz; Pdiv = 1, ERC = MED, FAST                                              | 45%      |     | 55% | -     |

| t <sub>OE</sub>           | Output enable to stable clock output                          | Pin mode. f <sub>out</sub> = 100 MHz, device in active mode with outputs disabled, OE asserted     | 2        |     | μs  |       |

| t <sub>PD</sub>           | PD de-asserted to stable clock output                         | Host mode, f <sub>out</sub> = 100 MHz, device in power down mode, PD de-asserted                   |          | 10  |     | μs    |

| t <sub>PU</sub>           | Time from power applied to stable clock output <sup>(4)</sup> | Pin mode, $f_{out}$ = 100 MHz, OE asserted, measured from time $V_{DD}$ is valid to stable output. |          | 1   |     | ms    |

The  $t_{sk(o)}$  specification is only valid for equal loading with identical edge rates and output supply voltages. Assumes 50% duty cycle at the input(s)

<sup>(3)</sup> odc depends on output rise and fall time  $(t_R/t_F)$ .

Parameter depends significantly on power supply design and supply voltage rise time.

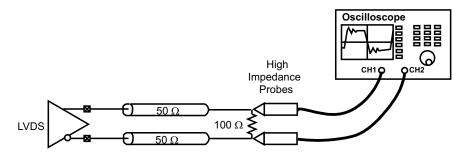

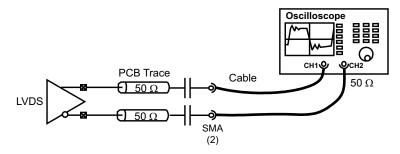

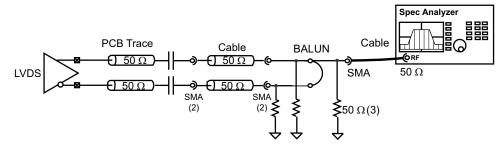

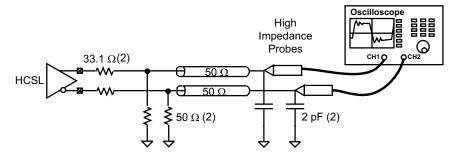

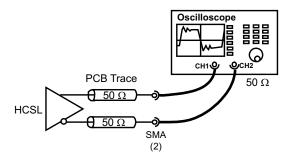

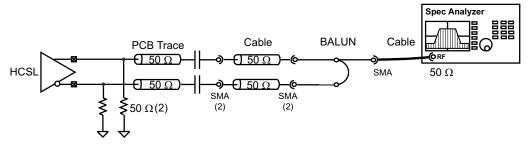

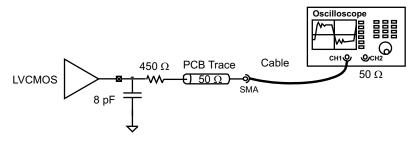

#### **TEST CONFIGURATIONS**

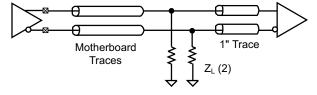

Figure 9. CDCUN1208LP LVDS Output - Test Setup

Figure 10. CDCUN1208LP LVDS Output - Propagation Delay/Skew Measurement Setup

Figure 11. CDCUN1208LP LVDS Output - Phase Noise/Jitter Measurement Setup

Figure 12 shows the configuration used to measure the HCSL buffer characteristics. Either single ended probes with math or differential probes can be used for differential measurements. The  $50\Omega$  differential trace length is up to 15 inches.

Figure 12. CDCUN1208LP HCSL Output - Measurement Configuration with Load

Figure 13. CDCUN1208LP HCSL Output - Propagation Delay/Skew Measurement

Figure 14. CDCUN1208LP HCSL Output - Phase Noise/Jitter Measurement Configuration

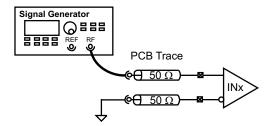

Figure 15. CDCUN1208LP LVCMOS Output - Measurement Configuration

Figure 16. CDCUN1208LP LVCMOS Output - Phase Noise/Jitter Measurement Setup

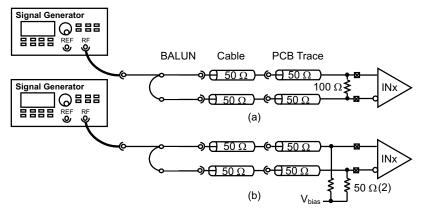

Figure 17. CDCUN1208LP Universal Input - Differential Mode Measurement Setup

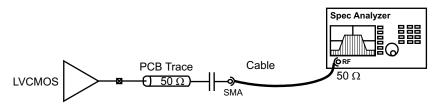

Figure 18. CDCUN1208LP Universal Input - Single-Ended Mode Measurement Setup

Figure 19. CDCUN1208LP Power Consumption Measurement Setup

#### PERFORMANCE CHARACTERISTICS

3.5 3.5 3.5 2.5 VDDOx = 1.8 V VDDOx = 1.8 V VDDOx = 1.8 V 0.5 0 10 20 30 40 50 60 70 80 I<sub>Ot</sub> - Low Level Output Current - mA

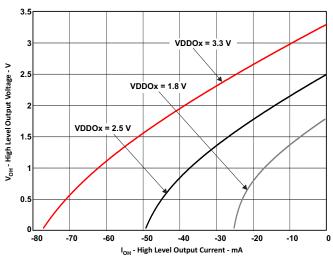

Figure 20. High Level Output Voltage vs. Current - LVCMOS Mode

Figure 21. Low Level Output Voltage vs. Current - LVCMOS Mode

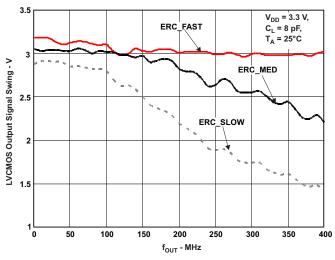

Figure 22. CDCUN1208LP LVCMOS Signal Swing Characteristics (3.3V Mode)

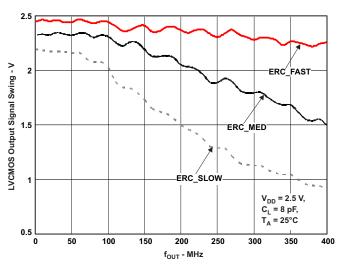

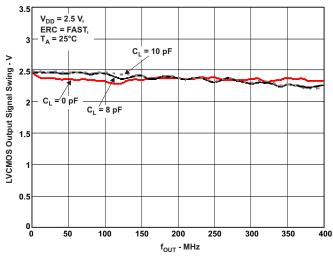

Figure 23. CDCUN1208LP LVCMOS Signal Swing Characteristics (2.5V Mode)

V<sub>DD</sub> = 3.3 V, ERC = FAST, T<sub>A</sub> = 25°C

C<sub>L</sub> = 10 pF

C<sub>L</sub> = 0 pF

1.5

0

50

100

150

200

250

300

350

400

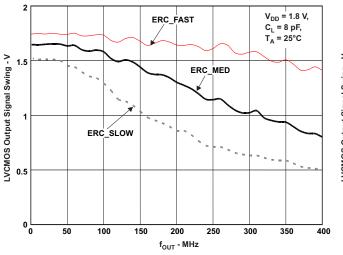

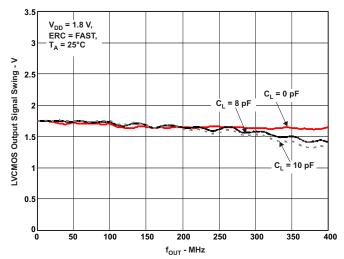

Figure 24. CDCUN1208LP LVCMOS Signal Swing Characteristics (1.8V Mode)

Figure 25. CDCUN1208LP LVCMOS Capacitive Load Drive Characteristics (3.3V Mode)

Figure 26. CDCUN1208LP LVCMOS Capacitive Load Drive Characteristics (2.5V Mode)

Figure 27. CDCUN1208LP LVCMOS Capacitive Load Drive Characteristics (1.8V Mode)

#### **FUNCTIONAL DESCRIPTION**

#### **DEVICE CONTROL USING CONFIGURATION PINS**

Figure 28 illustrates and Table 2 lists the CDCUN1208LP device settings using the configuration pins. Some pins sense three different states (HIGH, LOW, OPEN) according to Figure 28 and DIGITAL INPUT ELECTRICAL CHARACTERISTICS – OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), MODE. The device samples the state of the pins at power up and configures the device accordingly. Certain pins including INSEL and OE are sampled continuously; thus changes of state of INSEL or OE controls the device instantly.

Figure 28. CDCUN1208LP Pin Configuration Overview

Table 2. CDCUN1208LP Pin Configuration Summary

| PIN NAME    | PIN NUMBER                  | DEFINITION                  | DEVICE CONFIGURATION DETAILS |  |  |  |  |

|-------------|-----------------------------|-----------------------------|------------------------------|--|--|--|--|

| DEVICE OUT  | DEVICE OUTPUTS              |                             |                              |  |  |  |  |

| OTTP        | OTTP 19 Output Type Setting |                             | See Table 3                  |  |  |  |  |

| ERC         | 31                          | Edge Rate Control           | See Table 4                  |  |  |  |  |

| OE          | 32                          | Device Global Output Enable | See Table 5                  |  |  |  |  |

| DEVICE INPU | DEVICE INPUTS               |                             |                              |  |  |  |  |

| ITTP        | TTP 8 Input Type Setting    |                             | See Table 6                  |  |  |  |  |

| DIVIDE      | 1                           | IN2 Input Divider Control   | See Table 7                  |  |  |  |  |

| INSEL       | 2                           | Input Multiplexer Setting   | See Table 8                  |  |  |  |  |

Copyright © 2012–2013, Texas Instruments Incorporated

#### **Configuration of Output Type (OTTP)**

Table 3 shows how to set the output buffer type using the OTTP pin. This setting affects all device outputs equally. Certain combinations of output buffers include a dedicated power supply pin which must be properly bypassed. If the device output configuration is set to LVCMOS, then the supply voltage applied establishes the switching thresholds corresponding to the supply provided according to CLOCK OUTPUT BUFFER ELECTRICAL CHARACTERISTICS (OUTPUT MODE = LVCMOS). For example, if OUT1 and OUT2 are supplied with a 1.8V power supply via the VDDO1 pin, the switching thresholds are set to the 1.8V logic domain. The system may have other logic supplies (1.8V, 2.5V, or 3.3V) connected to the device on different output buffer supply domains simultaneously. This enables the device to clock devices operating on different supplies without the need for external logic level translation buffers. The CDCUN1208LP automatically adjusts the switching thresholds corresponding to these common logic power supply voltages. For more information regarding the power supplies for the output section, see DEVICE POWER SUPPLY CONNECTIONS AND SEQUENCING.

Table 3. CDCUN1208LP Pin Configuration of Output Type

| OTTP (Pin 19) | OUTPUT TYPE |  |

|---------------|-------------|--|

| LOW           | LVDS        |  |

| HIGH          | HCSL        |  |

| OPEN          | LVCMOS      |  |

#### Configuration of Edge Rate Control (ERC)

The CDCUN1208LP supports Edge Rate Control (ERC) used to tailor jitter and EMI performance from device outputs. Table 4 shows the edge rate control setting. This setting affects all device outputs equally. Each edge rate setting is unique to the output buffer type selected as described in CLOCK OUTPUT BUFFER CHARACTERISTICS (OUTPUT MODE = LVDS), CLOCK OUTPUT BUFFER CHARACTERISTICS (OUTPUT MODE = LVCMOS), and CLOCK OUTPUT BUFFER ELECTRICAL CHARACTERISTICS (OUTPUT MODE = LVCMOS).

Table 4. CDCUN1208LP Pin Configuration of Output Edge Rate

| ERC (Pin 31) | OUTPUT EDGE RATE |

|--------------|------------------|

| LOW          | SLOW             |

| HIGH         | MEDIUM           |

| OPEN         | FAST             |

#### **Control of Output Enable (OE)**

Table 5 shows how the output enable pin controls the device outputs. The OE pin is sampled continuously so that the application may turn on/off the output buffers at any time.

Table 5. CDCUN1208LP Pin Control of Output Enable

| OE (Pin 32) | OUTPUT ENABLE           |  |

|-------------|-------------------------|--|

| LOW         | DISABLED in Tri-State   |  |

| HIGH        | ENABLED                 |  |

| OPEN        | RESERVED <sup>(1)</sup> |  |

(1) Leaving the Output Enable pin OPEN will cause the CDCUN1208LP to malfunction. This pin must be driven high or low at all times

## **INPUT PORTS (IN1, IN2)**

#### **Configuration of the Input Type (ITTP)**

Table 6 describes how to set the input buffers to the appropriate switching levels using the ITTP pin. For proper input termination, see Figure 44.

Table 6. CDCUN1208LP Pin Control of Input Type (ITTP)

| ITTP (Pin 8) | ITTP SETTING |  |

|--------------|--------------|--|

| LOW          | LVDS         |  |

| HIGH         | HCSL         |  |

| OPEN         | LVCMOS       |  |

## Configuration of the IN2 Divider (INDIV)

Table 7 describes how to set the input divider using the DIVIDE pin. If the /8 setting is desired, then this feature is accessed via the host configuration method only refer to section DEVICE CONTROL USING THE HOST INTERFACE.

Table 7. CDCUN1208LP Pin Control of INDIV Divider

| DIVIDE (Pin 1) | INDIV DIVIDER SETTING |

|----------------|-----------------------|

| LOW            | /2                    |

| HIGH           | /4                    |

| OPEN           | /1                    |

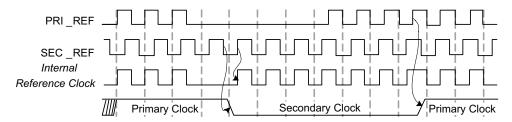

#### **SMART INPUT MULTIPLEXER (INMUX)**

The Smart Multiplexer supports manual and automatic switching between IN1 and IN2. If enabled, the Smart Multiplexer switches automatically between clock inputs based on a prioritization scheme shown in Table 8. If using the Smart Multiplexer Auto Mode, the frequencies of the clocks applied to the smart multiplexer via IN1 and IN2 (via the divider) may differ by up to 20%. The phase relationship between clock inputs has no restriction. The smart multiplexer includes signal conditioning that provides glitch suppression. (1)

Upon the detection of a loss of signal on the input with higher priority, the smart multiplexer switches over to the other clock input on the first incoming rising edge. During this switching operation, the output of the smart multiplexer is low. Upon restoration of the higher priority clock, the smart multiplexer waits until it detects four complete cycles from the higher priority clock prior to switching the output of the smart multiplexer back to the higher priority clock. During this switching operation, the output of the smart multiplexer remains high until the next falling edge as shown in Figure 29.

#### Pin Configuration of the Smart Input Multiplexer (INMUX)

Table 8 shows how to control the Smart Input Multiplexer. In Pin Configuration mode, the INSEL pin is sampled continuously so that the application may select the input clock at any time.

Table 8. Control of INMUX via the INSEL Pin

| INSEL(Pin 2)                                                                                                                                       | IN1 BUFFER SETTING                   | IN2 BUFFER SETTING           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------|--|

| LOW                                                                                                                                                | ON and selected by INSEL Multiplexer | OFF                          |  |

| HIGH                                                                                                                                               | OFF                                  | ON and selected by INSEL Mux |  |

| OPEN Smart Multiplexer selects input. IN1 is the primary input (it has the highest priority, therefore if it is the smart multiplexer selects IN1) |                                      |                              |  |

Figure 29. CDCUN1208LP Smart Multiplexer Operation

(1) This implementation does not implement a phase build-out mechanism; rather, analog filtering insuring a smooth transition at device outputs.

Product Folder Links : CDCUN1208LP

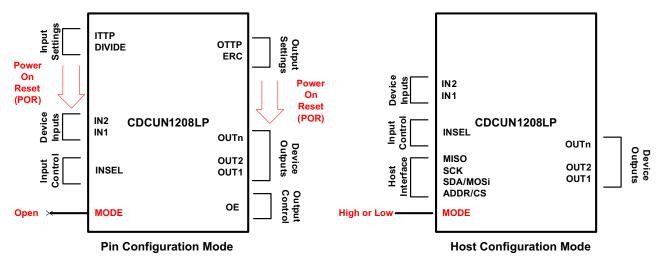

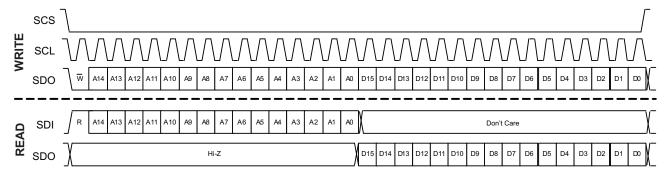

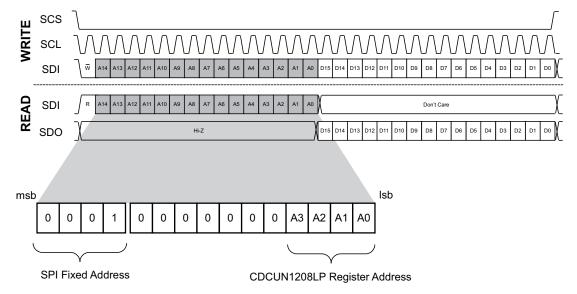

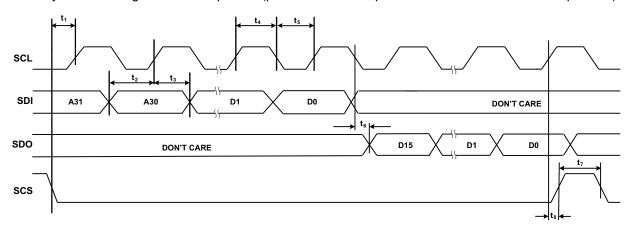

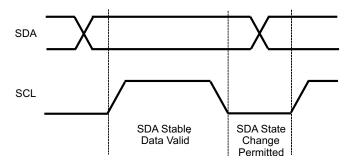

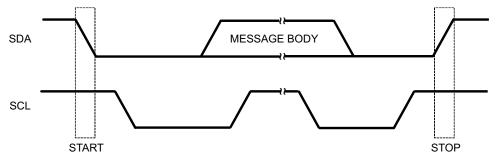

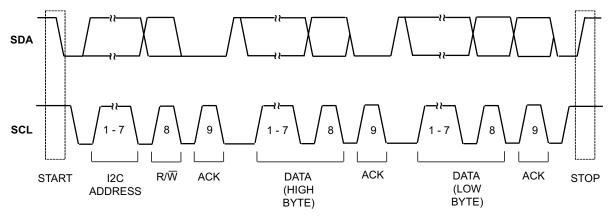

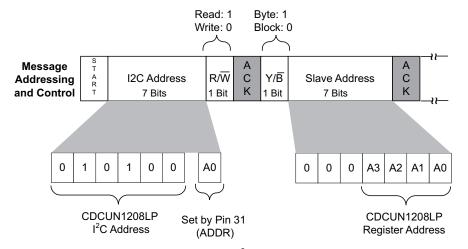

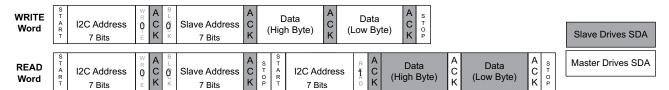

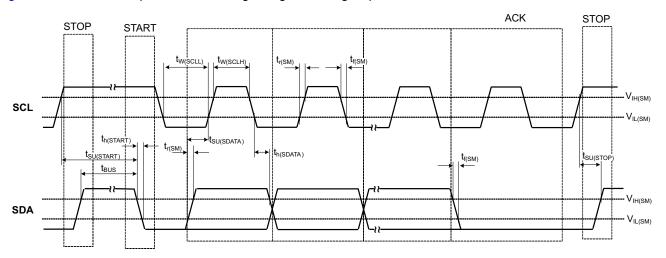

#### DEVICE CONTROL USING THE HOST INTERFACE

Host configuration mode affords a greater degree of flexibility. Unlike pin configuration mode in which the pin settings affect the entire device, host configuration mode enables the user to apply different settings to each input and output port as depicted in Figure 30. This includes the ability to mix and match output type, edge rate control, and output enable settings. The host interface is enabled/selected by strapping the MODE pin either high (for I<sup>2</sup>C) or low (for SPI) and resetting the device. Additional device features are accessible only through the host interface as well. For instance, the user can configure the input divider (IDIV) to /8 in host configuration mode only. Additionally, the system can power down the device through device registers.

#### **OE and INSEL in Host Configuration Mode**