**TEXAS INSTRUMENTS-PRODUCTION DATA**

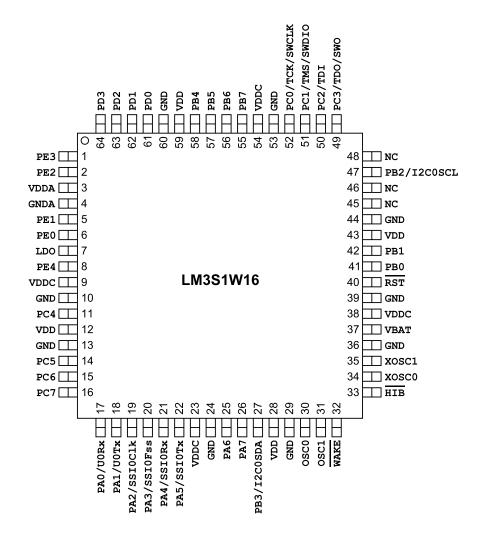

# Stellaris® LM3S1W16 Microcontroller

DATA SHEET

### Copyright

Copyright © 2007-2012 Texas Instruments Incorporated All rights reserved. Stellaris and StellarisWare® are registered trademarks of Texas Instruments Incorporated. ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property of others.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

A Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Texas Instruments Incorporated

108 Wild Basin, Suite 350

Austin, TX 78746

http://www.ti.com/stellaris

http://www-k.ext.ti.com/sc/technical-support/product-information-centers.htm

## **Table of Contents**

| Revision His  | story                                                      | 25 |

|---------------|------------------------------------------------------------|----|

| About This I  | Document                                                   | 33 |

| Audience      |                                                            | 33 |

| About This Ma | anual                                                      | 33 |

|               | ments                                                      |    |

| Documentation | n Conventions                                              | 34 |

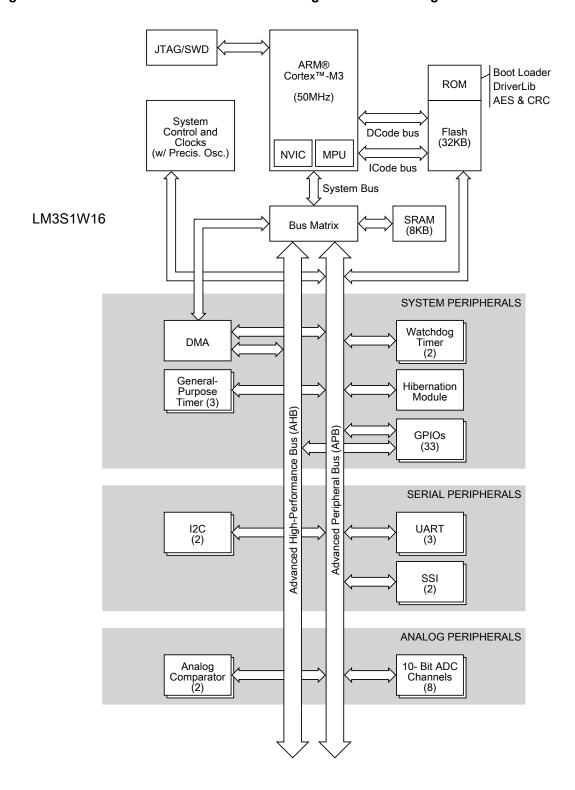

| 1             | Architectural Overview                                     | 36 |

| 1.1           | Overview                                                   | 36 |

| 1.2           | Target Applications                                        |    |

| 1.3           | Features                                                   |    |

| 1.3.1         | ARM Cortex-M3 Processor Core                               |    |

| 1.3.2         | On-Chip Memory                                             |    |

| 1.3.3         | Serial Communications Peripherals                          |    |

| 1.3.4         | System Integration                                         |    |

| 1.3.5         | Analog                                                     |    |

| 1.3.6         | JTAG and ARM Serial Wire Debug                             |    |

| 1.3.7         | Packaging and Temperature                                  |    |

| 1.4           | Hardware Details                                           | 52 |

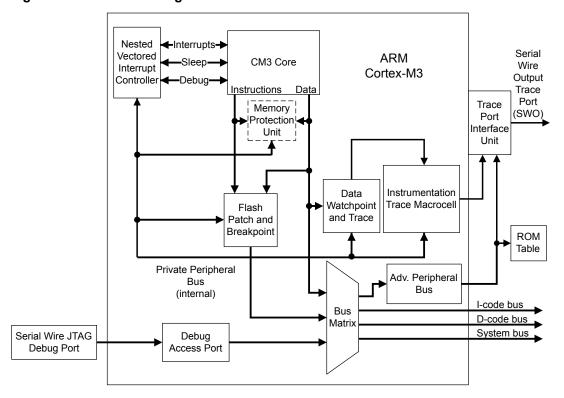

| 2             | The Cortex-M3 Processor                                    |    |

| 2.1           | Block Diagram                                              | 54 |

| 2.2           | Overview                                                   |    |

| 2.2.1         | System-Level Interface                                     | 55 |

| 2.2.2         | Integrated Configurable Debug                              | 55 |

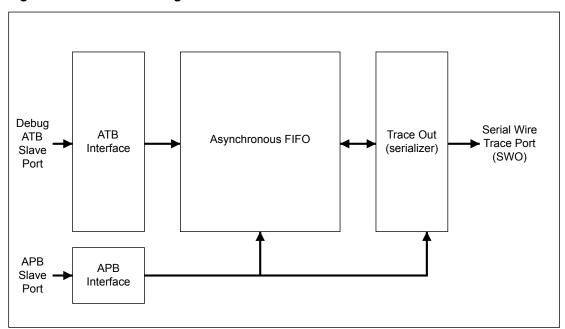

| 2.2.3         | Trace Port Interface Unit (TPIU)                           |    |

| 2.2.4         | Cortex-M3 System Component Details                         |    |

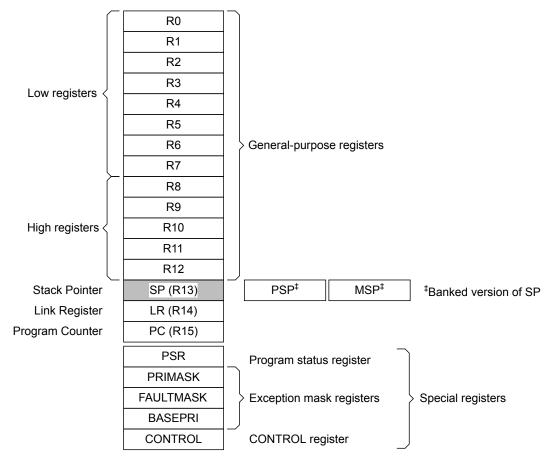

| 2.3           | Programming Model                                          |    |

| 2.3.1         | Processor Mode and Privilege Levels for Software Execution |    |

| 2.3.2         | Stacks                                                     |    |

| 2.3.3         | Register Map                                               |    |

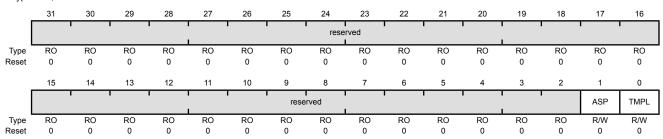

| 2.3.4         | Register Descriptions                                      |    |

| 2.3.5         | Exceptions and Interrupts                                  |    |

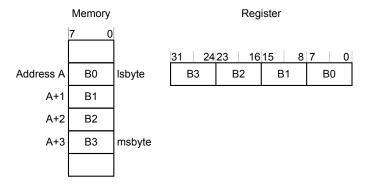

| 2.3.6         | Data Types                                                 |    |

| 2.4           | Memory Model                                               |    |

| 2.4.1         | Memory Regions, Types and Attributes                       |    |

| 2.4.2         | Memory System Ordering of Memory Accesses                  |    |

| 2.4.3         | Behavior of Memory Accesses                                |    |

| 2.4.4         | Software Ordering of Memory Accesses                       |    |

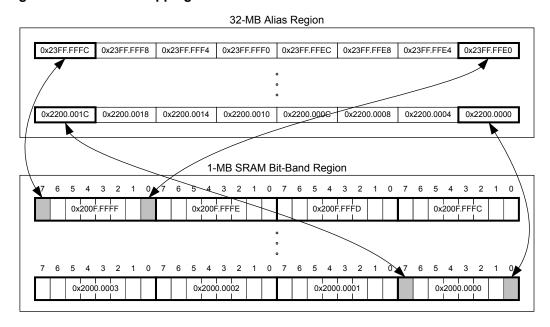

| 2.4.5         | Bit-Banding                                                |    |

| 2.4.6         | Data Storage                                               |    |

| 2.4.7         | Synchronization Primitives                                 |    |

| 2.5           | Exception Model                                            |    |

| 2.5.1         | Exception States                                           |    |

| 2.5.2         | Exception Types                                            |    |

| 2.5.3         | Exception Handlers                                         |    |

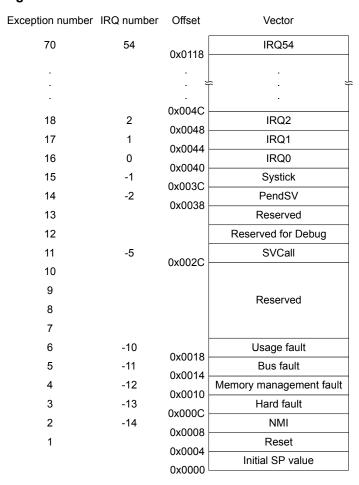

| 2.5.4         | Vector Table                                               | 84 |

|                                                                                                                                                           | Exception Priorities                                                                                                                                                                                                                                                                                                                                                                                   |                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2.5.6                                                                                                                                                     | Interrupt Priority Grouping                                                                                                                                                                                                                                                                                                                                                                            | 86                       |

| 2.5.7                                                                                                                                                     | Exception Entry and Return                                                                                                                                                                                                                                                                                                                                                                             | 86                       |

| 2.6                                                                                                                                                       | Fault Handling                                                                                                                                                                                                                                                                                                                                                                                         | 88                       |

| 2.6.1                                                                                                                                                     | Fault Types                                                                                                                                                                                                                                                                                                                                                                                            | 88                       |

| 2.6.2                                                                                                                                                     | Fault Escalation and Hard Faults                                                                                                                                                                                                                                                                                                                                                                       | 89                       |

| 2.6.3                                                                                                                                                     | Fault Status Registers and Fault Address Registers                                                                                                                                                                                                                                                                                                                                                     | 90                       |

| 2.6.4                                                                                                                                                     | Lockup                                                                                                                                                                                                                                                                                                                                                                                                 | 90                       |

| 2.7                                                                                                                                                       | Power Management                                                                                                                                                                                                                                                                                                                                                                                       | 90                       |

| 2.7.1                                                                                                                                                     | Entering Sleep Modes                                                                                                                                                                                                                                                                                                                                                                                   | 90                       |

| 2.7.2                                                                                                                                                     | Wake Up from Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                | 91                       |

| 2.8                                                                                                                                                       | Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                | 92                       |

| 3                                                                                                                                                         | Cortex-M3 Peripherals                                                                                                                                                                                                                                                                                                                                                                                  | 95                       |

| 3.1                                                                                                                                                       | Functional Description                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 3.1.1                                                                                                                                                     | System Timer (SysTick)                                                                                                                                                                                                                                                                                                                                                                                 | 95                       |

| 3.1.2                                                                                                                                                     | Nested Vectored Interrupt Controller (NVIC)                                                                                                                                                                                                                                                                                                                                                            |                          |

| 3.1.3                                                                                                                                                     | System Control Block (SCB)                                                                                                                                                                                                                                                                                                                                                                             |                          |

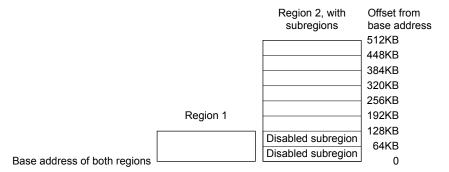

| 3.1.4                                                                                                                                                     | Memory Protection Unit (MPU)                                                                                                                                                                                                                                                                                                                                                                           |                          |

| 3.2                                                                                                                                                       | Register Map                                                                                                                                                                                                                                                                                                                                                                                           | 103                      |

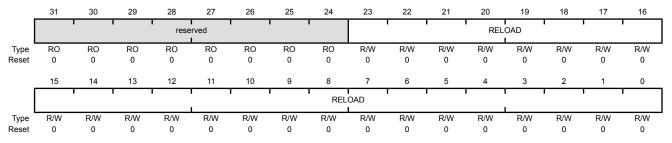

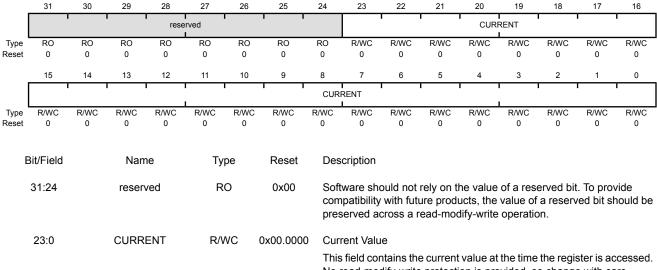

| 3.3                                                                                                                                                       | System Timer (SysTick) Register Descriptions                                                                                                                                                                                                                                                                                                                                                           |                          |

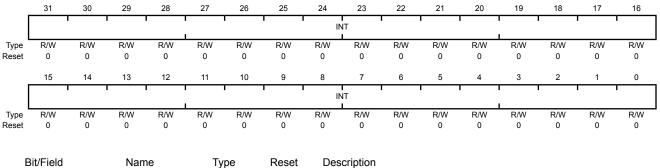

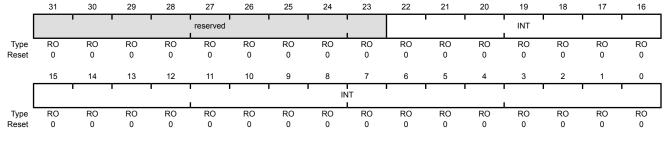

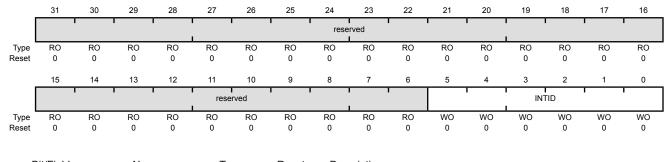

| 3.4                                                                                                                                                       | NVIC Register Descriptions                                                                                                                                                                                                                                                                                                                                                                             |                          |

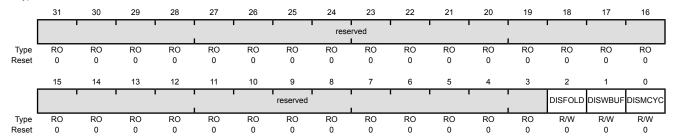

| 3.5                                                                                                                                                       | System Control Block (SCB) Register Descriptions                                                                                                                                                                                                                                                                                                                                                       |                          |

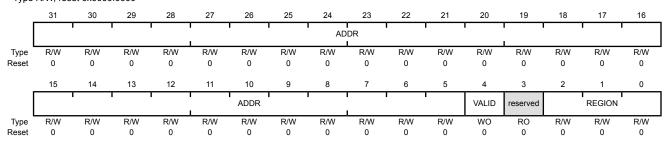

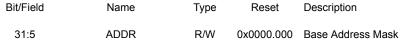

| 3.6                                                                                                                                                       | Memory Protection Unit (MPU) Register Descriptions                                                                                                                                                                                                                                                                                                                                                     |                          |

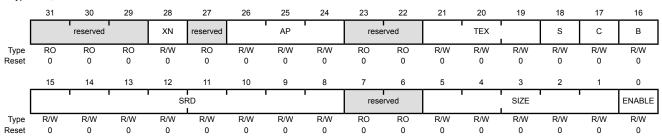

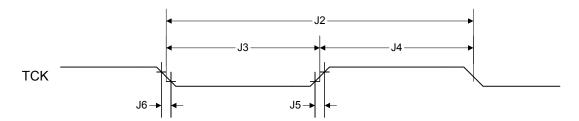

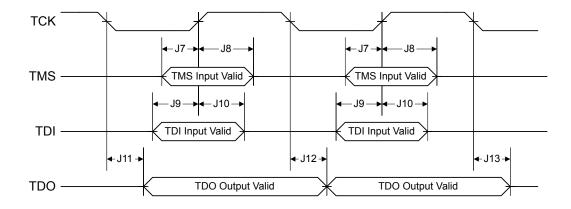

| 4                                                                                                                                                         | JTAG Interface                                                                                                                                                                                                                                                                                                                                                                                         | 161                      |

| 4.1                                                                                                                                                       | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| 4.2                                                                                                                                                       | Signal Description                                                                                                                                                                                                                                                                                                                                                                                     | 162                      |

|                                                                                                                                                           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| 4.3                                                                                                                                                       | Functional Description                                                                                                                                                                                                                                                                                                                                                                                 | 163                      |

| 4.3<br>4.3.1                                                                                                                                              | · ·                                                                                                                                                                                                                                                                                                                                                                                                    | 163<br>163               |

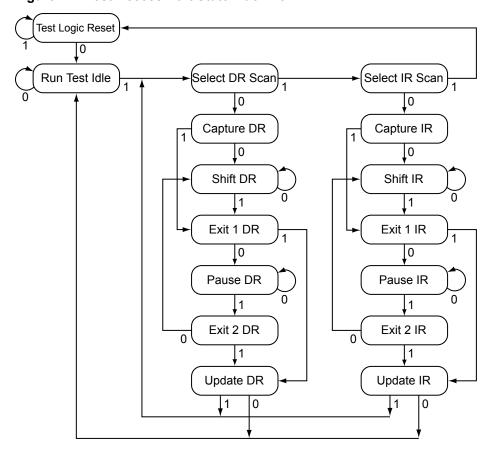

| 4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3                                                                                                                     | Functional Description  JTAG Interface Pins  JTAG TAP Controller                                                                                                                                                                                                                                                                                                                                       | 163<br>163<br>164        |

| 4.3<br>4.3.1<br>4.3.2                                                                                                                                     | Functional Description                                                                                                                                                                                                                                                                                                                                                                                 | 163<br>163<br>164<br>165 |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3                                                                                                                            | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers                                                                                                                                                                                                                                                                                                                      | 163<br>163<br>164<br>165 |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                                                                   | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations                                                                                                                                                                                                                                                                                          |                          |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4                                                                                                            | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations  Initialization and Configuration                                                                                                                                                                                                                                                        |                          |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1                                                                                            | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations Initialization and Configuration  Register Descriptions                                                                                                                                                                                                                                  |                          |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4                                                                                                            | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations  Initialization and Configuration  Register Descriptions  Instruction Register (IR)                                                                                                                                                                                                      |                          |

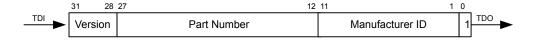

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1<br>4.5.2                                                                                   | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations Initialization and Configuration  Register Descriptions Instruction Register (IR)  Data Registers                                                                                                                                                                                        |                          |

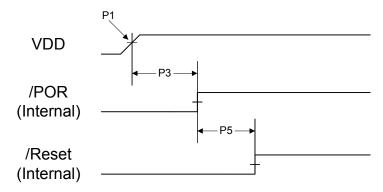

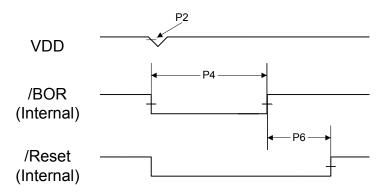

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b>                                                                       | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations  Initialization and Configuration  Register Descriptions  Instruction Register (IR)  Data Registers  System Control                                                                                                                                                                      |                          |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1                                                                       | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations  Initialization and Configuration  Register Descriptions  Instruction Register (IR)  Data Registers  System Control  Signal Description                                                                                                                                                  |                          |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1<br>5.2<br>5.2.1                                                | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations Initialization and Configuration Register Descriptions Instruction Register (IR) Data Registers  System Control  Signal Description  Functional Description                                                                                                                              |                          |

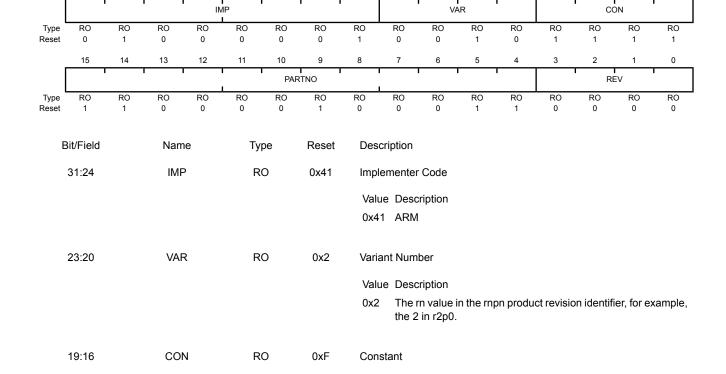

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1<br>5.2                                                         | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations Initialization and Configuration  Register Descriptions Instruction Register (IR)  Data Registers  System Control  Signal Description  Functional Description  Device Identification                                                                                                     |                          |

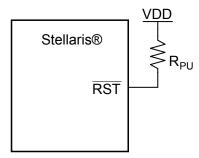

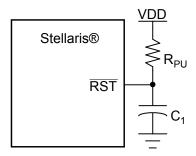

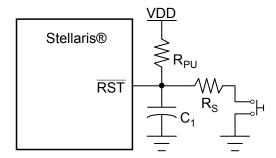

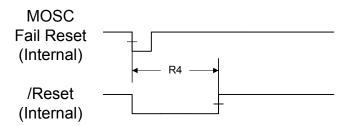

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1<br>5.2<br>5.2.1<br>5.2.2                                              | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations  Initialization and Configuration  Register Descriptions  Instruction Register (IR)  Data Registers  System Control  Signal Description  Functional Description  Device Identification  Reset Control                                                                                    |                          |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                     | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations  Initialization and Configuration  Register Descriptions  Instruction Register (IR)  Data Registers  System Control  Signal Description  Functional Description  Device Identification  Reset Control  Non-Maskable Interrupt                                                            |                          |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3                                     | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations Initialization and Configuration  Register Descriptions Instruction Register (IR)  Data Registers  System Control  Signal Description  Functional Description  Device Identification  Reset Control  Non-Maskable Interrupt  Power Control                                               |                          |

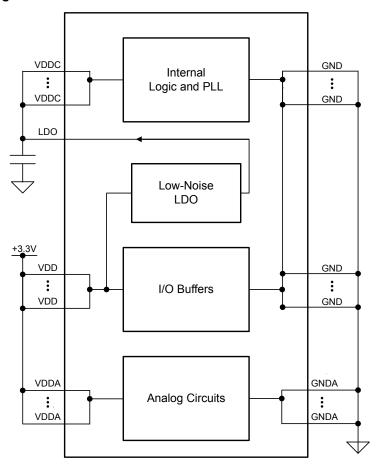

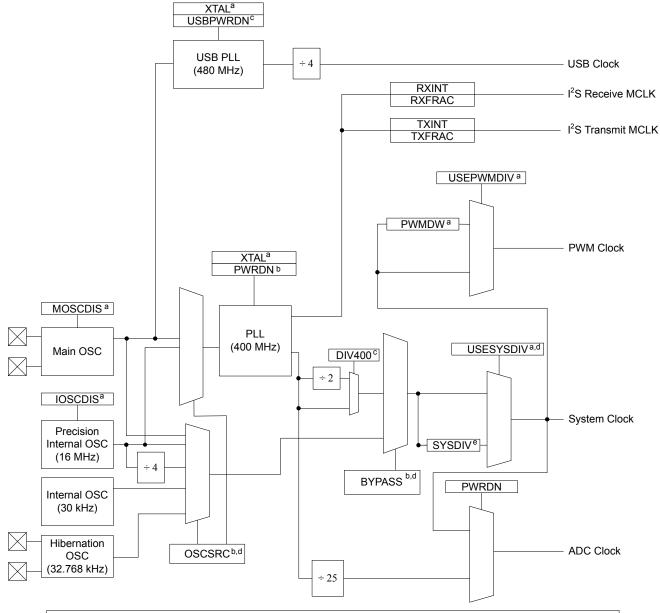

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1<br>5.2.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6 | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations  Initialization and Configuration  Register Descriptions  Instruction Register (IR)  Data Registers  System Control  Signal Description  Functional Description  Device Identification  Reset Control  Non-Maskable Interrupt  Power Control  Clock Control                              |                          |

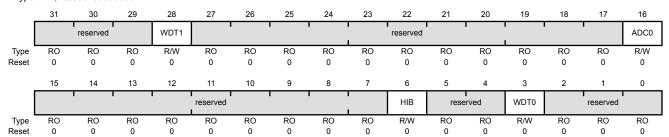

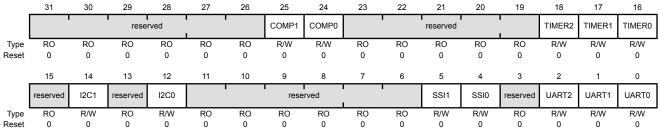

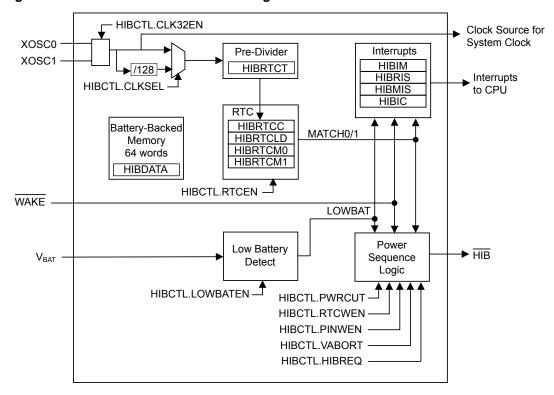

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br><b>5</b><br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5            | Functional Description  JTAG Interface Pins  JTAG TAP Controller  Shift Registers  Operational Considerations Initialization and Configuration Register Descriptions Instruction Register (IR)  Data Registers  System Control  Signal Description  Functional Description  Device Identification  Reset Control  Non-Maskable Interrupt  Power Control  Clock Control  System Control  System Control |                          |

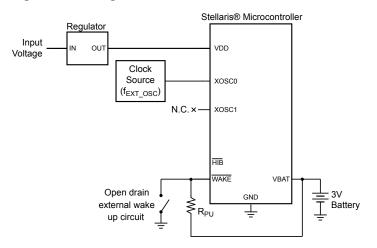

| 6      | Hibernation Module                                        | 264 |

|--------|-----------------------------------------------------------|-----|

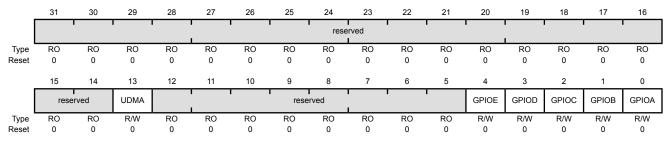

| 6.1    | Block Diagram                                             | 265 |

| 6.2    | Signal Description                                        | 265 |

| 6.3    | Functional Description                                    | 266 |

| 6.3.1  | Register Access Timing                                    | 266 |

| 6.3.2  | Hibernation Clock Source                                  | 266 |

| 6.3.3  | System Implementation                                     | 268 |

| 6.3.4  | Battery Management                                        | 268 |

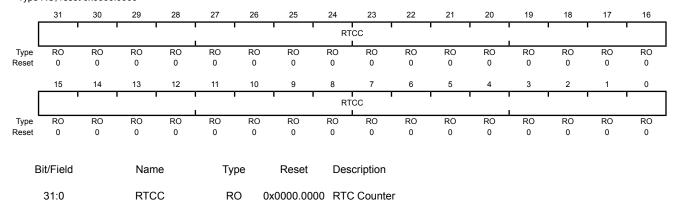

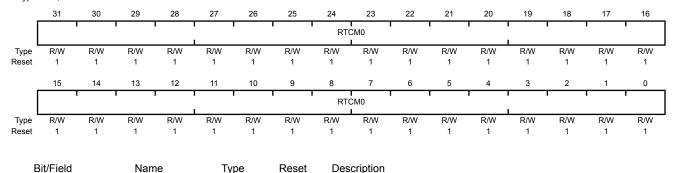

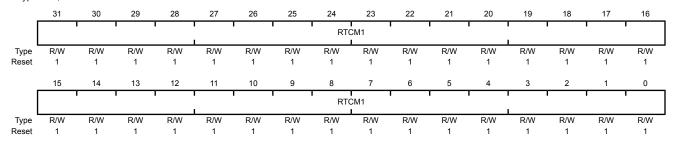

| 6.3.5  | Real-Time Clock                                           |     |

| 6.3.6  | Battery-Backed Memory                                     | 269 |

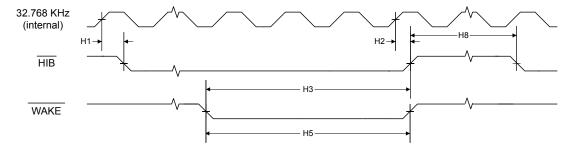

| 6.3.7  | Power Control Using HIB                                   | 269 |

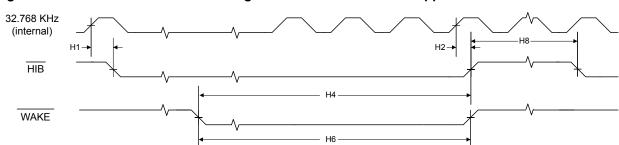

| 6.3.8  | Power Control Using VDD3ON Mode                           | 270 |

| 6.3.9  | Initiating Hibernate                                      |     |

| 6.3.10 | Waking from Hibernate                                     |     |

| 6.3.11 | Interrupts and Status                                     |     |

| 6.4    | Initialization and Configuration                          |     |

| 6.4.1  | Initialization                                            |     |

| 6.4.2  | RTC Match Functionality (No Hibernation)                  |     |

| 6.4.3  | RTC Match/Wake-Up from Hibernation                        |     |

| 6.4.4  | External Wake-Up from Hibernation                         |     |

| 6.4.5  | RTC or External Wake-Up from Hibernation                  |     |

| 6.5    | Register Map                                              |     |

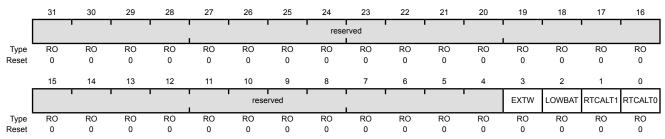

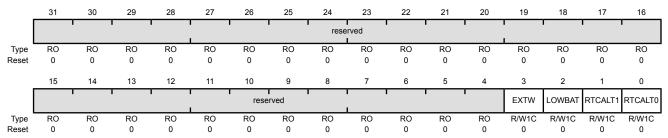

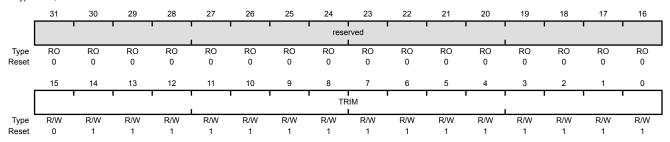

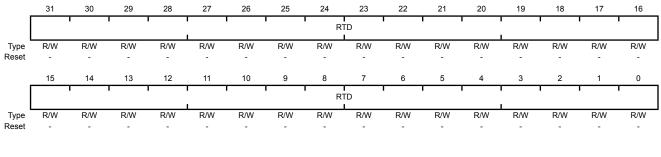

| 6.6    | Register Descriptions                                     |     |

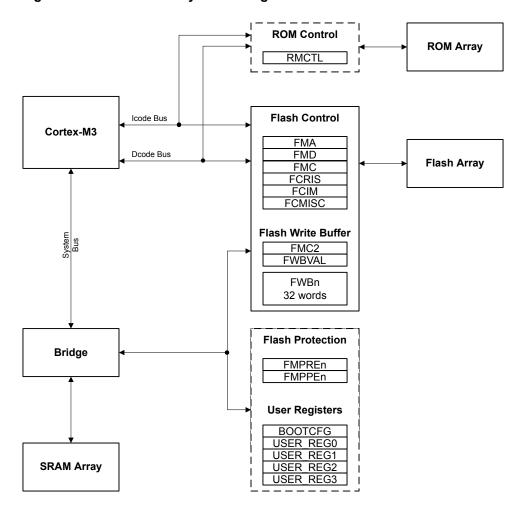

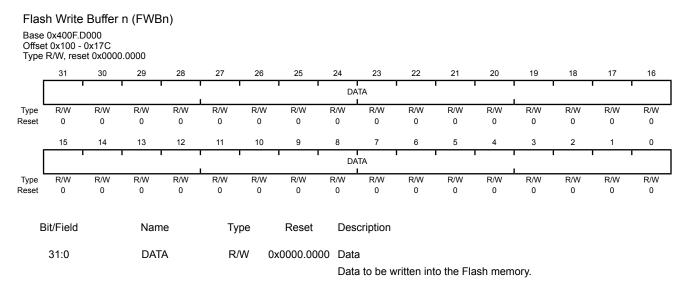

| 7      | Internal Memory                                           |     |

| 7.1    | Block Diagram                                             |     |

| 7.2    | Functional Description                                    |     |

| 7.2.1  | SRAM                                                      |     |

| 7.2.2  | ROM                                                       |     |

| 7.2.3  | Flash Memory                                              |     |

| 7.3    | Register Map                                              |     |

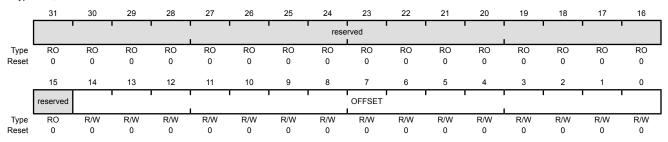

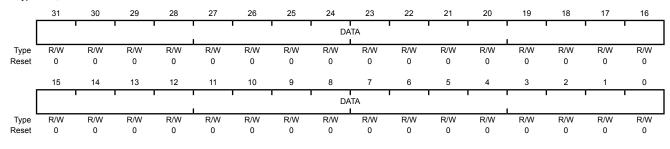

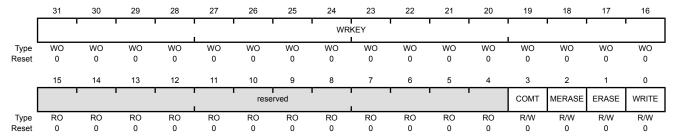

| 7.4    | Flash Memory Register Descriptions (Flash Control Offset) |     |

| 7.5    | Memory Register Descriptions (System Control Offset)      |     |

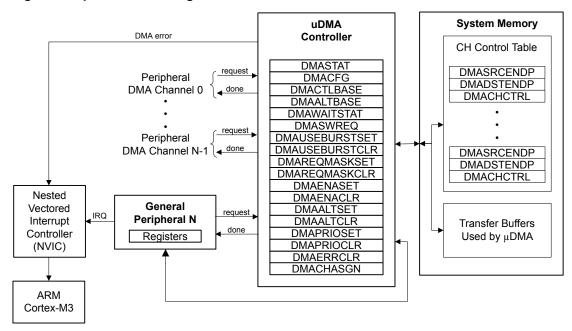

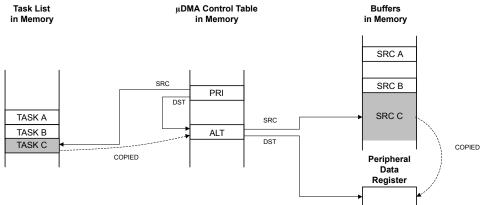

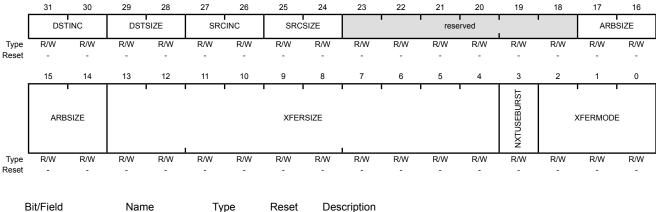

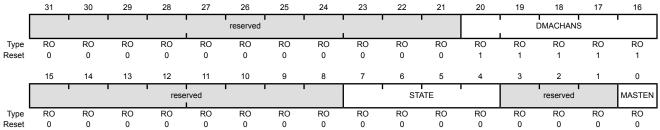

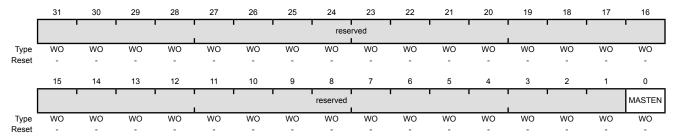

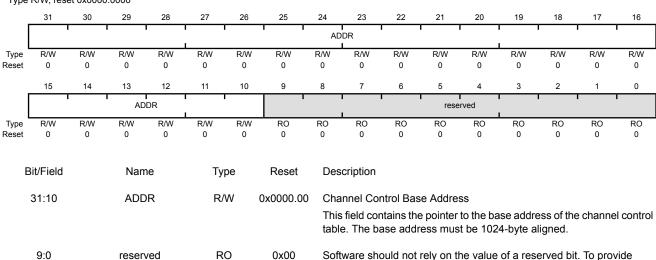

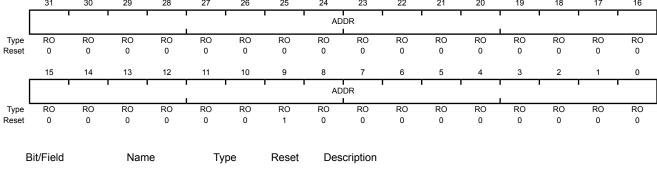

| 8      | Micro Direct Memory Access (µDMA)                         |     |

| 8.1    | Block Diagram                                             |     |

| 8.2    | Functional Description                                    |     |

| 8.2.1  | Channel Assignments                                       |     |

| 8.2.2  | Priority                                                  |     |

| 8.2.3  | Arbitration Size                                          | 330 |

| 8.2.4  | Request Types                                             | 330 |

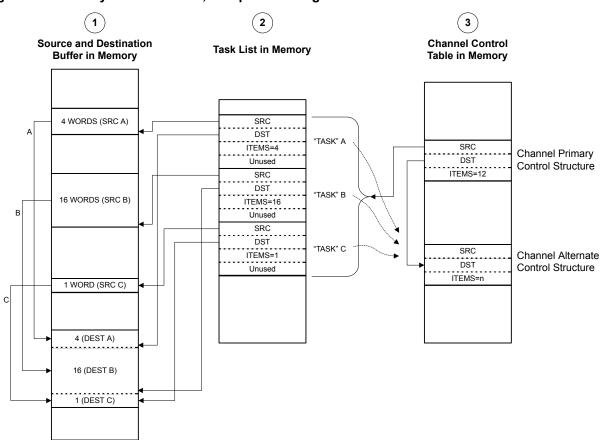

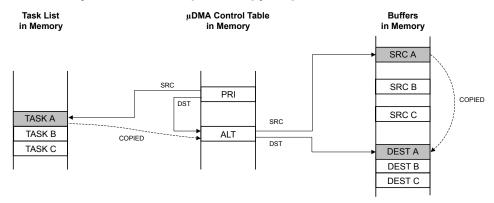

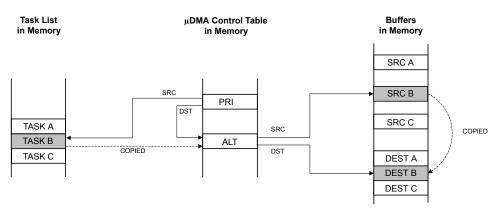

| 8.2.5  | Channel Configuration                                     | 331 |

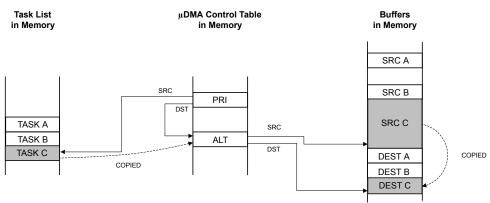

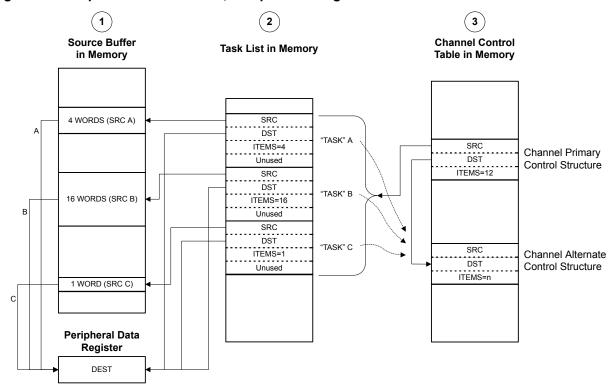

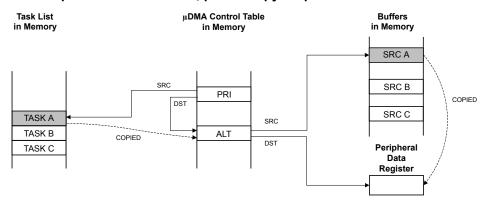

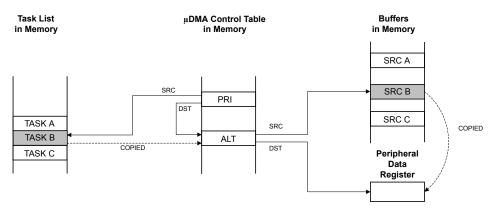

| 8.2.6  | Transfer Modes                                            | 333 |

| 8.2.7  | Transfer Size and Increment                               | 341 |

| 8.2.8  | Peripheral Interface                                      | 341 |

| 8.2.9  | Software Request                                          |     |

| 8.2.10 | Interrupts and Errors                                     |     |

| 8.3    | Initialization and Configuration                          |     |

| 8.3.1  | Module Initialization                                     | 342 |

| 8.3.2  | Configuring a Memory-to-Memory Transfer                   | 342 |

| Configuring a Peripheral for Simple Transmit   | 344                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuring a Peripheral for Ping-Pong Receive | 345                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Configuring Channel Assignments                | 348                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register Map                                   | 348                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

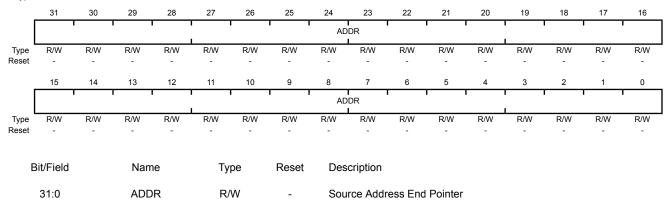

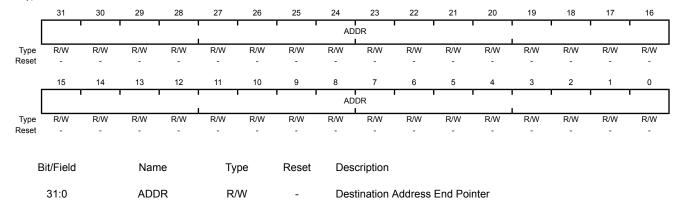

| μDMA Channel Control Structure                 | 349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| μDMA Register Descriptions                     | 356                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

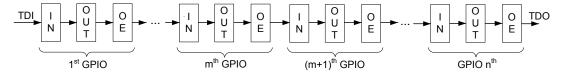

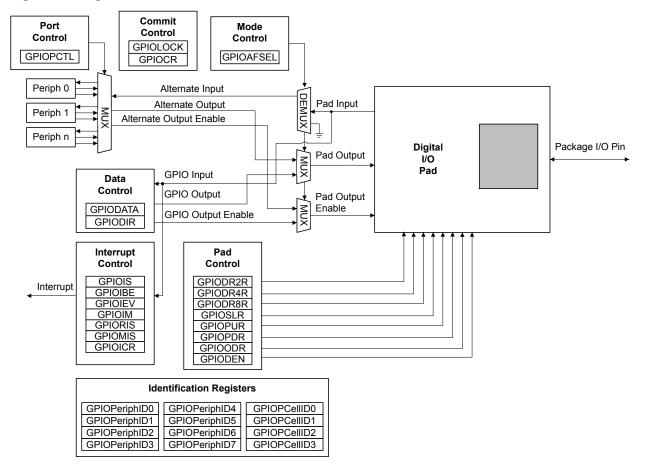

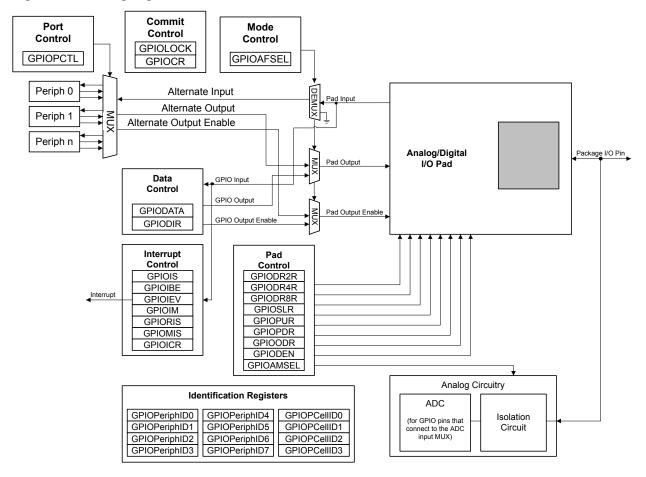

| General-Purpose Input/Outputs (GPIOs)          | 385                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| · ·                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ·                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Mode Control                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Commit Control                                 | 391                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pad Control                                    | 392                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

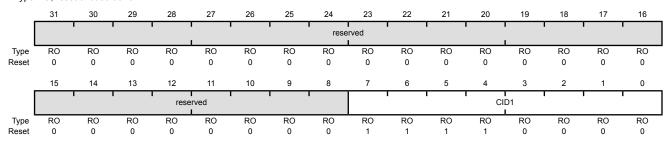

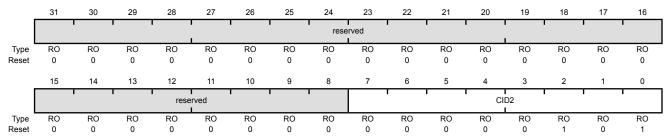

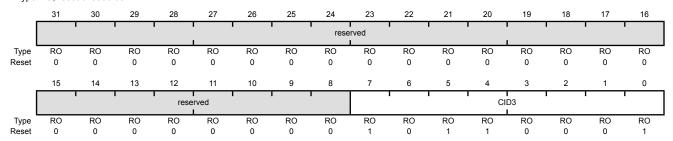

| Identification                                 | 392                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Initialization and Configuration               | 392                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register Map                                   | 393                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

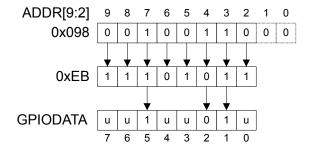

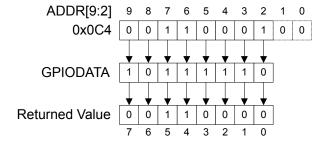

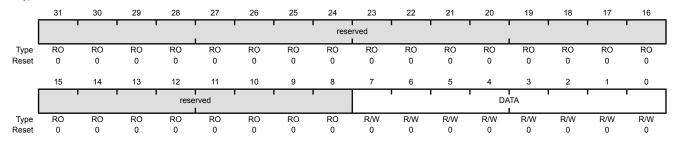

| Register Descriptions                          | 395                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

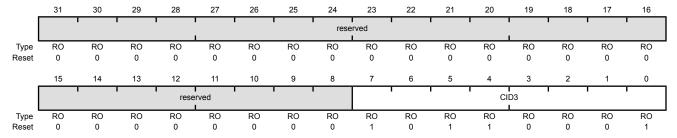

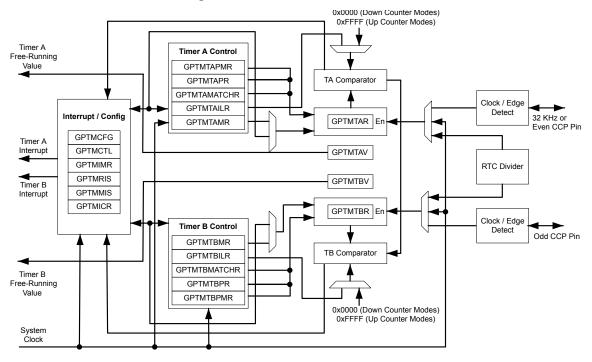

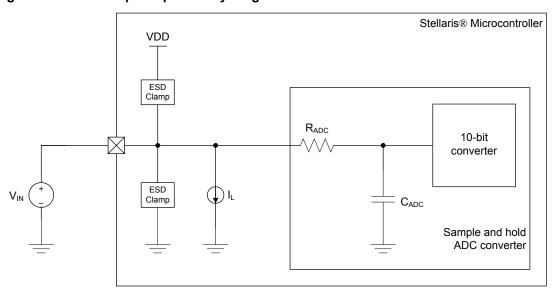

| General-Purnose Timers                         | 436                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |