## **Contents**

| Overview                              | ■ Altera® Solutions Portfolio                                                                                                                                    | 1                          |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                       |                                                                                                                                                                  |                            |

|                                       | ■ 20 nm Device Portfolio                                                                                                                                         | 2                          |

|                                       | ■ 28 nm Device Portfolio                                                                                                                                         | 7                          |

|                                       | ■ 40 nm Device Portfolio                                                                                                                                         | 27                         |

| Davissa                               | ■ 60 nm Device Portfolio                                                                                                                                         | 34                         |

| Devices                               | ■ MAX® CPLD Series                                                                                                                                               | 40                         |

|                                       | ■ Enpirion® Power Portfolio                                                                                                                                      | 43                         |

|                                       | ■ Configuration Devices                                                                                                                                          | 47                         |

|                                       |                                                                                                                                                                  |                            |

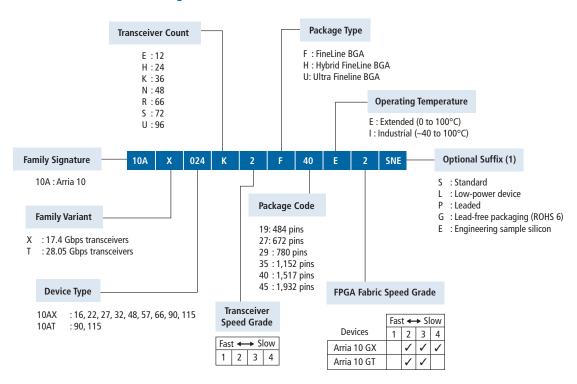

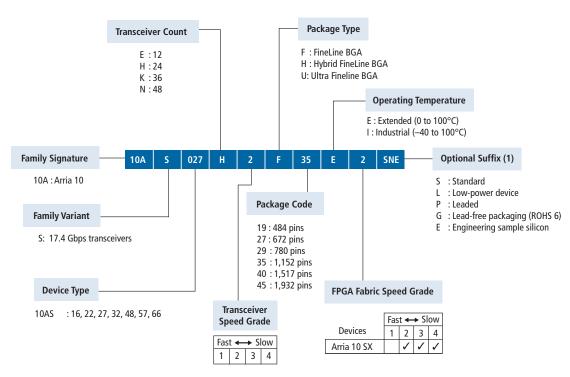

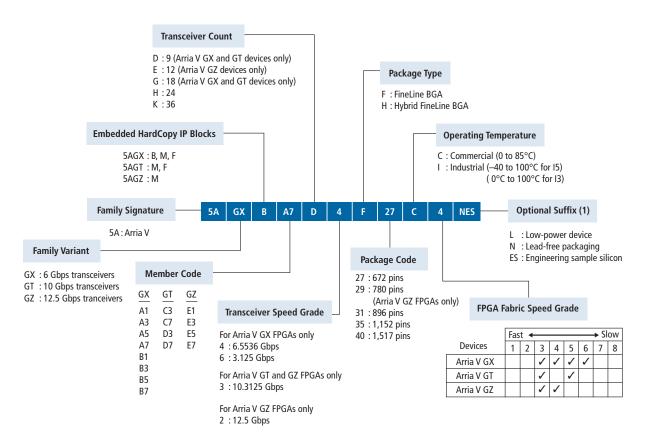

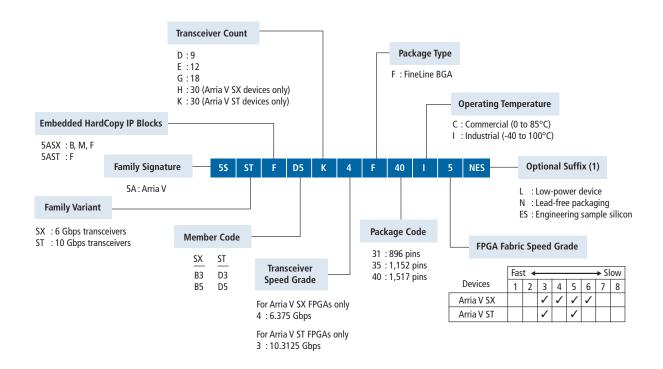

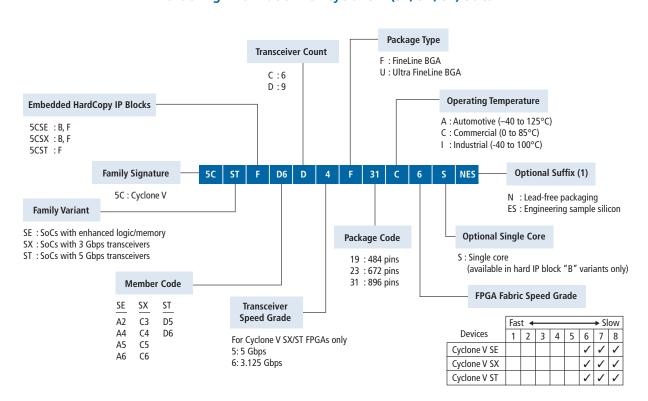

| Ordering Codes                        | ■ Ordering Codes                                                                                                                                                 | 48                         |

|                                       |                                                                                                                                                                  |                            |

|                                       | ■ Quartus® II Software                                                                                                                                           | 52                         |

| Design Software                       | ■ SoC Embedded Design Suite                                                                                                                                      | 55                         |

| Tools and<br>Embedded Processing      | ■ Altera's Customizable Processor Portfolio                                                                                                                      | 56                         |

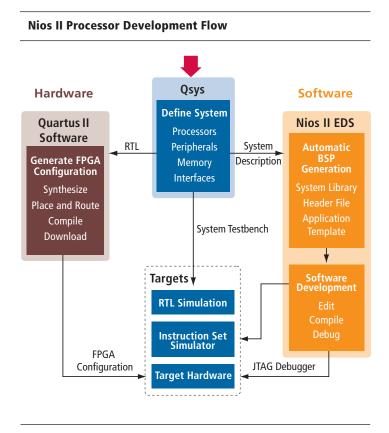

| Litibeduca i Tocessing                | ■ Nios® II Processor                                                                                                                                             | 59                         |

|                                       |                                                                                                                                                                  |                            |

|                                       |                                                                                                                                                                  |                            |

| Intellectual Property (IP)            | ■ Altera and Partner Functions                                                                                                                                   | 61                         |

| Intellectual Property (IP)            | ■ Altera and Partner Functions                                                                                                                                   | 61                         |

| Intellectual Property (IP)  Protocols | <ul><li>Altera and Partner Functions</li><li>Transceiver Protocols</li></ul>                                                                                     | 65                         |

|                                       |                                                                                                                                                                  |                            |

| Protocols                             |                                                                                                                                                                  |                            |

|                                       | ■ Transceiver Protocols                                                                                                                                          | 65                         |

| Protocols                             | ■ Transceiver Protocols  ■ Altera and Partner Development Kits                                                                                                   | 65                         |

| Protocols  Development Kits           | ■ Transceiver Protocols  ■ Altera and Partner Development Kits  ■ Training Overview                                                                              | 65<br>67<br>82             |

| Protocols                             | ■ Transceiver Protocols  ■ Altera and Partner Development Kits  ■ Training Overview ■ Instructor-Led and Virtual Classroom Courses                               | 65<br>67<br>82<br>83       |

| Protocols  Development Kits           | ■ Transceiver Protocols  ■ Altera and Partner Development Kits  ■ Training Overview                                                                              | 65<br>67<br>82             |

| Protocols  Development Kits           | ■ Transceiver Protocols  ■ Altera and Partner Development Kits  ■ Training Overview ■ Instructor-Led and Virtual Classroom Courses ■ Online Training             | 65<br>67<br>82<br>83<br>84 |

| Protocols  Development Kits  Training | ■ Transceiver Protocols  ■ Altera and Partner Development Kits  ■ Training Overview ■ Instructor-Led and Virtual Classroom Courses ■ Online Training  ■ Glossary | 65<br>67<br>82<br>83<br>84 |

| Protocols  Development Kits           | ■ Transceiver Protocols  ■ Altera and Partner Development Kits  ■ Training Overview ■ Instructor-Led and Virtual Classroom Courses ■ Online Training             | 65<br>67<br>82<br>83<br>84 |

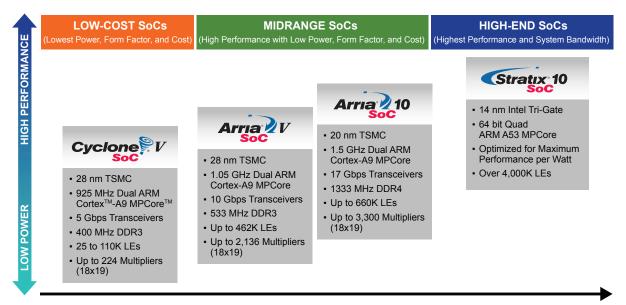

Altera delivers the broadest portfolio of programmable logic devices—FPGAs, SoCs, and CPLDs in combination with software tools, intellectual property (IP), embedded processors, customer support, and technical training. Altera's product leadership, excellent value, and superior quality of service give you a measurable advantage. Bring your great ideas to life faster, better, and more cost effectively.

#### **FPGAs**

Altera FPGAs give you the flexibility to innovate, differentiate, and stay ahead in the market. We have three classes of FPGAs to meet your market needs, from the industry's highest density and performance to the most cost effective.

- Highest bandwidth, highest density FPGAs

- Integrated transceiver variants

- Design entire systems on a chip

# Midrange FPGAs

- Balanced cost, power, and performance FPGAs

- Integrated transceiver and processor variants

- Comprehensive design protection

### **Lowest Cost and Power FPGAs**

- Lowest system cost and power FPGAs

- Integrated transceiver and processor variants

- Fastest time to market

### SoCs

SoCs consolidate two discrete devices into one, reducing system power, cost, and board size while increasing performance. SoCs integrate an ARM-based hard processor system (HPS) consisting of a dual-core ARM\* processor, peripherals, and memory controllers with the FPGA fabric using a high-bandwidth interconnect backbone.

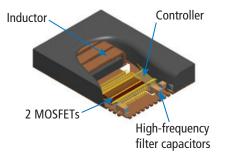

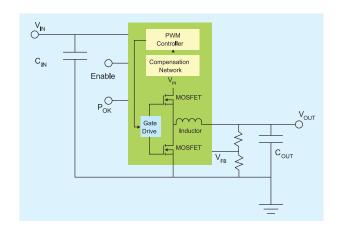

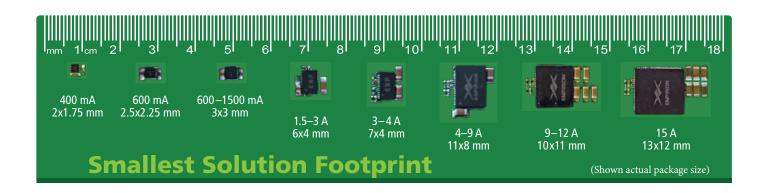

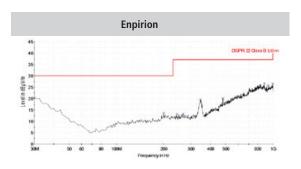

#### **Power**

Power your FPGA with Enpirion power management products. Our integrated products provide an industry-leading combination of small footprint, low noise performance, and high efficiency to complete your design faster.

#### **CPLDs**

For glue logic and any control functions, our non-volatile MAX series comprises the market's lowest cost CPLDs—a single-chip solution, great for interface bridging, level shifting, I/O expansion, and management of analog I/Os.

#### Productivity-Enhancing Design Software, Embedded Processing, IP, Development Kits, and Training

With Altera, you get a complete design environment and a wide choice of design tools—all built to work together easily so your designs are up and running fast. You can try one of our training classes to get a jump-start on your designs. Choose Altera and see how we enhance your productivity and make a difference to your bottom line.

The following features, packages, and I/O matrices give you an overview of our devices. To get more details about these devices or other older devices that are available, check out our online selector guide at www.altera.com/selector.

Arria® 10 GX FPGAs: Up to 96 full-duplex transceivers with data rates up to 17.4 Gbps, 16 Gbps backplane, and up to 1,150K equivalent logic elements (LEs).

|                           |                                                           | Maximum Resource Count for Arria 10 GX FPGAs <sup>1</sup> |                                                                                        |                                                                   |                                                                       |                                               |                                                                    |                                                      |                                                    |                          |  |  |

|---------------------------|-----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------|--------------------------|--|--|

|                           |                                                           | 10AX016                                                   | 10AX022                                                                                | 10AX027                                                           | 10AX032                                                               | 10AX048                                       | 10AX057                                                            | 10AX066                                              | 10AX090                                            | 10AX115                  |  |  |

|                           | Adaptive logic modules (ALMs)                             | 61,510                                                    | 83,730                                                                                 | 101,620                                                           | 118,730                                                               | 181,790                                       | 217,080                                                            | 250,540                                              | 339,620                                            | 427,200                  |  |  |

|                           | LEs (K)                                                   | 160                                                       | 220                                                                                    | 270                                                               | 320                                                                   | 480                                           | 570                                                                | 660                                                  | 900                                                | 1,150                    |  |  |

|                           | Registers                                                 | 246,040                                                   | 334,920                                                                                | 406,480                                                           | 474,920                                                               | 727,160                                       | 868,320                                                            | 1,002,160                                            | 1,358,480                                          | 1,708,800                |  |  |

| ces.                      | M20K memory blocks                                        | 440                                                       | 588                                                                                    | 750                                                               | 891                                                                   | 1,438                                         | 1,800                                                              | 2,133                                                | 2,423                                              | 2,713                    |  |  |

| Resources                 | M20K memory (Mb)                                          | 9                                                         | 11                                                                                     | 15                                                                | 17                                                                    | 28                                            | 35                                                                 | 42                                                   | 47                                                 | 53                       |  |  |

| Ä                         | MLAB memory (Mb)                                          | 1                                                         | 1.8                                                                                    | 2.4                                                               | 2.8                                                                   | 4.3                                           | 5.0                                                                | 5.7                                                  | 9.2                                                | 12.7                     |  |  |

|                           | Variable-precision digital signal processing (DSP) blocks | 156                                                       | 192                                                                                    | 800                                                               | 985                                                                   | 1,368                                         | 1,612                                                              | 1,855                                                | 1,518                                              | 1,518                    |  |  |

|                           | 18 x 19 multipliers                                       | 312                                                       | 382                                                                                    | 1,660                                                             | 1,970                                                                 | 2,736                                         | 3,046                                                              | 3,356                                                | 3,036                                              | 3,036                    |  |  |

| ural                      | Global clock networks                                     | 32                                                        |                                                                                        |                                                                   |                                                                       |                                               |                                                                    |                                                      |                                                    |                          |  |  |

| Architectural<br>Features | Regional clock networks                                   | 8                                                         | 8                                                                                      | 8                                                                 | 8                                                                     | 8                                             | 8                                                                  | 16                                                   | 16                                                 | 16                       |  |  |

| Arc                       | Design security                                           |                                                           |                                                                                        | В                                                                 | itstream encr                                                         | yption with a                                 | uthenticatior                                                      | 1                                                    |                                                    |                          |  |  |

|                           | I/O voltage levels supported (V)                          | 1.2, 1.25, 1.35, 1.8, 2.5, 3.0 <sup>2</sup>               |                                                                                        |                                                                   |                                                                       |                                               |                                                                    |                                                      |                                                    |                          |  |  |

| sə.                       | I/O standards supported                                   | <b>All I/O</b> :<br>SSTL-1<br>D                           | I LVDS I/Os: I<br>s: 1.8 V CMOS<br>2, HSTL-18 (I<br>ifferential SST<br>al HSTL-18 (I a | POD12, POD1<br>S, 1.5 V CMOS<br>and II), HSTL<br>'L-15 (I and II) | 0, Differentia<br>5, 1.2 V CMOS<br>-15 (I and II),<br>), Differential | S, SSTL-18 (La<br>HSTL-12 (La<br>SSTL-135, Di | erential POD<br>and II), SSTL-<br>nd II), HSUL-1<br>fferential SST | 15 (I and II), S<br>2, Differentia<br>L-125, Differe | SSTL-135, SST<br>al SSTL-18 (I a<br>ential SSTL-12 | L-125,<br>and II),<br>2, |  |  |

| //O Features              | LVDS channels, 1.6 Gbps (receive/transmit)                | 120                                                       | 120                                                                                    | 168                                                               | 168                                                                   | 222                                           | 324                                                                | 324                                                  | 384                                                | 384                      |  |  |

| 0/I                       | Embedded dynamic phase alignment (DPA) circuitry          |                                                           |                                                                                        |                                                                   |                                                                       |                                               |                                                                    |                                                      |                                                    |                          |  |  |

|                           | On-chip termination (OCT)                                 | T) Series, parallel, and differential                     |                                                                                        |                                                                   |                                                                       |                                               |                                                                    |                                                      |                                                    |                          |  |  |

|                           | Transceiver count                                         | 12                                                        | 12                                                                                     | 24                                                                | 24                                                                    | 36                                            | 48                                                                 | 48                                                   | 96                                                 | 96                       |  |  |

|                           | PCI Express® (PCIe®)<br>hard IP blocks (Gen3)             | 1                                                         | 1                                                                                      | 2                                                                 | 2                                                                     | 2                                             | 2                                                                  | 2                                                    | 4                                                  | 4                        |  |  |

|                           | Memory devices supported                                  | DDR4, DDR                                                 | 3, DDR2, QDR                                                                           | IV, QDR II+,                                                      | QDR II+ Xtre                                                          | me, LPDDR3,                                   | LPDDR2, RLD                                                        | RAM 3, RLDF                                          | RAM II, LLDRA                                      | AM II, HMC               |  |  |

<sup>&</sup>lt;sup>1</sup> All data is correct at the time of printing, and may be subject to change without prior notice. For the latest information, please visit www.altera.com.

$<sup>^{2}</sup>$  3.0 V compliant, requires a 3 V power supply.

Arria 10 GT FPGAs: Up to 96 full-duplex optimized transceivers with data rates up to 28 Gbps, and up to 1,150K equivalent logic elements.

|                           |                                            | Maximum Resource Cour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nt for Arria 10 GT FPGAs <sup>1</sup> |  |  |  |  |

|---------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

|                           |                                            | 10AT090                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10AT115                               |  |  |  |  |

|                           | ALMs                                       | 339,620                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 427,200                               |  |  |  |  |

|                           | LEs (K)                                    | 900                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1,150                                 |  |  |  |  |

|                           | Registers                                  | 1,358,480                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1,708,800                             |  |  |  |  |

| Resources                 | M20K memory blocks                         | 2,423                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2,713                                 |  |  |  |  |

| Reso                      | M20K memory (Mb)                           | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                    |  |  |  |  |

|                           | MLAB memory (Mb)                           | 9.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12.7                                  |  |  |  |  |

|                           | Variable-precision DSP blocks              | 1,518                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1,518                                 |  |  |  |  |

|                           | 18 x 19 multipliers                        | 3,036                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3,036                                 |  |  |  |  |

| ural                      | Global clock networks                      | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |  |  |  |  |

| Architectural<br>Features | Regional clock networks                    | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16                                    |  |  |  |  |

| Arc                       | Design security                            | Bitstream encryption with authentication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |  |  |  |  |

|                           | I/O voltage levels supported (V)           | 1.2, 1.25, 1.35, 1.8, 2.5, 3.0 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |  |  |  |  |

| //O Features              | I/O standards supported                    | 3 V I/Os Only: 3 V LVTTL, 2.5 V CMOS  DDR and LVDS I/Os: POD12, POD10, Differential POD12, Differential POD10, LVDS, RSDS, mini-LVDS, LVPECL  All I/Os: 1.8 V CMOS, 1.5 V CMOS, 1.2 V CMOS, SSTL-18 (I and II), SSTL-15 (I and II), SSTL-135, SSTL-125, SSTL-12, HSTL-18 (I and II), HSTL-15 (I and II), HSTL-12 (I and II), HSUL-12, Differential SSTL-18 (I and II), Differential SSTL-15 (I and II), Differential SSTL-135, Differential SSTL-125, Differential SSTL-12, Differential HSTL-18 (I and II), Differential HSTL-15 (I and II), Differential HSTL-12 (I and II), Differential HSUL-12 |                                       |  |  |  |  |

| /0 F                      | LVDS channels, 1.6 Gbps (receive/transmit) | 312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 312                                   |  |  |  |  |

|                           | Embedded DPA circuitry                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |  |  |  |  |

|                           | ост                                        | Series, parallel,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | and differential                      |  |  |  |  |

|                           | Transceiver count                          | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96                                    |  |  |  |  |

|                           | PCIe hard IP blocks (Gen3)                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                     |  |  |  |  |

|                           | Memory devices supported                   | DDR4, DDR3, DDR2, QDR IV, QDR II+, QDR II+ Xtreme, LPDDR3, LPDDR2, RLDRAM 3, RLDRAM LLDRAM II, HMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |  |  |  |  |

All data is correct at the time of printing, and may be subject to change without prior notice. For the latest information, please visit www.altera.com.

<sup>&</sup>lt;sup>2</sup> 3.0 V compliant, requires a 3 V power supply.

### **Arria 10 SX SoC Features**

The 20 nm Arria 10 SoCs deliver all the features and benefits of Arria 10 FPGAs plus a second-generation hard processor system with 87 percent higher processor performance (1.5 GHz dual-core ARM Cortex™-A9 MPCore™) and enhancements, such as secure boot, three Ethernet Media Access Controller (EMAC) hard IP cores, and 64 bit DDR4 SDRAM support—all while maintaining full software compatibility with 28 nm SoCs.

|                           |                                            |                                               | M                                                                                                          | laximum Resou                                                                | ırce Count for A                                             | Arria 10 SX SoC                                                                       | 1                                                               |                                       |  |  |  |

|---------------------------|--------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|--|--|--|

|                           |                                            | 10AS016                                       | 10AS022                                                                                                    | 10AS027                                                                      | 10AS032                                                      | 10AS048                                                                               | 10AS057                                                         | 10AS066                               |  |  |  |

|                           | ALMs                                       | 61,510                                        | 83,730                                                                                                     | 101,620                                                                      | 118,730                                                      | 181,790                                                                               | 217,080                                                         | 250,540                               |  |  |  |

|                           | LEs (K)                                    | 160                                           | 220                                                                                                        | 270                                                                          | 320                                                          | 480                                                                                   | 570                                                             | 660                                   |  |  |  |

|                           | Registers                                  | 246,040                                       | 334,920                                                                                                    | 406,480                                                                      | 474,920                                                      | 727,160                                                                               | 868,320                                                         | 1,002,160                             |  |  |  |

| Resources                 | M20K memory blocks                         | 440                                           | 588                                                                                                        | 750                                                                          | 891                                                          | 1,438                                                                                 | 1,800                                                           | 2,133                                 |  |  |  |

| Resor                     | M20K memory (Mb)                           | 9                                             | 11                                                                                                         | 15                                                                           | 17                                                           | 28                                                                                    | 35                                                              | 42                                    |  |  |  |

| _                         | MLAB memory (Mb)                           | 1                                             | 1.8                                                                                                        | 2.4                                                                          | 2.8                                                          | 4.3                                                                                   | 5.0                                                             | 5.7                                   |  |  |  |

|                           | DSP blocks                                 | 156                                           | 192                                                                                                        | 800                                                                          | 985                                                          | 1,368                                                                                 | 1,612                                                           | 1,855                                 |  |  |  |

|                           | 18 x 19 multipliers                        | 312                                           | 382                                                                                                        | 1,660                                                                        | 1,970                                                        | 2,736                                                                                 | 3,046                                                           | 3,356                                 |  |  |  |

| Architectural<br>Features | Global clock networks                      | 32                                            |                                                                                                            |                                                                              |                                                              |                                                                                       |                                                                 |                                       |  |  |  |

| Archite<br>Featu          | Regional clock networks                    | 8                                             | 8                                                                                                          | 8                                                                            | 8                                                            | 8                                                                                     | 8                                                               | 16                                    |  |  |  |

|                           | I/O voltage levels supported (V)           | 1.2, 1.25, 1.35, 1.8, 2.5, 3.0 <sup>2</sup>   |                                                                                                            |                                                                              |                                                              |                                                                                       |                                                                 |                                       |  |  |  |

| tures                     | I/O standards supported                    | <b>All I/Os:</b> 1.8<br>SSTL-12, H<br>Differe | OS I/Os: POD12, I<br>3 V CMOS, 1.5 V C<br>STL-18 (I and II),<br>ential SSTL-15 (I a<br>TL-18 (I and II), D | POD10, Differen<br>CMOS, 1.2 V CM<br>HSTL-15 (I and I<br>Ind II), Differenti | OS, SSTL-18 (I ai<br>I), HSTL-12 (I and<br>al SSTL-135, Diff | rential POD10, L\<br>nd II), SSTL-15 (I a<br>d II), HSUL-12, Dit<br>erential SSTL-125 | and II), SSTL-135,<br>fferential SSTL-18<br>5, Differential SST | , SSTL-125,<br>3 (I and II),<br>L-12, |  |  |  |

| //O Features              | LVDS channels, 1.6 Gbps (receive/transmit) | 120                                           | 120                                                                                                        | 168                                                                          | 168                                                          | 222                                                                                   | 270                                                             | 270                                   |  |  |  |

| _                         | Embedded DPA circuitry                     |                                               |                                                                                                            |                                                                              | ✓                                                            |                                                                                       |                                                                 |                                       |  |  |  |

|                           | ОСТ                                        |                                               |                                                                                                            | Series, <sub> </sub>                                                         | parallel, and diffe                                          | erential                                                                              |                                                                 |                                       |  |  |  |

|                           | Transceiver count                          | 12                                            | 12                                                                                                         | 24                                                                           | 24                                                           | 36                                                                                    | 48                                                              | 48                                    |  |  |  |

|                           | PCIe hard IP blocks (Gen3)                 | 1                                             | 1                                                                                                          | 2                                                                            | 2                                                            | 2                                                                                     | 2                                                               | 2                                     |  |  |  |

|                           | Memory devices supported                   | DDR4, DDR3, DI                                | DR2, QDR IV, QDR                                                                                           | II+, QDR II+ Xt                                                              | reme, LPDDR3, LI                                             | PDDR2, RLDRAM                                                                         | 3, RLDRAM II, LL                                                | DRAM II, HMC                          |  |  |  |

All data is correct at the time of printing, and may be subject to change without prior notice. For the latest information, please visit www.altera.com.

$<sup>^{2}\,3.0\</sup> V$  compliant, requires a 3 V power supply.

|                                                 |                                                    |                                                   | Max                             | ximum Resou                                                 | rce Count for                     | Arria 10 SX S                                             | <b>oC</b> <sup>1</sup> |         |  |  |

|-------------------------------------------------|----------------------------------------------------|---------------------------------------------------|---------------------------------|-------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------|------------------------|---------|--|--|

|                                                 |                                                    | 10AS016                                           | 10AS022                         | 10AS027                                                     | 10AS032                           | 10AS048                                                   | 10AS057                | 10AS066 |  |  |

|                                                 | Central processing unit (CPU) core                 |                                                   | I                               | Dual-core ARM                                               | Cortex-A9 MF                      | Core processor                                            | r                      |         |  |  |

|                                                 | CPU cache and Co-processors                        |                                                   |                                 | L1 o<br>Layer 2<br>ting-point unit<br>ARM N<br>RM CoreSight | leon™ media                       | KB) ) shared nd double preci engine trace technolog (SCU) |                        |         |  |  |

|                                                 | Scratch pad RAM                                    | 256 KB                                            |                                 |                                                             |                                   |                                                           |                        |         |  |  |

|                                                 | HPS DDR memory                                     |                                                   |                                 | DDR4 and DI                                                 | DR3 (Up to 64                     | bit with ECC)                                             |                        |         |  |  |

| Direct Memory Access (DMA) controller 8-channel |                                                    |                                                   |                                 |                                                             |                                   |                                                           |                        |         |  |  |

| EMAC 3 x 10/100/1000 EMAC v                     |                                                    |                                                   |                                 |                                                             | 0 EMAC with i                     | ntegrated DMA                                             | 1                      |         |  |  |

| SSOF                                            | USB On-The-Go controller (OTG)                     |                                                   | 2 x USB OTG with integrated DMA |                                                             |                                   |                                                           |                        |         |  |  |

| Hard Processor System                           | UART controller                                    |                                                   |                                 | 2 x UA                                                      | JART 16550 compatible             |                                                           |                        |         |  |  |

| ard F                                           | Serial Peripheral Interface (SPI) controller       |                                                   |                                 |                                                             | 4 x SPI                           |                                                           |                        |         |  |  |

| <b>=</b>                                        | I <sup>2</sup> C controller                        |                                                   |                                 |                                                             | 5 x I <sup>2</sup> C              |                                                           |                        |         |  |  |

|                                                 | Quad SPI flash controller                          |                                                   |                                 | 1 x SIO, DIO                                                | O, QIO SPI flash                  | n supported                                               |                        |         |  |  |

|                                                 | SD/SDIO/MMC controller                             |                                                   | 1                               | x eMMC 4.5 v                                                | with DMA and                      | CE-ATA suppor                                             | t                      |         |  |  |

|                                                 | NAND flash controller                              |                                                   |                                 |                                                             | ONFI 1.0 or la<br>and 16 bit supp |                                                           |                        |         |  |  |

|                                                 | General-purpose timers                             |                                                   |                                 |                                                             | 7X                                |                                                           |                        |         |  |  |

|                                                 | Software-programmable general-purpose I/Os (GPIOs) | Max 54 GPIO                                       |                                 |                                                             |                                   |                                                           |                        |         |  |  |

|                                                 | Direct shared I/Os                                 | 48 I/O to connect HPS peripherals directly to I/O |                                 |                                                             |                                   |                                                           |                        |         |  |  |

|                                                 | Watchdog timers                                    | 4X                                                |                                 |                                                             |                                   |                                                           |                        |         |  |  |

|                                                 | Security                                           |                                                   | Secure l                        | boot, Advanced                                              | d Encryption St                   | andard (AES) a                                            | nd SHA                 |         |  |  |

<sup>&</sup>lt;sup>1</sup>All data is correct at the time of printing, and may be subject to change without prior notice. For the latest information, please visit www.altera.com.

## Arria 10 FPGA Series Package and I/O Matrices

|         |                                                      |                                                      | Arria 10 G                                           | X/GT FPGAs <sup>1</sup>                                |                                                        |                                                        |  |  |  |

|---------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|--|--|

|         | UBGA (U)                                             |                                                      | FBGA (F)                                             |                                                        |                                                        |                                                        |  |  |  |

|         | <b>484 pin (U19)</b><br>19 x 19 (mm)<br>0.8-mm pitch | <b>672 pin (F27)</b><br>27 x 27 (mm)<br>1.0-mm pitch | <b>780 pin (F29)</b><br>29 x 29 (mm)<br>1.0-mm pitch | <b>1,152 pin (F34)</b><br>35 x 35 (mm)<br>1.0-mm pitch | <b>1,152 pin (F35)</b><br>35 x 35 (mm)<br>1.0-mm pitch | <b>1,152 pin (F36)</b><br>35 x 35 (mm)<br>1.0-mm pitch |  |  |  |

| 10AX016 | 192, 48, 72, 6                                       | 240, 48, 96, 12                                      | 288, 48, 120, 12                                     |                                                        |                                                        |                                                        |  |  |  |

| 10AX022 | 192, 48, 72, 6                                       | 240, 48, 96, 12                                      | 288, 48, 120, 12                                     |                                                        |                                                        |                                                        |  |  |  |

| 10AX027 |                                                      | 240, 48, 96, 12                                      | 360, 48, 156, 12                                     | 384, 48, 168, 24                                       | 384, 48, 168, 24                                       |                                                        |  |  |  |

| 10AX032 |                                                      | 240, 48, 96, 12                                      | 360, 48, 156, 12                                     | 384, 48, 168, 24                                       | 384, 48, 168, 24                                       |                                                        |  |  |  |

| 10AX048 |                                                      |                                                      | 360, 48, 156, 12                                     | 492, 48, 222, 24                                       | 396, 48, 174, 36                                       |                                                        |  |  |  |

| 10AX057 |                                                      |                                                      |                                                      | 492, 48, 222, 24                                       | 396, 48, 174, 36                                       | 432, 48, 192, 36                                       |  |  |  |

| 10AX066 |                                                      |                                                      |                                                      | 492, 48, 222, 24                                       | 396, 48, 174, 36                                       | 432, 48, 192, 36                                       |  |  |  |

| 10AX090 |                                                      |                                                      |                                                      | 504, 0, 252, 24                                        |                                                        | 432, 0, 216, 36                                        |  |  |  |

| 10AX115 |                                                      |                                                      |                                                      | 504, 0, 252, 24                                        |                                                        | 432, 0, 216, 36                                        |  |  |  |

|         |                                                        | Arria 10 GX/GT FPGAs <sup>1</sup>                      |                                                        |                                                        |                                                        |                                                        |  |  |  |  |  |

|---------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|

|         |                                                        | FBGA (F)                                               |                                                        |                                                        |                                                        |                                                        |  |  |  |  |  |

|         | <b>1,517 pin (F40)</b><br>40 x 40 (mm)<br>1.0-mm pitch | <b>1,517 pin (F40)</b><br>40 x 40 (mm)<br>1.0-mm pitch | <b>1,517 pin (F40)</b><br>40 x 40 (mm)<br>1.0-mm pitch | <b>1,932 pin (F45)</b><br>45 x 45 (mm)<br>1.0-mm pitch | <b>1,932 pin (F45)</b><br>45 x 45 (mm)<br>1.0-mm pitch | <b>1,932 pin (F45)</b><br>45 x 45 (mm)<br>1.0-mm pitch |  |  |  |  |  |

| 10AX027 |                                                        |                                                        |                                                        |                                                        |                                                        |                                                        |  |  |  |  |  |

| 10AX032 |                                                        |                                                        |                                                        |                                                        |                                                        |                                                        |  |  |  |  |  |

| 10AX048 |                                                        |                                                        |                                                        |                                                        |                                                        |                                                        |  |  |  |  |  |

| 10AX057 | 696, 48, 324, 36                                       | 588, 48, 270, 48                                       |                                                        |                                                        |                                                        |                                                        |  |  |  |  |  |

| 10AX066 | 696, 48, 324, 36                                       | 588, 48, 270, 48                                       |                                                        |                                                        |                                                        |                                                        |  |  |  |  |  |

| 10AX090 |                                                        | 600, 0, 300, 48                                        | 342, 0, 154, 66                                        | 768, 0, 384, 48                                        | 624, 0, 312, 72                                        | 480, 0, 240, 96                                        |  |  |  |  |  |

| 10AX115 |                                                        | 600, 0, 300, 48                                        | 342, 0, 154, 66                                        | 768, 0, 384, 48                                        | 624, 0, 312, 72                                        | 480, 0, 240, 96                                        |  |  |  |  |  |

| 10AT090 |                                                        | 600, 0, 300, 48                                        |                                                        |                                                        | 624, 0, 312, 72                                        | 480, 0, 240, 96                                        |  |  |  |  |  |

| 10AT115 |                                                        | 600, 0, 300, 48                                        |                                                        |                                                        | 624, 0, 312, 72                                        | 480, 0, 240, 96                                        |  |  |  |  |  |

|         | Arria 10 SX SoCs <sup>1</sup>                 |                                               |                                                      |                                                        |                                                        |                                                        |                                                        |  |

|---------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

|         | UBGA (U)                                      |                                               | FBGA (F)                                             |                                                        |                                                        |                                                        |                                                        |  |

|         | 484 pin (U19)<br>19 x 19 (mm)<br>0.8-mm pitch | 672 pin (F27)<br>27 x 27 (mm)<br>1.0-mm pitch | <b>780 pin (F29)</b><br>29 x 29 (mm)<br>1.0-mm pitch | <b>1,152 pin (F34)</b><br>35 x 35 (mm)<br>1.0-mm pitch | <b>1,152 pin (F35)</b><br>35 x 35 (mm)<br>1.0-mm pitch | <b>1,517 pin (F40)</b><br>40 x 40 (mm)<br>1.0-mm pitch | <b>1,517 pin (F40)</b><br>40 x 40 (mm)<br>1.0-mm pitch |  |

| 10AS016 | 192, 48, 72, 6                                | 240, 48, 96, 12                               | 288, 48, 120, 12                                     |                                                        |                                                        |                                                        |                                                        |  |

| 10AS022 | 192, 48, 72, 6                                | 240, 48, 96, 12                               | 288, 48, 120, 12                                     |                                                        |                                                        |                                                        |                                                        |  |

| 10AS027 |                                               | 240, 48, 96, 12                               | 360, 48, 156, 12                                     | 384, 48, 168, 24                                       | 384, 48, 168, 24                                       |                                                        |                                                        |  |

| 10AS032 |                                               | 240, 48, 96, 12                               | 360, 48, 156, 12                                     | 384, 48, 168, 24                                       | 384, 48, 168, 24                                       |                                                        |                                                        |  |

| 10AS048 |                                               |                                               | 360, 48, 156, 12                                     | 492, 48, 222, 24                                       | 396, 48, 174, 36                                       |                                                        |                                                        |  |

| 10AS057 |                                               |                                               |                                                      | 492, 48, 222, 24                                       | 396, 48, 174, 36                                       | 696, 48, 324, 36 📮                                     | 588, 48, 270, 48                                       |  |

| 10AS066 |                                               |                                               |                                                      | 492, 48, 222, 24                                       | 396, 48, 174, 36                                       | 696, 48, 324, 36                                       | 588, 48, 270, 48                                       |  |

<sup>&</sup>lt;sup>1</sup> All data is correct at the time of printing, and may be subject to change without prior notice. For the latest information, please visit www.altera.com.

624, 48, 192, 48 Numbers indicate GPIO count, 3.0 V I/O count, LVDS count, and transceiver count.

Vertical migration (same Vcc, Gnd, ISP, and input pins). User I/Os may be less than labeled for vertical migration.

Arria 10 series devices are offered in extended and industrial temperatures, and RoHS-compliant packages.

|                           |                                            | Maximum Resource Count fo                                                                                                                                                                                                                                                                                                    | r Stratix V GT FPGAs (0.85 V) <sup>1</sup> |  |  |  |

|---------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|

|                           |                                            | 5SGTC5                                                                                                                                                                                                                                                                                                                       | 5SGTC7                                     |  |  |  |

|                           | ALMs                                       | 160,400                                                                                                                                                                                                                                                                                                                      | 234,720                                    |  |  |  |

|                           | LEs (K)                                    | 425                                                                                                                                                                                                                                                                                                                          | 622                                        |  |  |  |

|                           | Registers                                  | 641,600                                                                                                                                                                                                                                                                                                                      | 938,880                                    |  |  |  |