# TMS320x2805x Piccolo

# **Technical Reference Manual**

Literature Number: SPRUHE5B November 2012–Revised April 2013

# **Contents**

| Pref | ace   |                               |                                                                    | 31        |  |  |  |

|------|-------|-------------------------------|--------------------------------------------------------------------|-----------|--|--|--|

| 1    | Syste | System Control and Interrupts |                                                                    |           |  |  |  |

|      | 1.1   |                               | and OTP Memory                                                     |           |  |  |  |

|      |       | 1.1.1                         | Flash Memory                                                       | 33        |  |  |  |

|      |       | 1.1.2                         | OTP Memory                                                         | 33        |  |  |  |

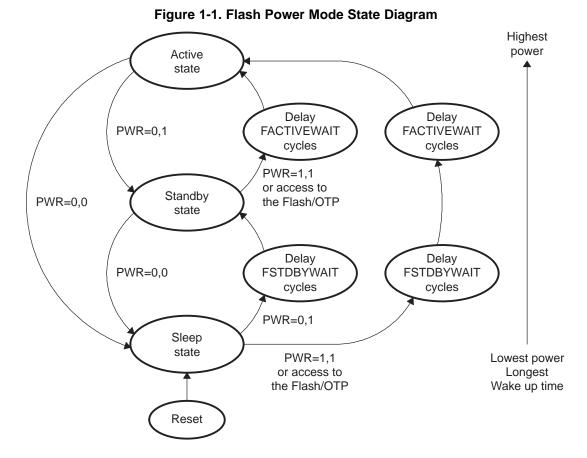

|      |       | 1.1.3                         | Flash and OTP Power Modes                                          | 34        |  |  |  |

|      |       | 1.1.4                         | Flash and OTP Registers                                            | 39        |  |  |  |

|      | 1.2   | Clocki                        | ng                                                                 | 45        |  |  |  |

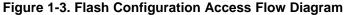

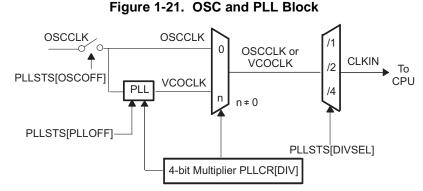

|      |       | 1.2.1                         | Clocking and System Control                                        | 45        |  |  |  |

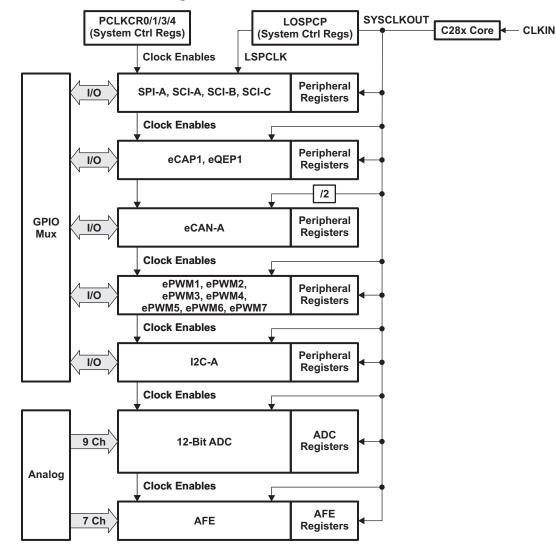

|      |       | 1.2.2                         | OSC and PLL Block                                                  | 51        |  |  |  |

|      |       | 1.2.3                         | Low-Power Modes Block                                              | <b>69</b> |  |  |  |

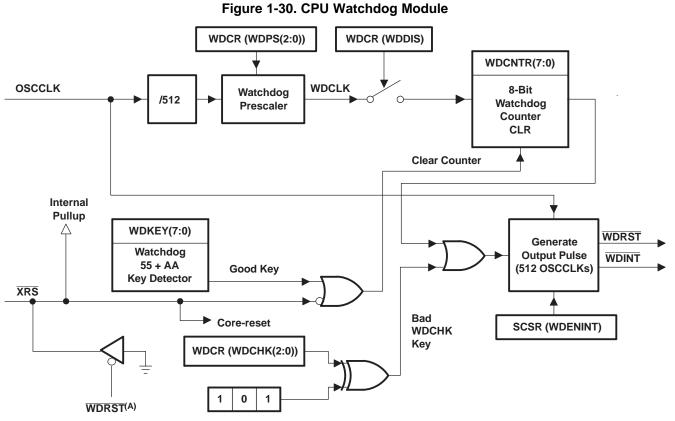

|      |       | 1.2.4                         | CPU Watchdog Block                                                 | 72        |  |  |  |

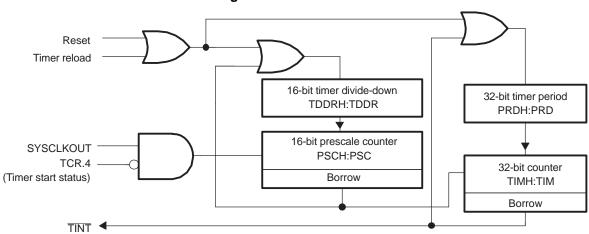

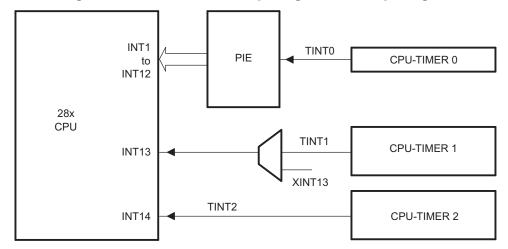

|      |       | 1.2.5                         | 32-Bit CPU Timers 0/1/2                                            | 78        |  |  |  |

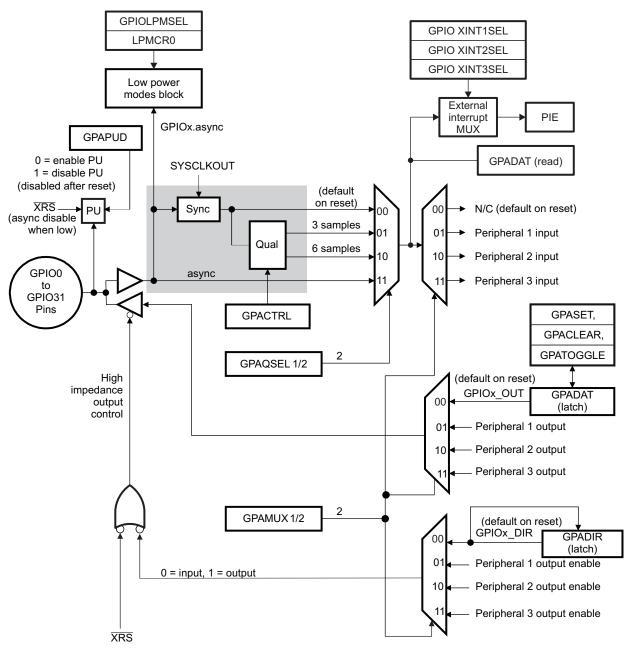

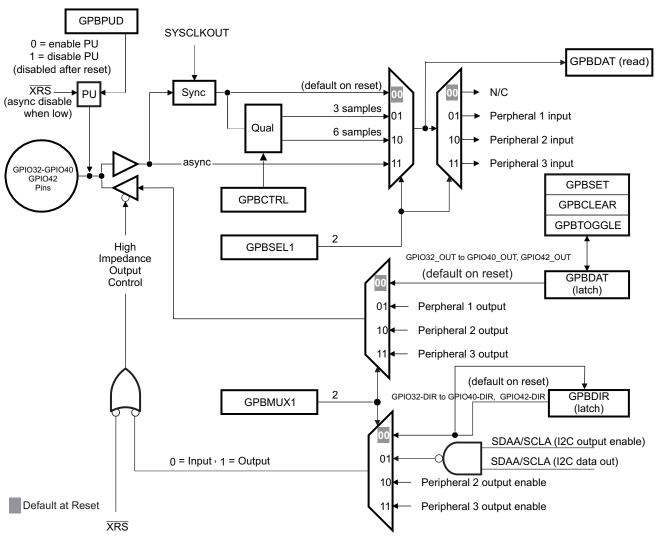

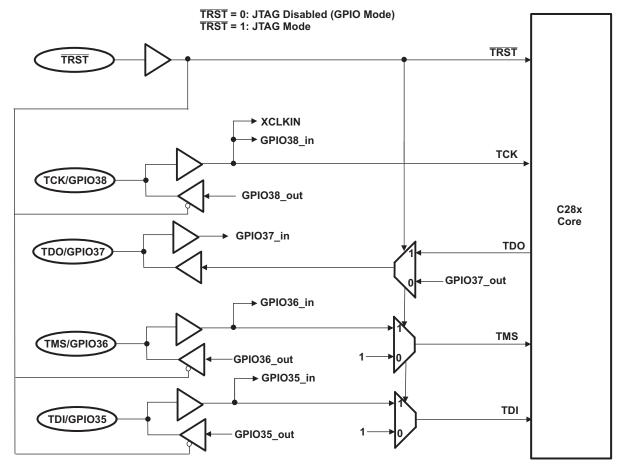

|      | 1.3   | Gener                         | al-Purpose Input/Output (GPIO)                                     | 83        |  |  |  |

|      |       | 1.3.1                         | GPIO Module Overview                                               | 83        |  |  |  |

|      |       | 1.3.2                         | Configuration Overview                                             | 87        |  |  |  |

|      |       | 1.3.3                         | Digital General Purpose I/O Control                                |           |  |  |  |

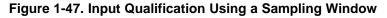

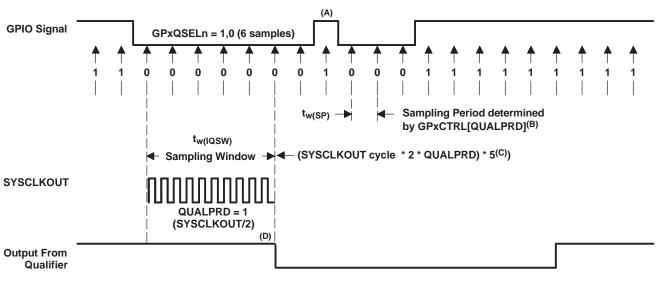

|      |       | 1.3.4                         | Input Qualification                                                |           |  |  |  |

|      |       | 1.3.5                         | GPIO and Peripheral Multiplexing (MUX)                             |           |  |  |  |

|      |       | 1.3.6                         | Register Bit Definitions                                           | 99        |  |  |  |

|      | 1.4   | Periph                        | eral Frames                                                        | 115       |  |  |  |

|      |       | 1.4.1                         | Peripheral Frame Registers                                         | 115       |  |  |  |

|      |       | 1.4.2                         | EALLOW-Protected Registers                                         | 117       |  |  |  |

|      |       | 1.4.3                         | Device Emulation Registers                                         | 122       |  |  |  |

|      |       | 1.4.4                         | Write-Followed-by-Read Protection                                  | 124       |  |  |  |

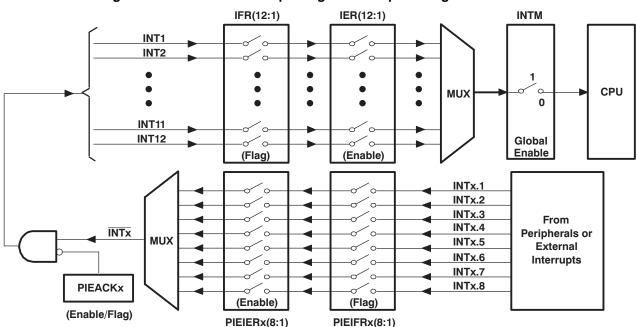

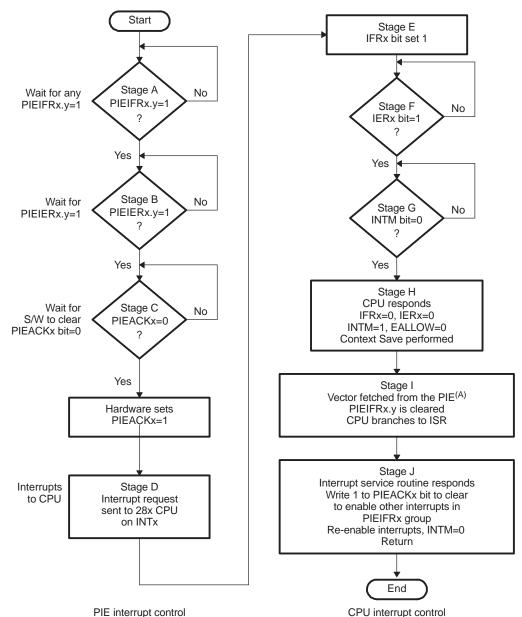

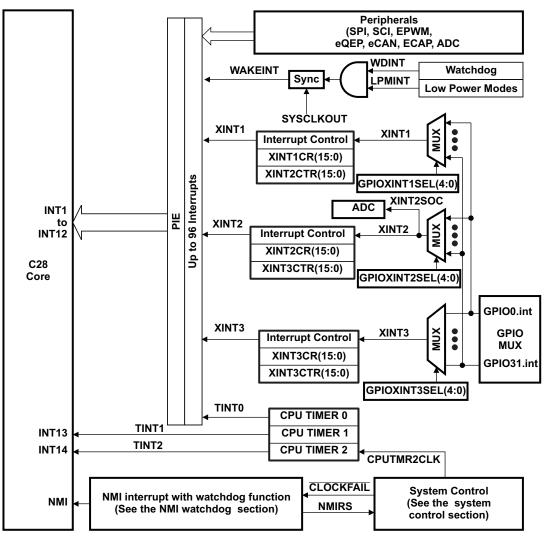

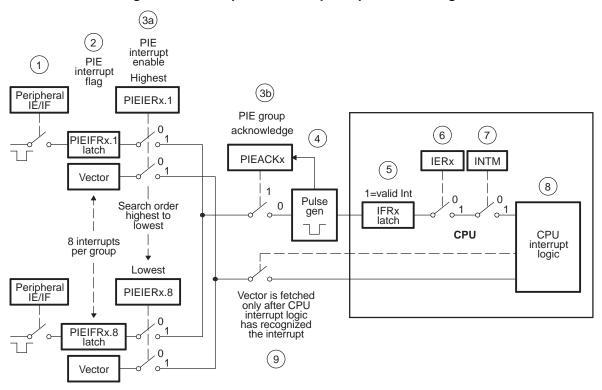

|      | 1.5   | Periph                        | eral Interrupt Expansion (PIE)                                     | 125       |  |  |  |

|      |       | 1.5.1                         | Overview of the PIE Controller                                     | 125       |  |  |  |

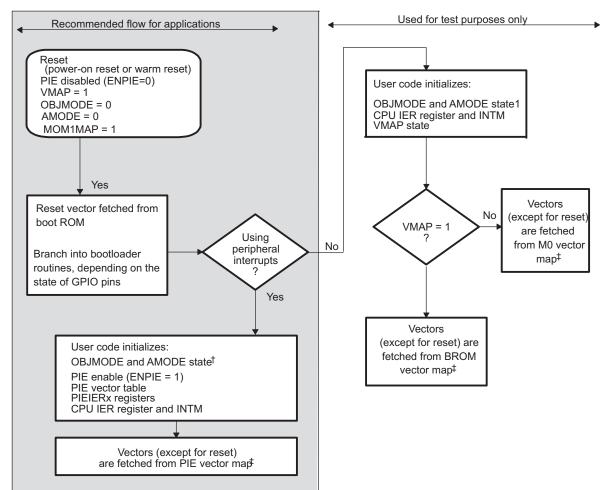

|      |       | 1.5.2                         | Vector Table Mapping                                               |           |  |  |  |

|      |       | 1.5.3                         | Interrupt Sources                                                  |           |  |  |  |

|      |       | 1.5.4                         | PIE Configuration Registers                                        | 139       |  |  |  |

|      |       | 1.5.5                         | PIE Interrupt Registers                                            |           |  |  |  |

|      |       | 1.5.6                         | External Interrupt Control Registers                               |           |  |  |  |

|      | 1.6   | VREG                          | /BOR/POR                                                           |           |  |  |  |

|      |       | 1.6.1                         | On-chip Voltage Regulator (VREG)                                   |           |  |  |  |

|      |       | 1.6.2                         | On-chip Power-On Reset (POR) and Brown-Out Reset (BOR) Circuit     |           |  |  |  |

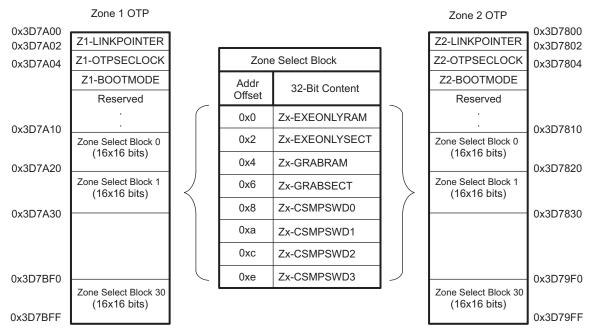

|      | 1.7   | Dual C                        | Code Security Module (DCSM)                                        |           |  |  |  |

|      |       | 1.7.1                         | Functional Description                                             | 151       |  |  |  |

|      |       | 1.7.2                         |                                                                    | 157       |  |  |  |

|      |       | 1.7.3                         | Safe Copy Code                                                     |           |  |  |  |

|      |       | 1.7.4                         | DCSM Impact on Other On-Chip Resources                             |           |  |  |  |

|      |       | 1.7.5                         | Incorporating Code Security in User Applications                   |           |  |  |  |

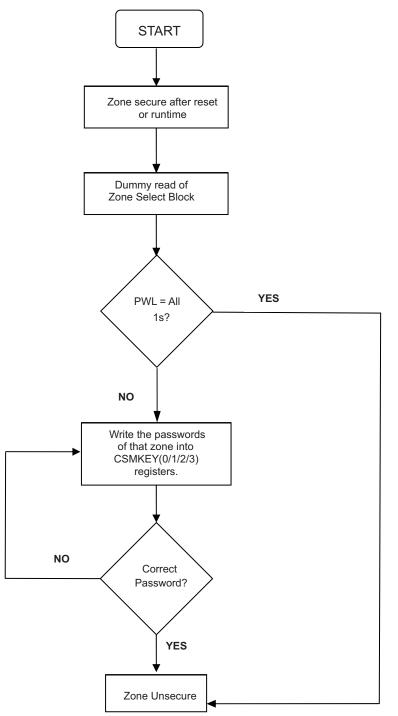

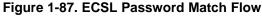

|      |       | 1.7.6                         | Unsecuring a Zone with Security Enabled (DCSM Password Match Flow) |           |  |  |  |

|      |       | 1.7.7                         | Unsecuring a Zone with Security Disabled                           |           |  |  |  |

|      |       | 1.7.8                         | Environments That Require ECSL Unlocking                           |           |  |  |  |

|      |       | 1.7.9                         | Disabling the ECSL (ECSL Password Match Flow)                      | 162       |  |  |  |

|   |      | 1.7.10         | Do's and Don'ts to Protect Security Logic                         | 164               |

|---|------|----------------|-------------------------------------------------------------------|-------------------|

|   |      | 1.7.11         | Dual Code Security Module Disclaimer                              |                   |

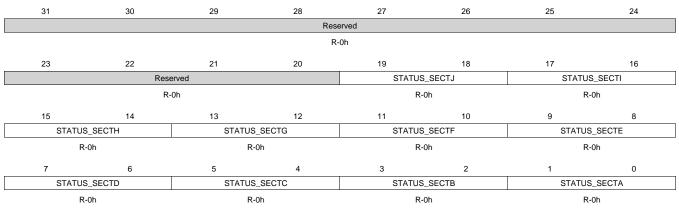

|   | 1.8  | DCSM           | Registers                                                         | 165               |

|   |      | 1.8.1          | DCSM_OTP_Z1 DCSM Registers                                        | 165               |

|   |      | 1.8.2          | DCSM_OTP_Z2 DCSM Registers                                        | 168               |

|   |      | 1.8.3          | DCSM_REGS_COMMON DCSM Registers                                   | 171               |

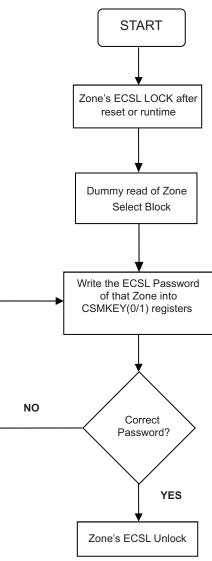

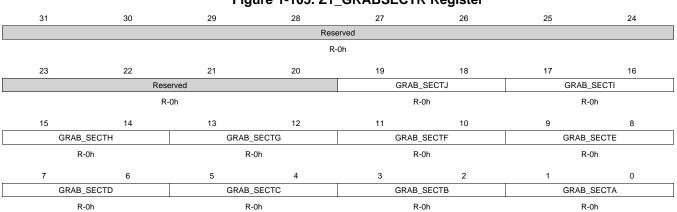

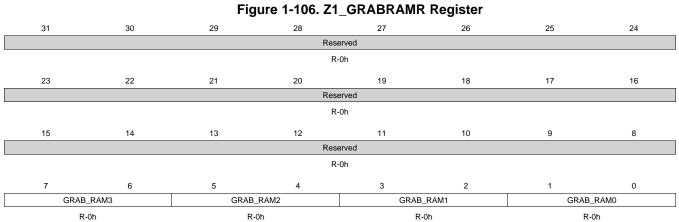

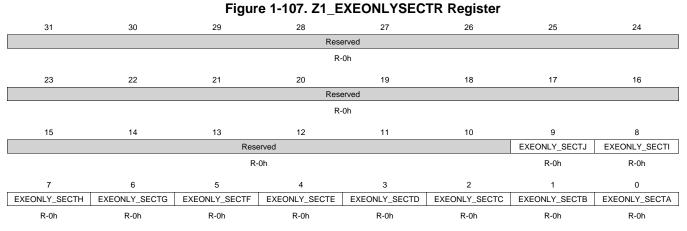

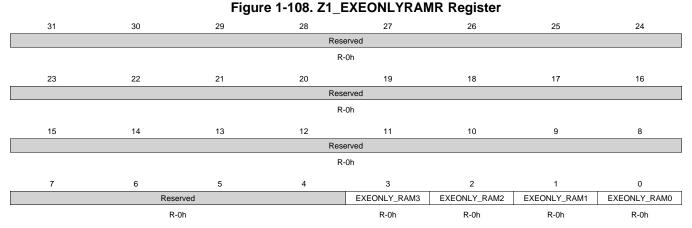

|   |      | 1.8.4          | DCSM_REGS_Z1 DCSM Registers                                       | 175               |

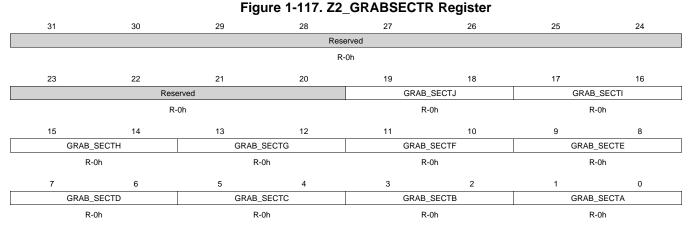

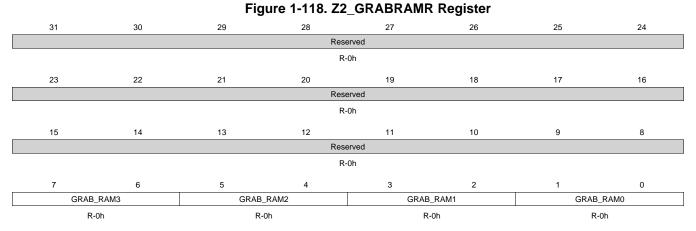

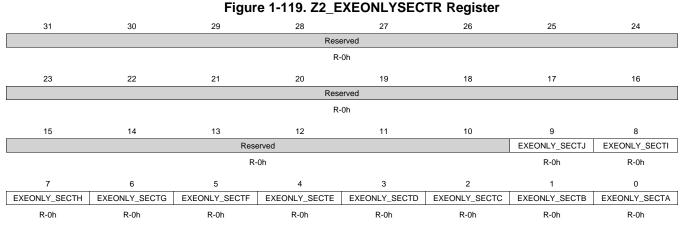

|   |      | 1.8.5          | DCSM_REGS_Z2 DCSM Registers                                       | 190               |

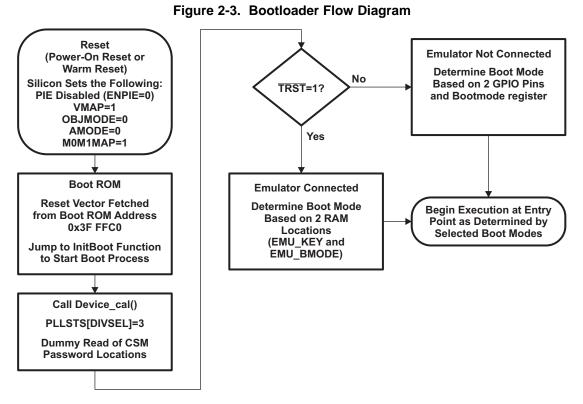

| 2 | ROM  | Code a         | and Peripheral Booting                                            | 206               |

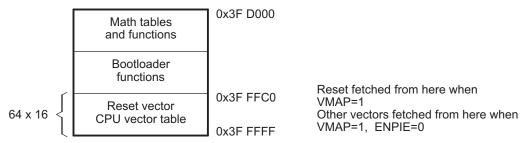

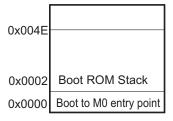

|   | 2.1  |                | OM                                                                |                   |

|   |      | 2.1.1          | On-Chip Boot ROM IQmath Tables                                    | 208               |

|   |      | 2.1.2          | On-Chip Boot ROM IQmath Functions                                 | 209               |

|   |      | 2.1.3          | On-Chip Flash API                                                 | 210               |

|   |      | 2.1.4          | CPU Vector Table                                                  | 210               |

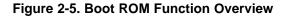

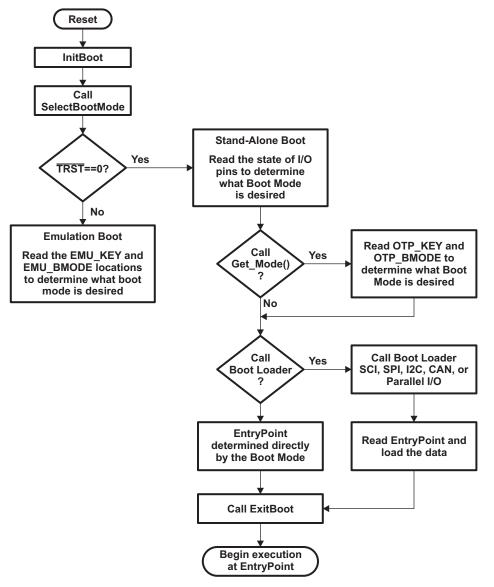

|   |      | 2.1.5          | Bootloader Features                                               | 212               |

|   |      | 2.1.6          | Building the Boot Table                                           | 249               |

|   |      | 2.1.7          | Bootloader Code Overview                                          | 253               |

|   | 2.2  | CLA D          | ATA ROM                                                           | 254               |

|   |      | 2.2.1          | On-Chip CLA Data ROM Math Tables                                  | 254               |

|   |      | 2.2.2          | CLA DataROM Version and Checksum                                  | 255               |

|   | 2.3  | Secure         | • ROM                                                             | 256               |

|   |      | 2.3.1          | Safe Copy code Functions (Z1 and Z2)                              | 256               |

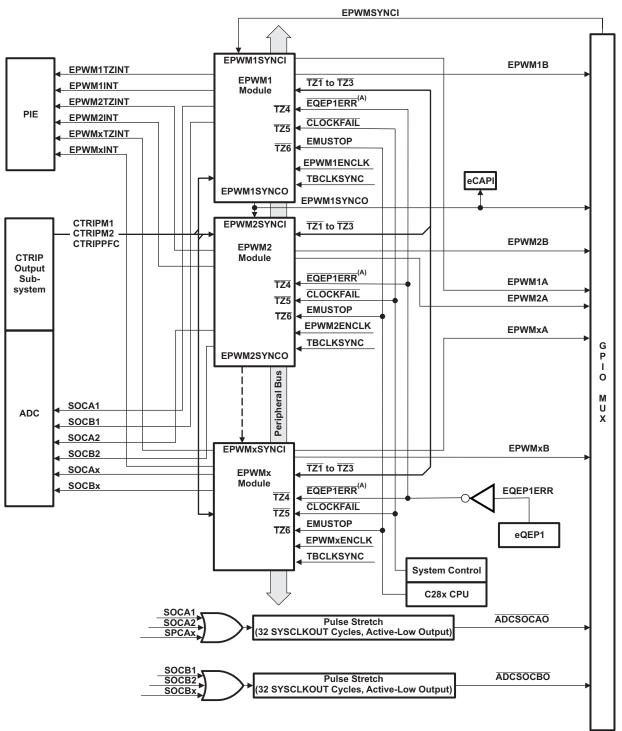

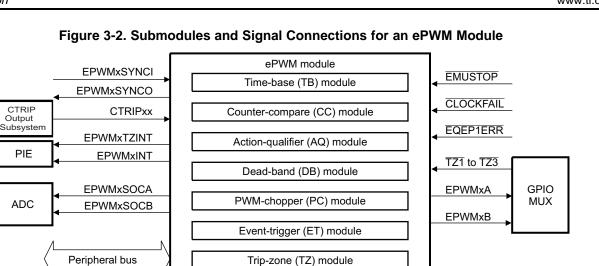

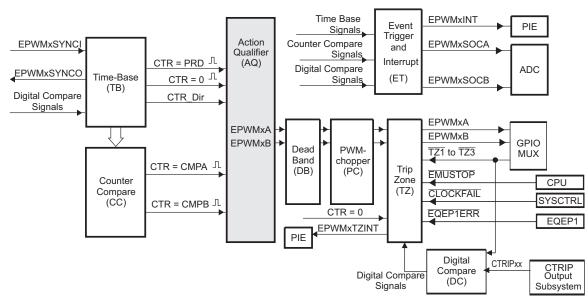

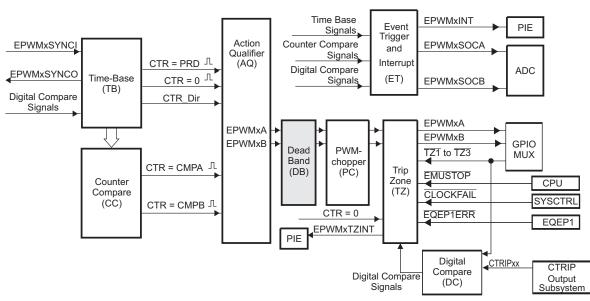

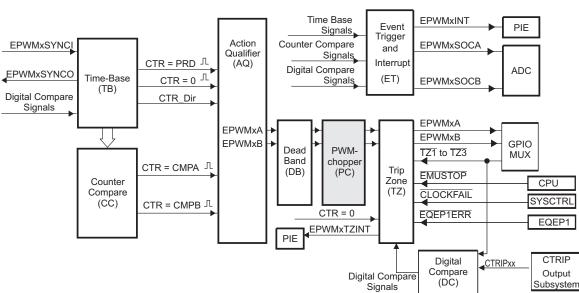

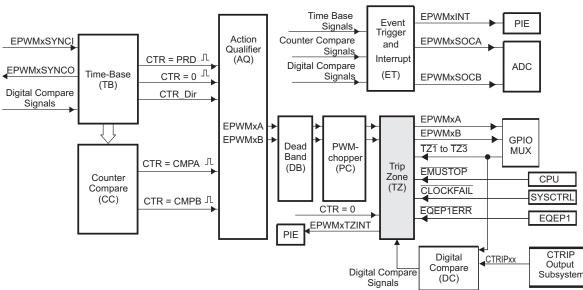

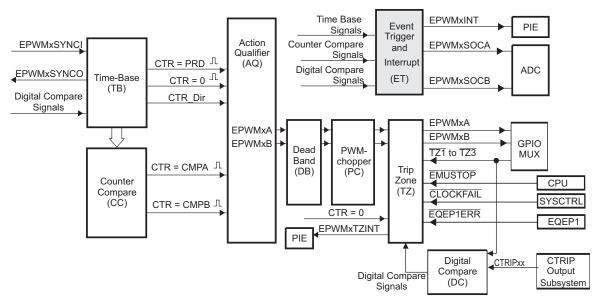

| 3 | Enha | nced P         | Pulse Width Modulator (ePWM) Module                               | 257               |

|   | 3.1  |                |                                                                   |                   |

|   |      | 3.1.1          | Submodule Overview                                                | 258               |

|   |      | 3.1.2          | Register Mapping                                                  | 261               |

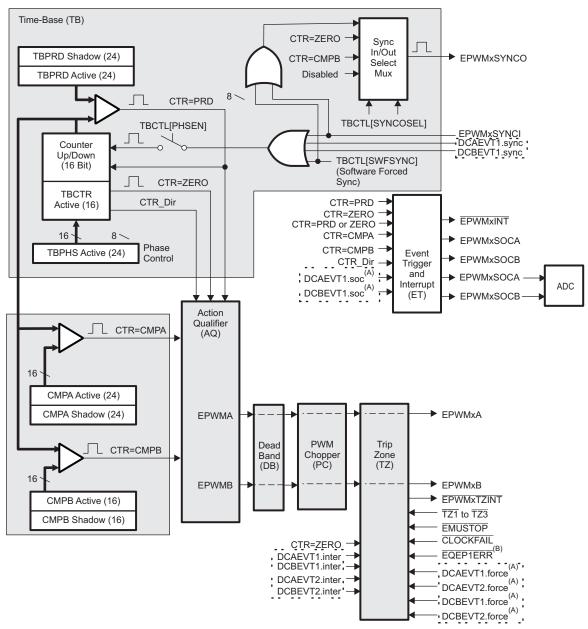

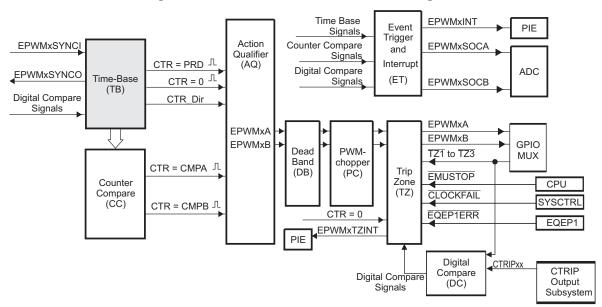

|   | 3.2  | ePWM           | Submodules                                                        | 264               |

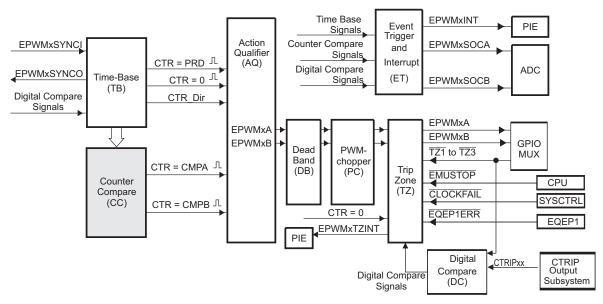

|   |      | 3.2.1          | Overview                                                          | 264               |

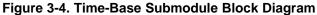

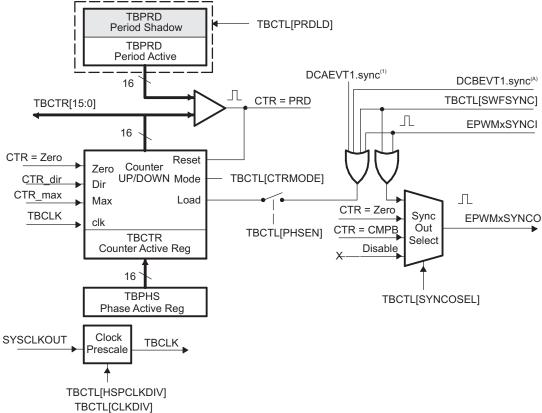

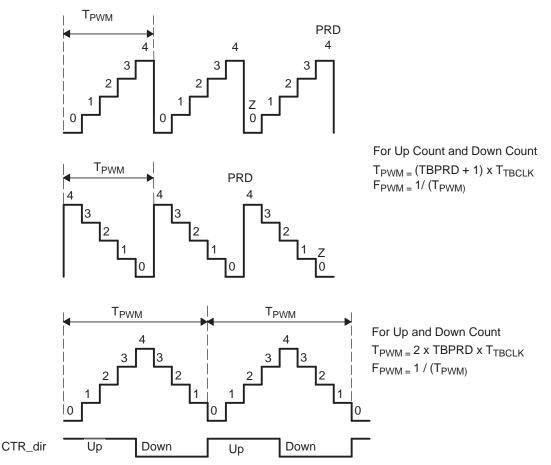

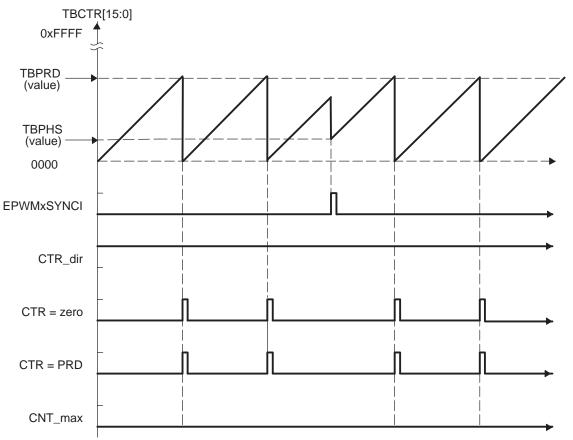

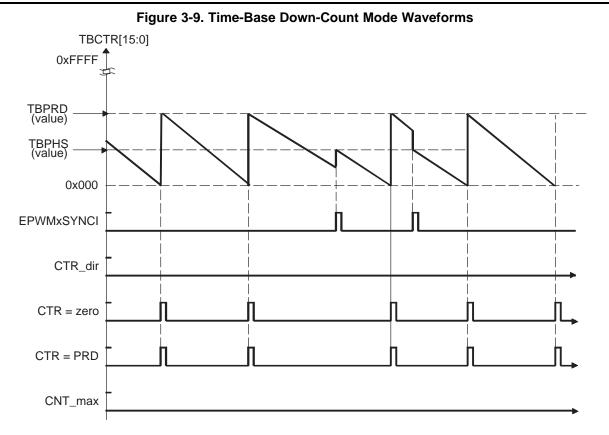

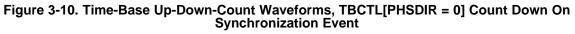

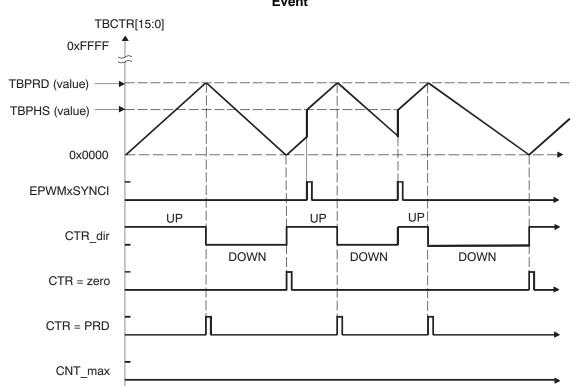

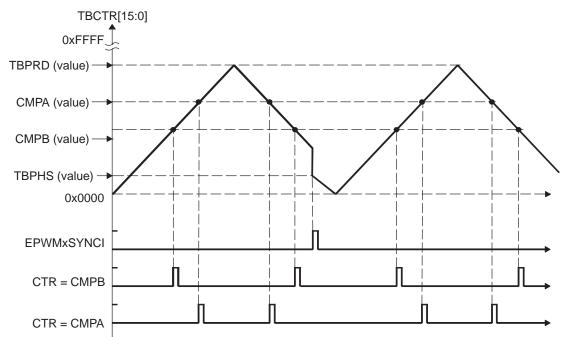

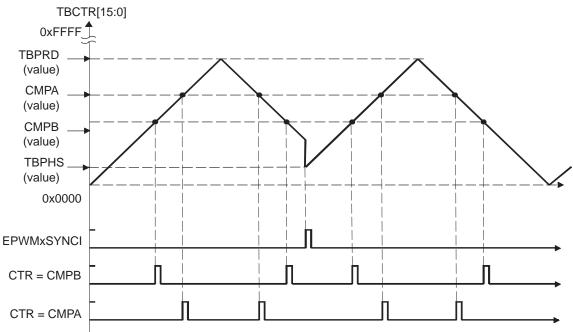

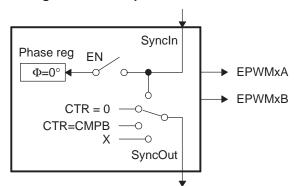

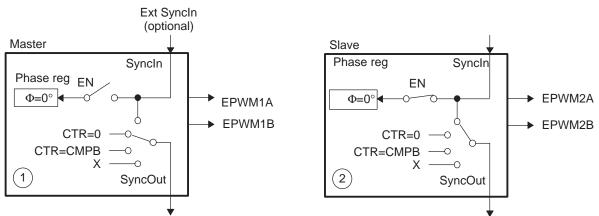

|   |      | 3.2.2          | Time-Base (TB) Submodule                                          | 266               |

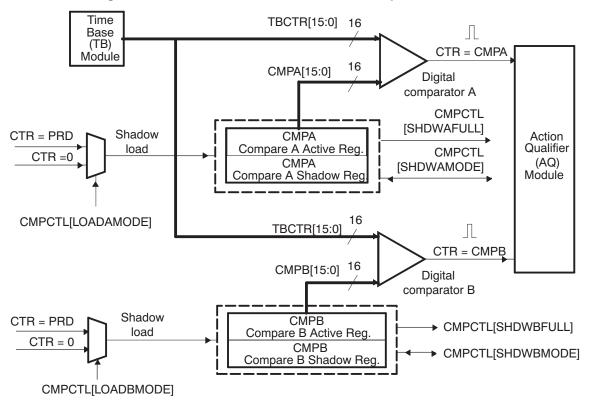

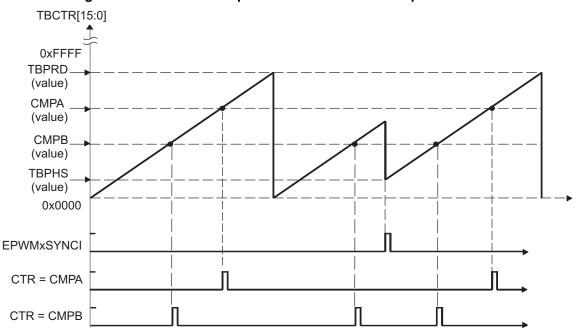

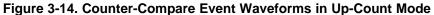

|   |      | 3.2.3          | Counter-Compare (CC) Submodule                                    | 274               |

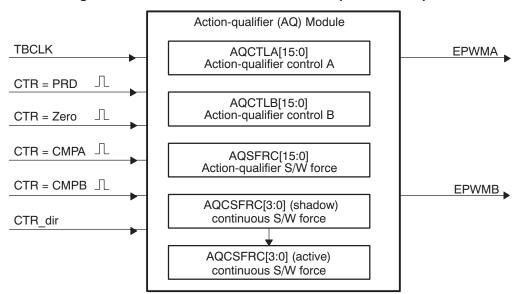

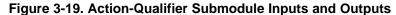

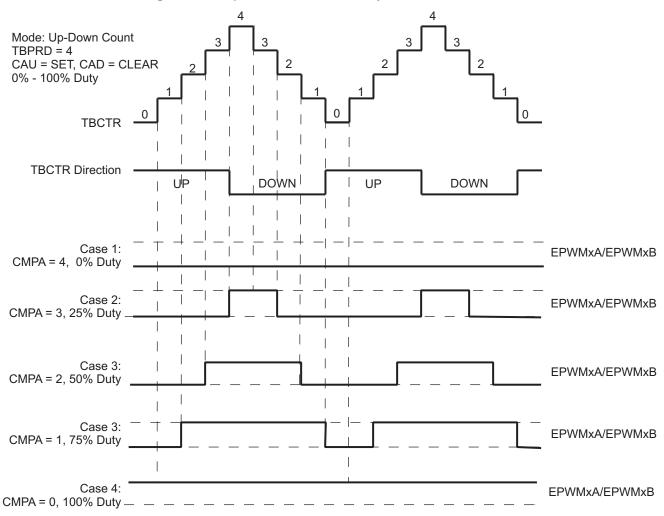

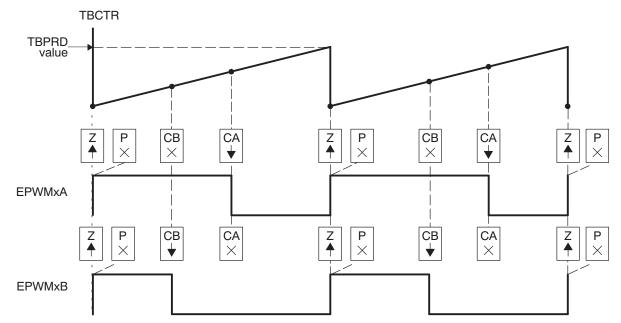

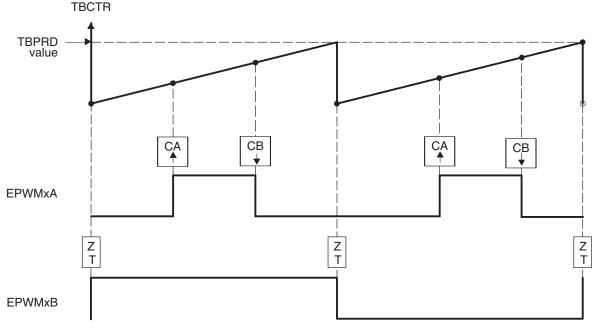

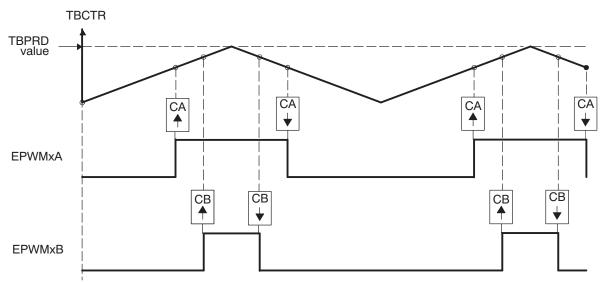

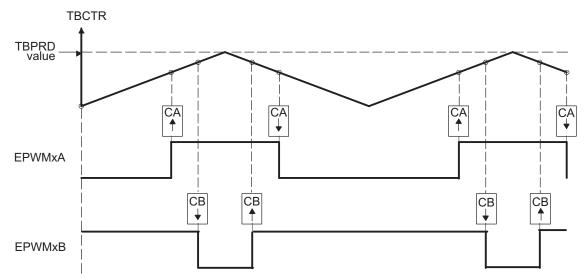

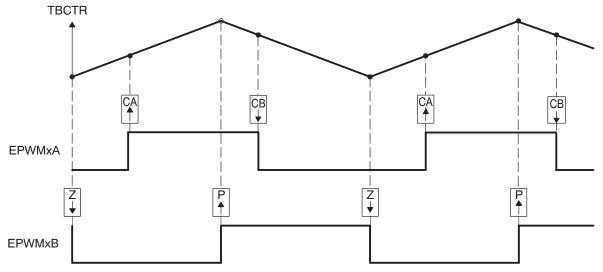

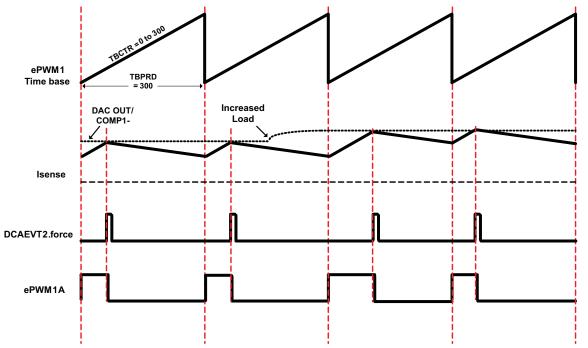

|   |      | 3.2.4          | Action-Qualifier (AQ) Submodule                                   | 279               |

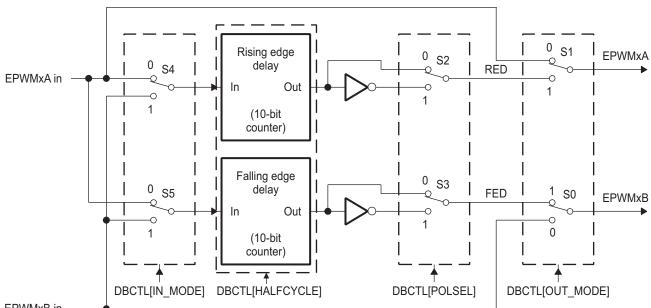

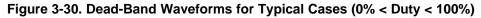

|   |      | 3.2.5          | Dead-Band Generator (DB) Submodule                                | 293               |

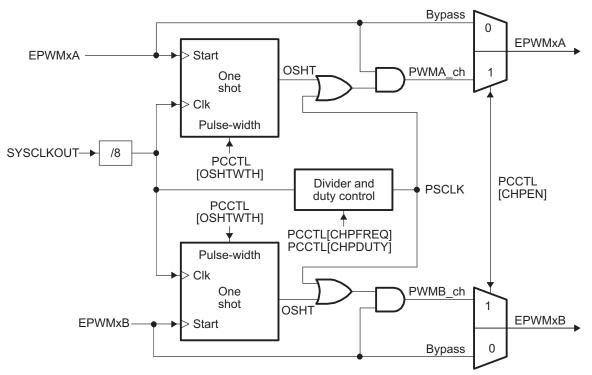

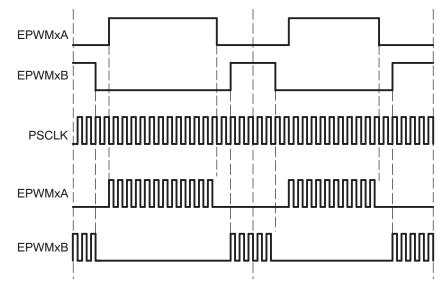

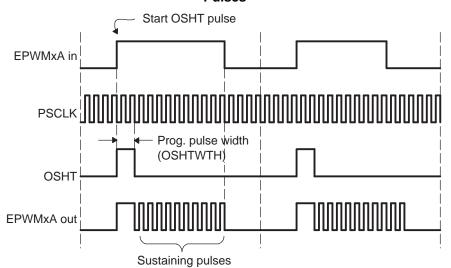

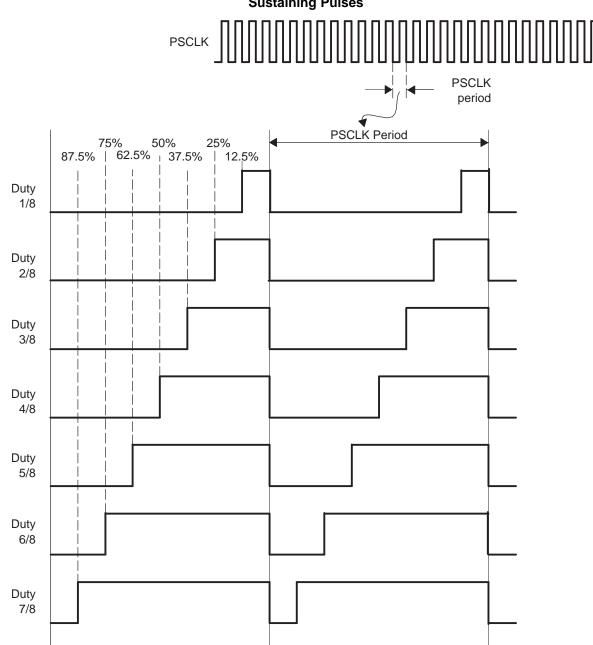

|   |      | 3.2.6          | PWM-Chopper (PC) Submodule                                        | 298               |

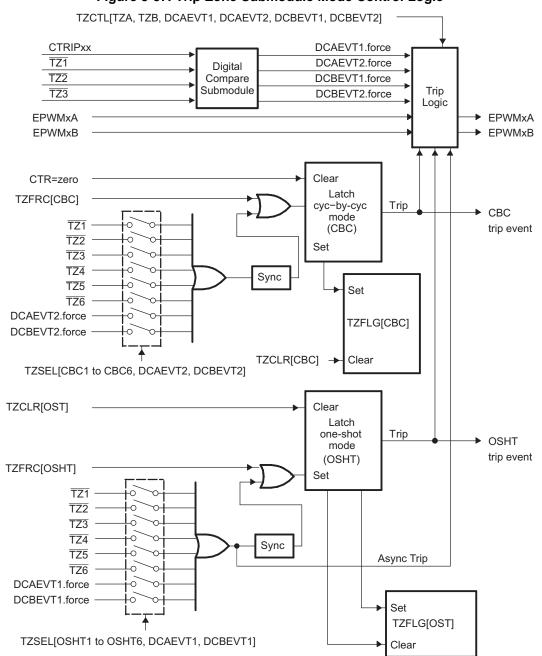

|   |      | 3.2.7          | Trip-Zone (TZ) Submodule                                          | 303               |

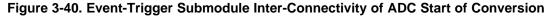

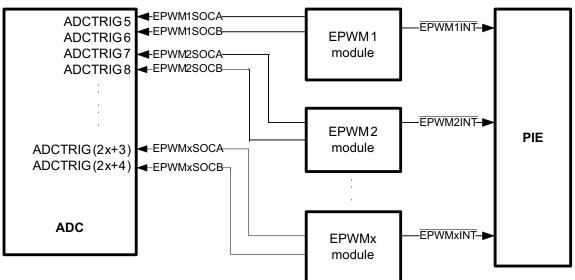

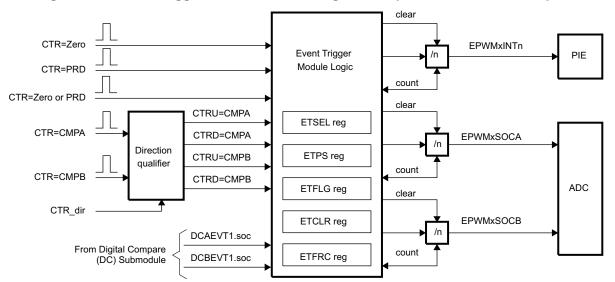

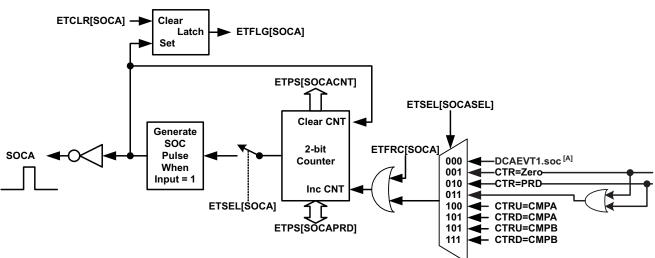

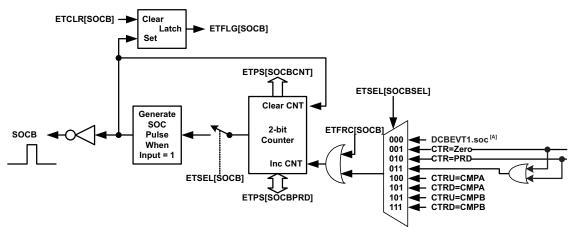

|   |      | 3.2.8          | Event-Trigger (ET) Submodule                                      | 308               |

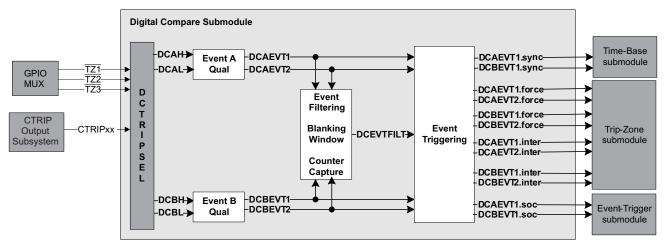

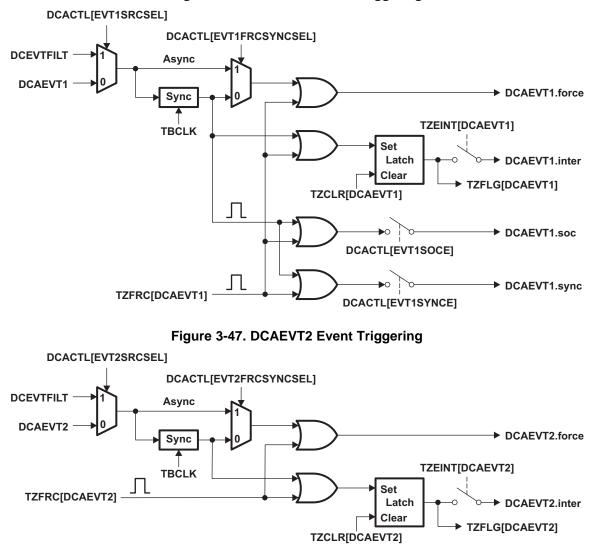

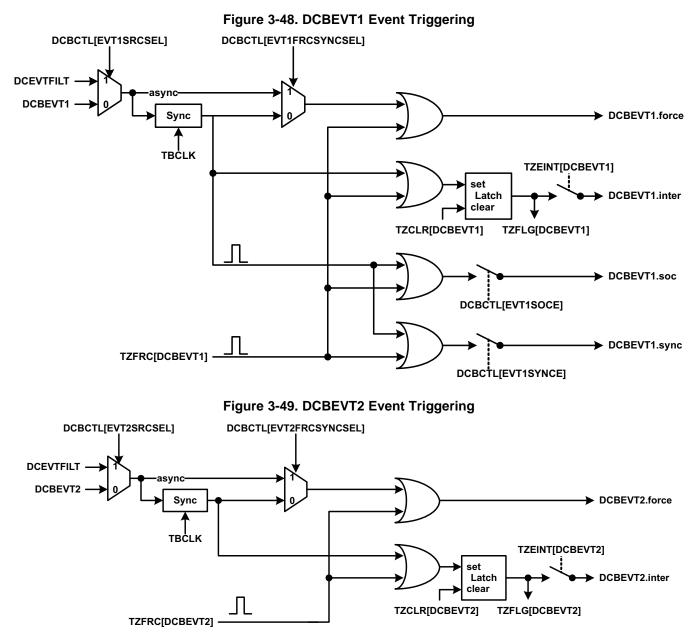

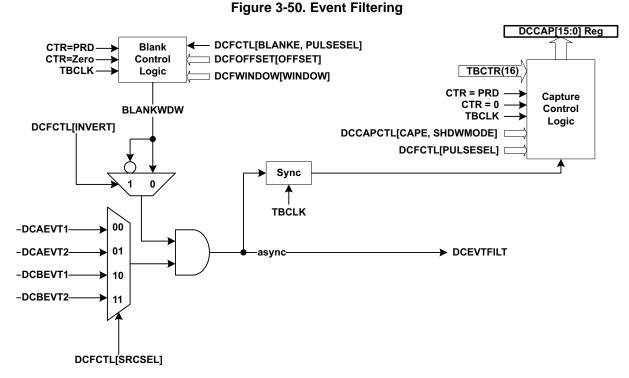

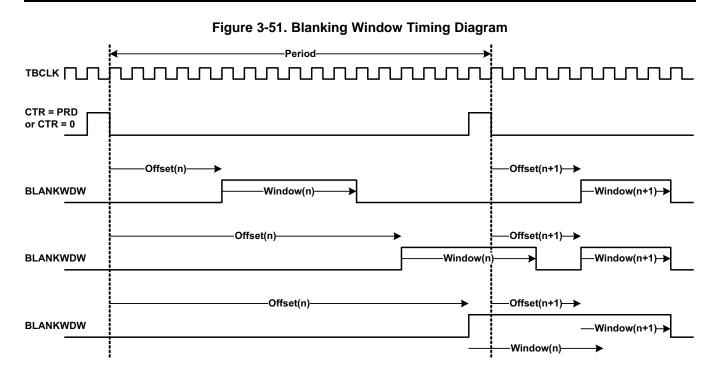

|   |      | 3.2.9          | Digital Compare (DC) Submodule                                    | 312               |

|   | 3.3  | Applica        | ations to Power Topologies                                        | 319               |

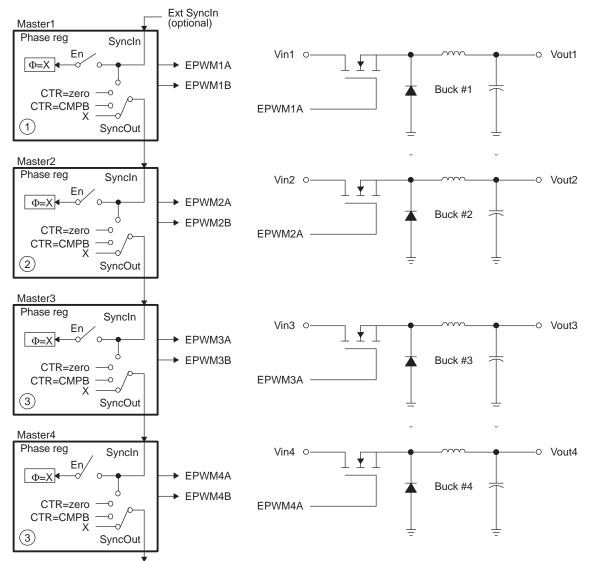

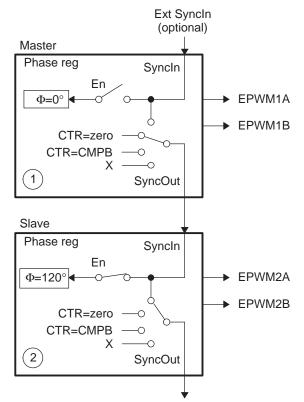

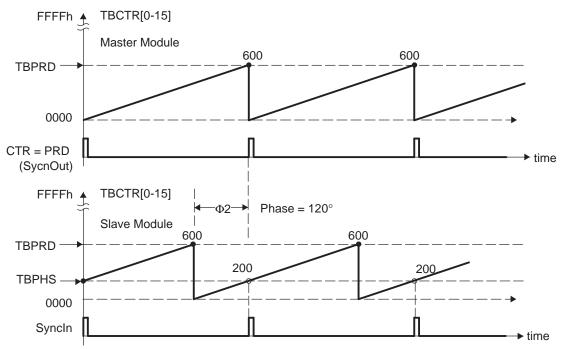

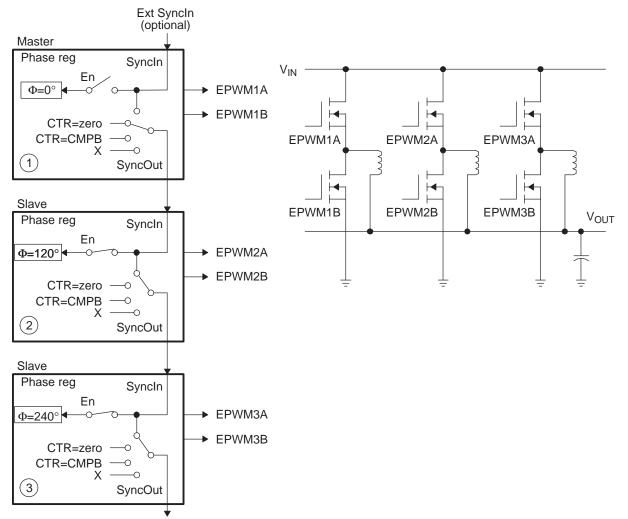

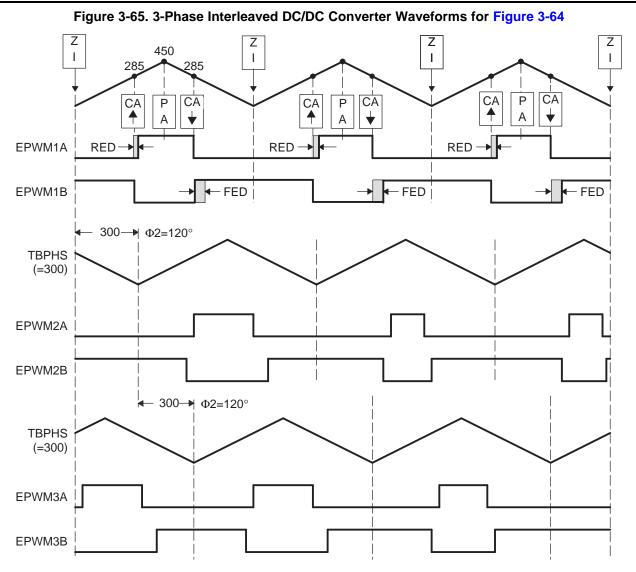

|   |      | 3.3.1          | Overview of Multiple Modules                                      |                   |

|   |      | 3.3.2          | Key Configuration Capabilities                                    | 319               |

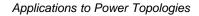

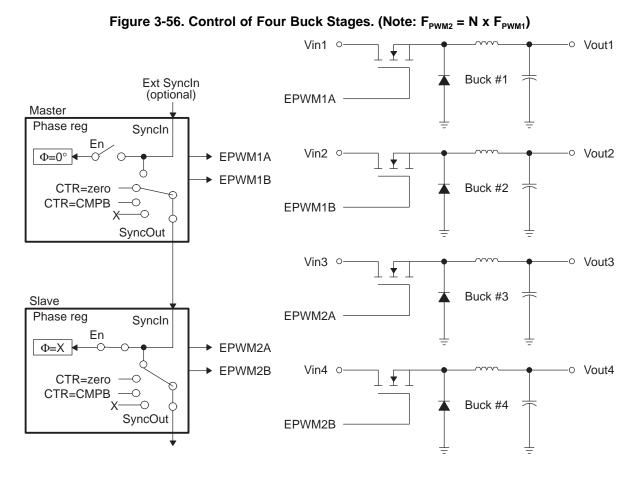

|   |      | 3.3.3          | Controlling Multiple Buck Converters With Independent Frequencies |                   |

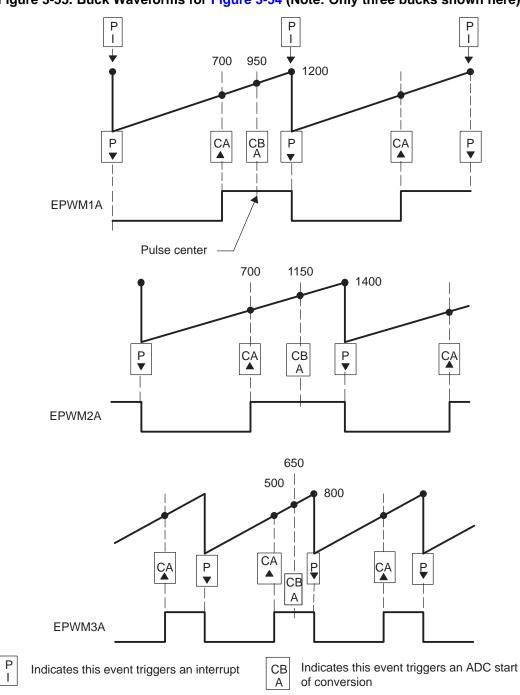

|   |      | 3.3.4          | Controlling Multiple Buck Converters With Same Frequencies        |                   |

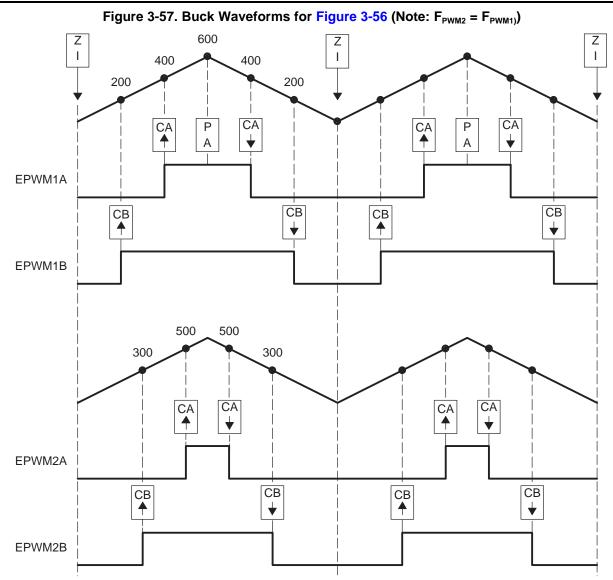

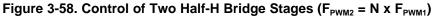

|   |      | 3.3.5          | Controlling Multiple Half H-Bridge (HHB) Converters               |                   |

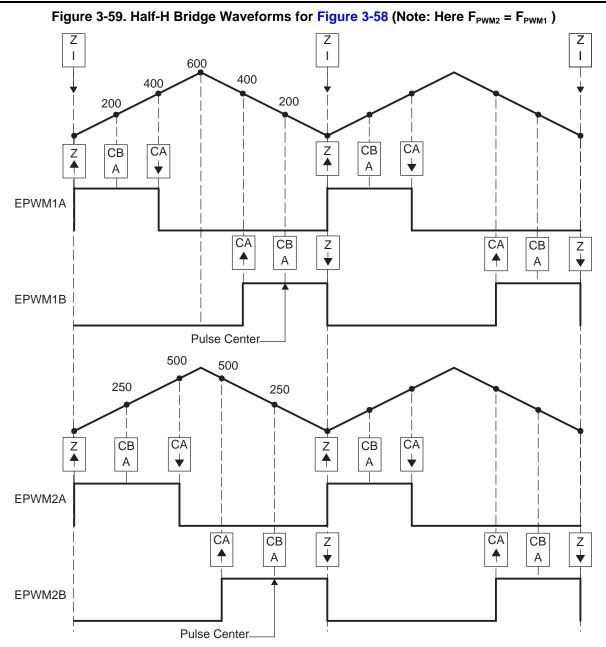

|   |      | 3.3.6          | Controlling Dual 3-Phase Inverters for Motors (ACI and PMSM)      |                   |

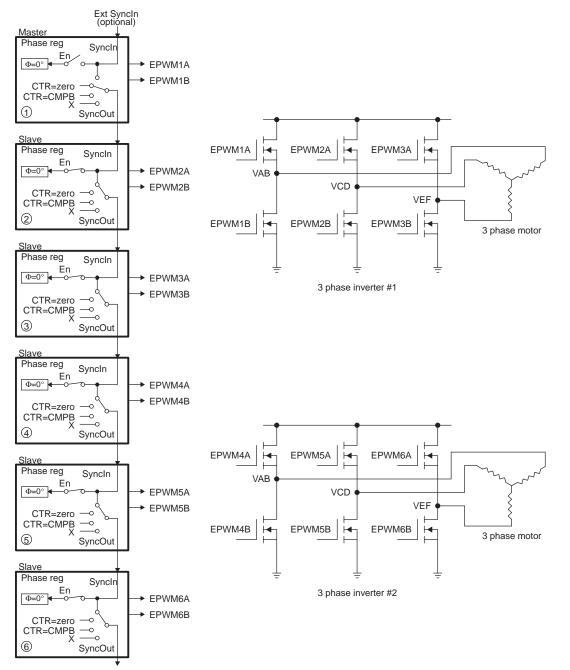

|   |      | 3.3.7          | Practical Applications Using Phase Control Between PWM Modules    |                   |

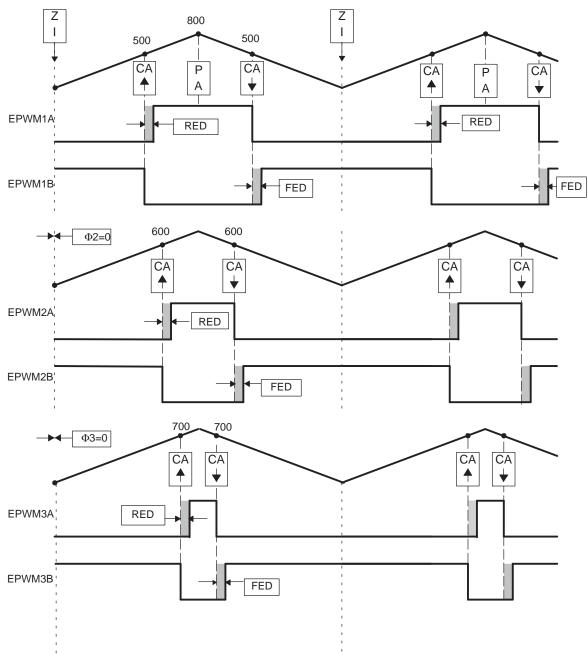

|   |      | 3.3.8          | Controlling a 3-Phase Interleaved DC/DC Converter                 |                   |

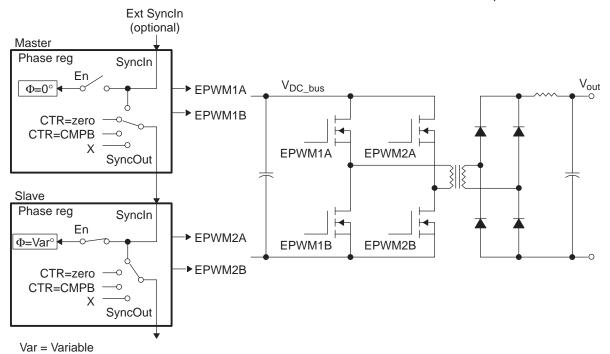

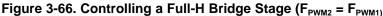

|   |      | 3.3.9          | Controlling Zero Voltage Switched Full Bridge (ZVSFB) Converter   |                   |

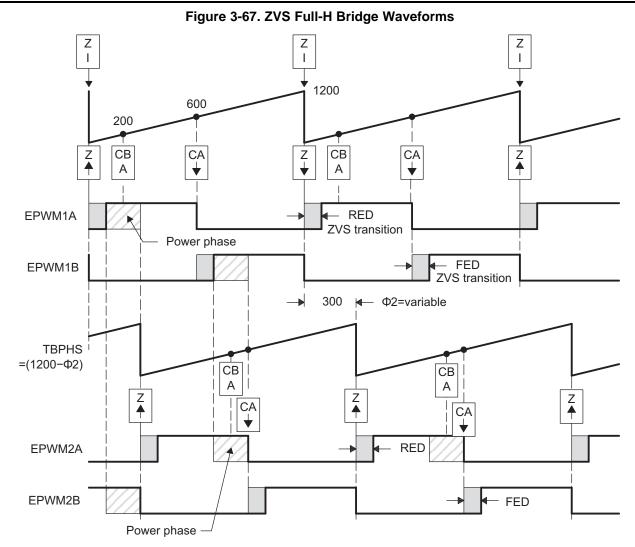

|   |      | 3.3.10         | 5                                                                 |                   |

|   | 3.4  | Regist         |                                                                   |                   |

|   |      |                | Time-Base Submodule Registers                                     | 343               |

|   |      | 3.4.1          | -                                                                 |                   |

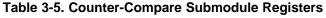

|   |      | 3.4.2          | Counter-Compare Submodule Registers                               | 347               |

|   |      | 3.4.2<br>3.4.3 | Counter-Compare Submodule Registers                               | 347<br>350        |

|   |      | 3.4.2          | Counter-Compare Submodule Registers                               | 347<br>350<br>355 |

| ti.com |  |

|--------|--|

|        |  |

|   |                                                                                          | 3.4.6                                                                                                                                                                                                                                                                                                          | Trip-Zone Submodule Control and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 359                                                                                                                                                                                                     |

|---|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                          | 3.4.7                                                                                                                                                                                                                                                                                                          | Digital Compare Submodule Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 366                                                                                                                                                                                                     |

|   |                                                                                          | 3.4.8                                                                                                                                                                                                                                                                                                          | Event-Trigger Submodule Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 371                                                                                                                                                                                                     |

|   |                                                                                          | 3.4.9                                                                                                                                                                                                                                                                                                          | Proper Interrupt Initialization Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 376                                                                                                                                                                                                     |

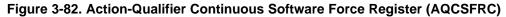

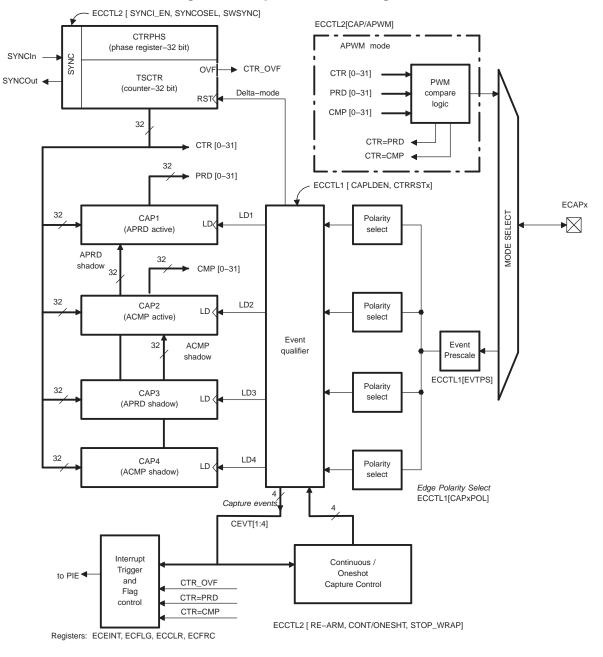

| 4 | Enha                                                                                     | nced C                                                                                                                                                                                                                                                                                                         | Capture (eCAP) Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 377                                                                                                                                                                                                     |

| - | 4.1                                                                                      |                                                                                                                                                                                                                                                                                                                | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                         |

|   | 4.2                                                                                      |                                                                                                                                                                                                                                                                                                                | ption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                         |

|   | 4.3                                                                                      |                                                                                                                                                                                                                                                                                                                | re and APWM Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                         |

|   | 4.4                                                                                      |                                                                                                                                                                                                                                                                                                                | re Mode Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                         |

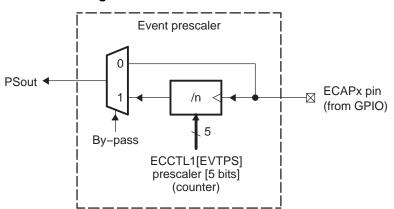

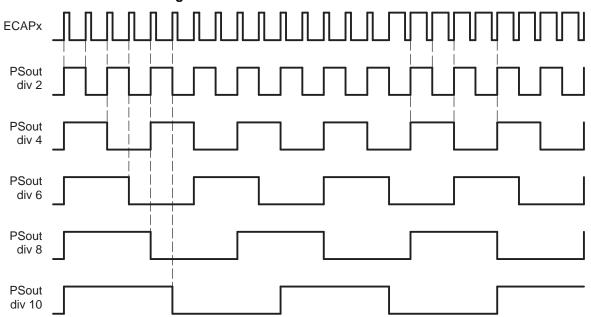

|   |                                                                                          | 4.4.1                                                                                                                                                                                                                                                                                                          | Event Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                         |

|   |                                                                                          | 4.4.2                                                                                                                                                                                                                                                                                                          | Edge Polarity Select and Qualifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                         |

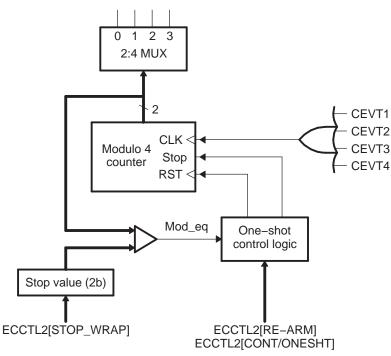

|   |                                                                                          | 4.4.3                                                                                                                                                                                                                                                                                                          | Continuous/One-Shot Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                         |

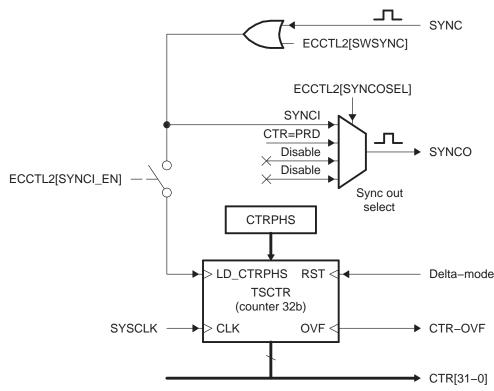

|   |                                                                                          | 4.4.4                                                                                                                                                                                                                                                                                                          | 32-Bit Counter and Phase Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                         |

|   |                                                                                          | 4.4.5                                                                                                                                                                                                                                                                                                          | CAP1-CAP4 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                         |

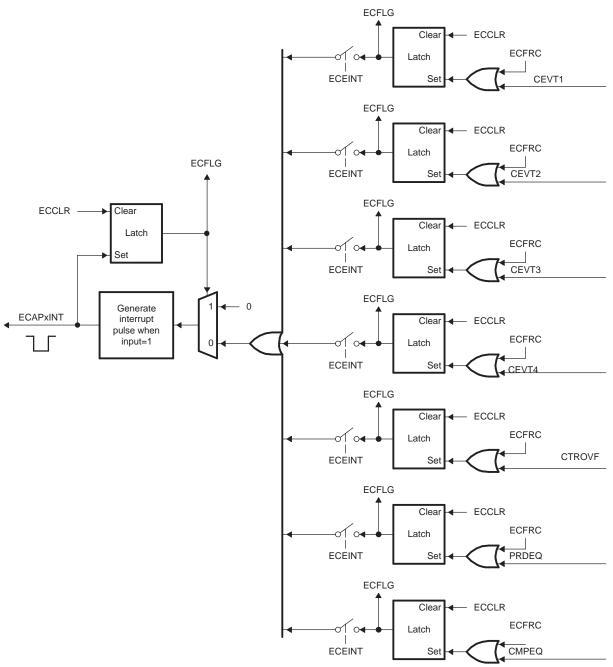

|   |                                                                                          | 4.4.6                                                                                                                                                                                                                                                                                                          | Interrupt Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                         |

|   |                                                                                          | 4.4.7                                                                                                                                                                                                                                                                                                          | Shadow Load and Lockout Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                         |

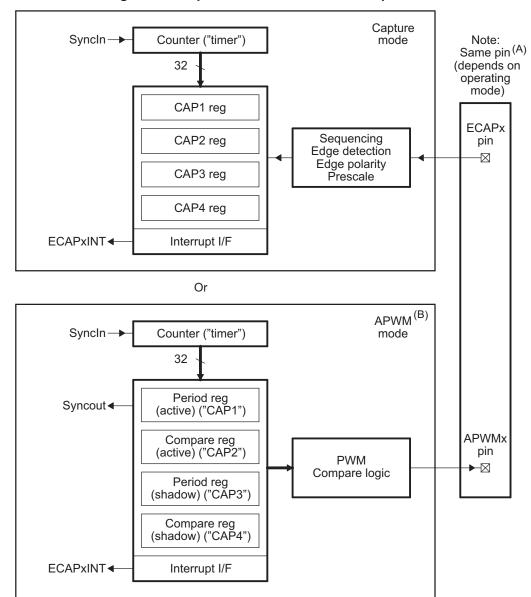

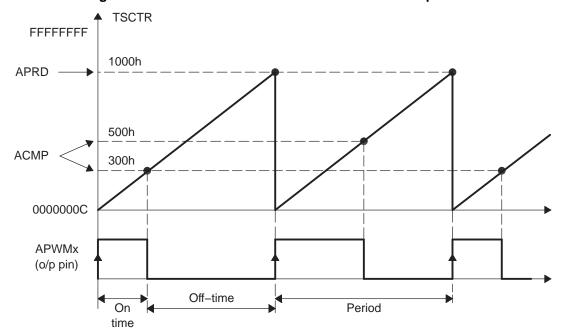

|   |                                                                                          | 4.4.8                                                                                                                                                                                                                                                                                                          | APWM Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 386                                                                                                                                                                                                     |

|   | 4.5                                                                                      | Captu                                                                                                                                                                                                                                                                                                          | re Module - Control and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                         |

|   | 4.6                                                                                      | •                                                                                                                                                                                                                                                                                                              | er Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                         |

|   | 4.7                                                                                      | -                                                                                                                                                                                                                                                                                                              | ation of the ECAP Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                         |

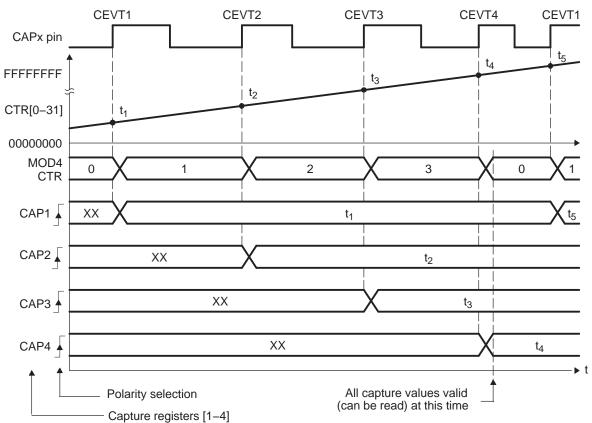

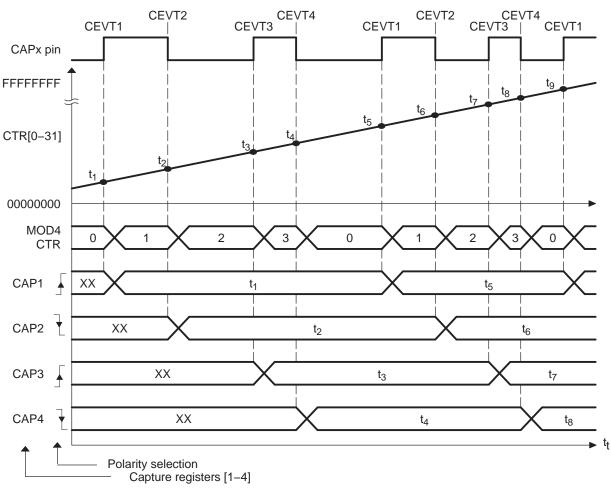

|   |                                                                                          | 4.7.1                                                                                                                                                                                                                                                                                                          | Example 1 - Absolute Time-Stamp Operation Rising Edge Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 396                                                                                                                                                                                                     |

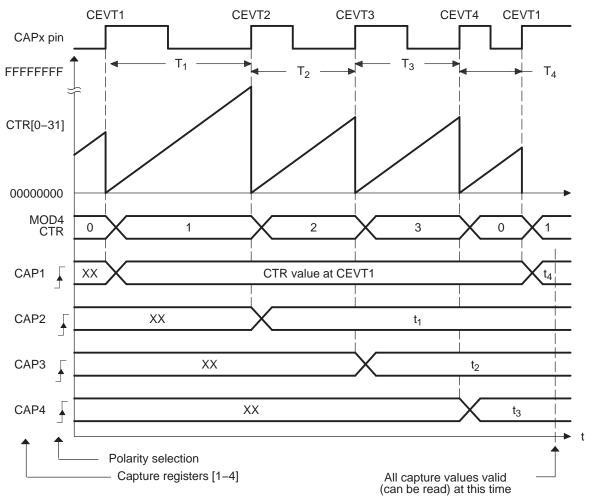

|   |                                                                                          | 4.7.2                                                                                                                                                                                                                                                                                                          | Example 2 - Absolute Time-Stamp Operation Rising and Falling Edge Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 399                                                                                                                                                                                                     |

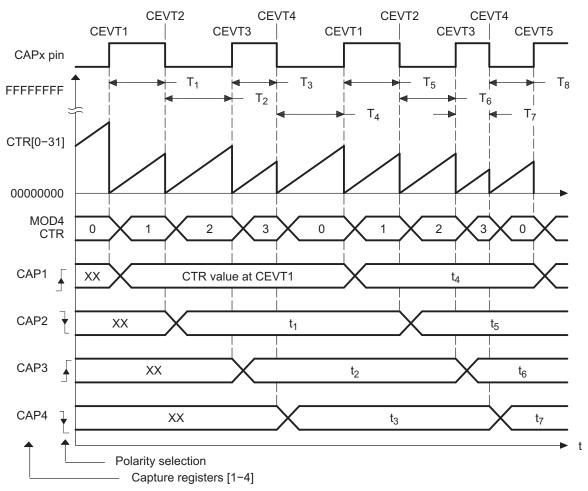

|   |                                                                                          | 4.7.3                                                                                                                                                                                                                                                                                                          | Example 3 - Time Difference (Delta) Operation Rising Edge Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 401                                                                                                                                                                                                     |

|   |                                                                                          | 4.7.4                                                                                                                                                                                                                                                                                                          | Example 4 - Time Difference (Delta) Operation Rising and Falling Edge Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 403                                                                                                                                                                                                     |

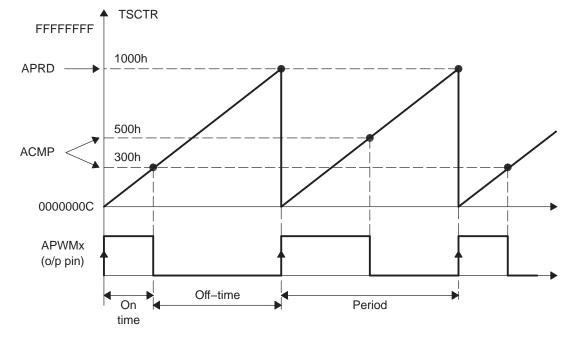

|   | 4.8                                                                                      | Applic                                                                                                                                                                                                                                                                                                         | ation of the APWM Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 405                                                                                                                                                                                                     |

|   |                                                                                          | 4.8.1                                                                                                                                                                                                                                                                                                          | Example 1 - Simple PWM Generation (Independent Channel/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 405                                                                                                                                                                                                     |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                         |

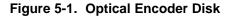

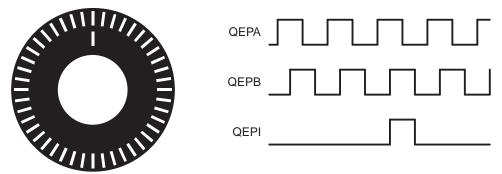

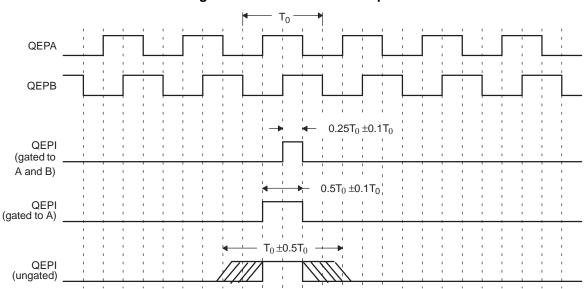

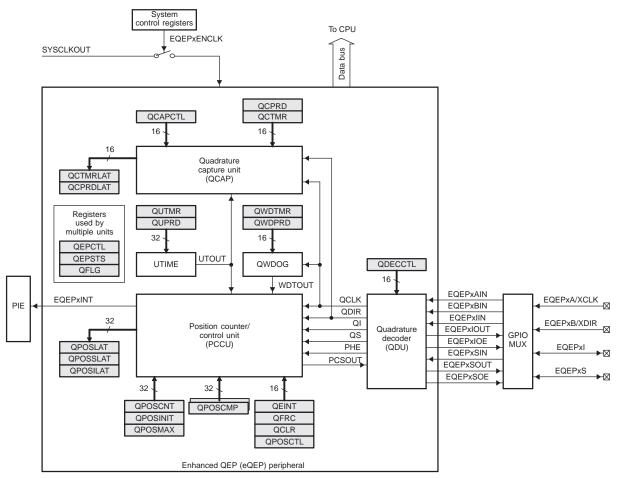

| 5 | Enha                                                                                     | nced C                                                                                                                                                                                                                                                                                                         | QEP (eQEP) Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>407</b>                                                                                                                                                                                              |

| 5 | <b>Enha</b><br>5.1                                                                       |                                                                                                                                                                                                                                                                                                                | QEP (eQEP) Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                         |

| 5 |                                                                                          | Introdu                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 408                                                                                                                                                                                                     |

| 5 | 5.1                                                                                      | Introdu                                                                                                                                                                                                                                                                                                        | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 408<br>410                                                                                                                                                                                              |

| 5 | 5.1                                                                                      | Introdu<br>Descri                                                                                                                                                                                                                                                                                              | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 408<br>410<br>410                                                                                                                                                                                       |

| 5 | 5.1                                                                                      | Introdu<br>Descri<br>5.2.1                                                                                                                                                                                                                                                                                     | uction<br>ption<br>EQEP Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 408<br>410<br>410<br>411                                                                                                                                                                                |

| 5 | 5.1                                                                                      | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3                                                                                                                                                                                                                                                                   | eQEP Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 408<br>410<br>410<br>411<br>412<br>413                                                                                                                                                                  |

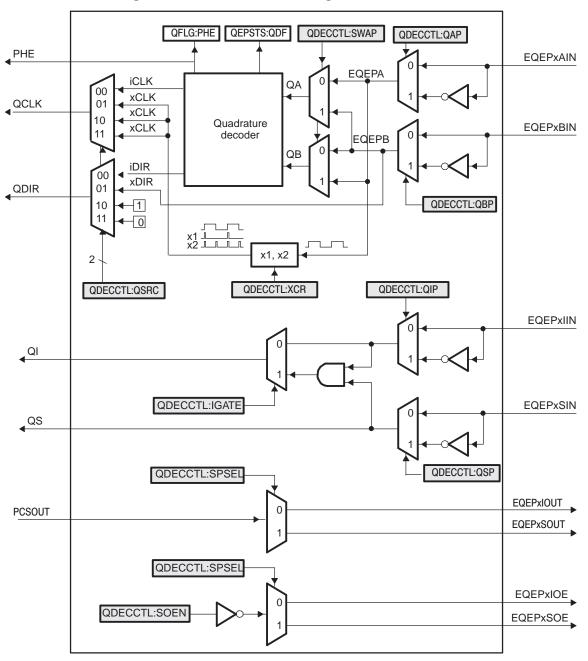

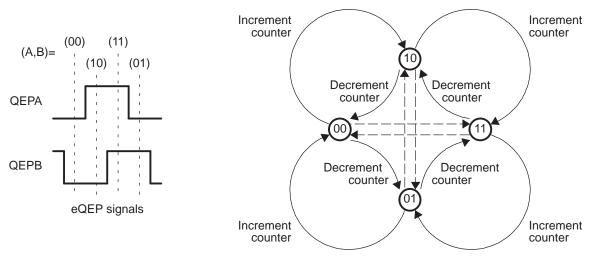

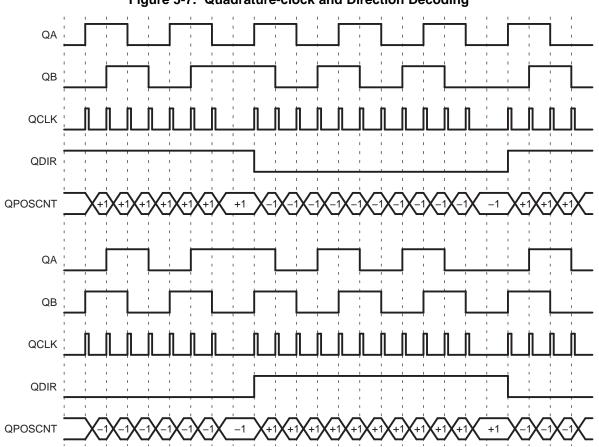

| 5 | 5.1<br>5.2                                                                               | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3                                                                                                                                                                                                                                                                   | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 408<br>410<br>410<br>411<br>412<br>413<br>413                                                                                                                                                           |

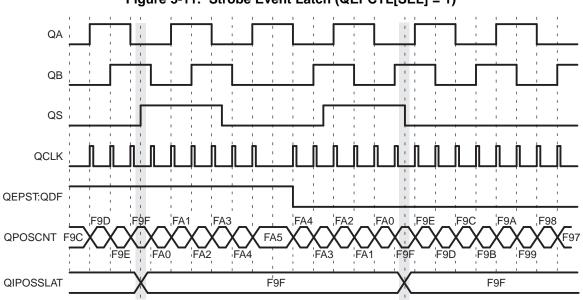

| 5 | 5.1<br>5.2                                                                               | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2                                                                                                                                                                                                                                        | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 408<br>410<br>411<br>412<br>413<br>413<br>413                                                                                                                                                           |

| 5 | 5.1<br>5.2                                                                               | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3                                                                                                                                                                                                                               | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 408<br>410<br>411<br>412<br>413<br>413<br>413<br>416<br>416                                                                                                                                             |

| 5 | 5.1<br>5.2                                                                               | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3                                                                                                                                                                                                                               | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output         on Counter and Control Unit (PCCU)                                                                                                                                                                                                                                                                                                                                                                                                        | 408<br>410<br>411<br>412<br>413<br>413<br>413<br>416<br>416<br>416                                                                                                                                      |

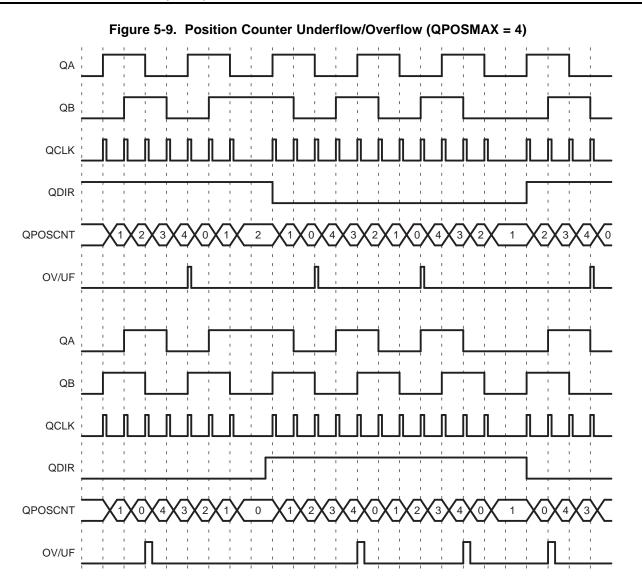

| 5 | 5.1<br>5.2<br>5.3                                                                        | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3                                                                                                                                                                                                                               | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output         on Counter and Control Unit (PCCU)         Position Counter Operating Modes                                                                                                                                                                                                                                                                                                                                                               | 408<br>410<br>411<br>412<br>413<br>413<br>413<br>416<br>416<br>416                                                                                                                                      |

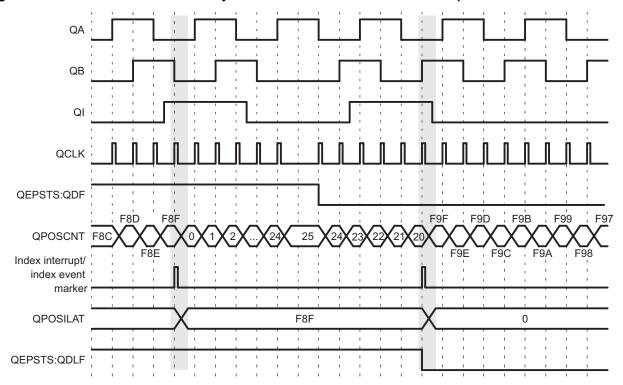

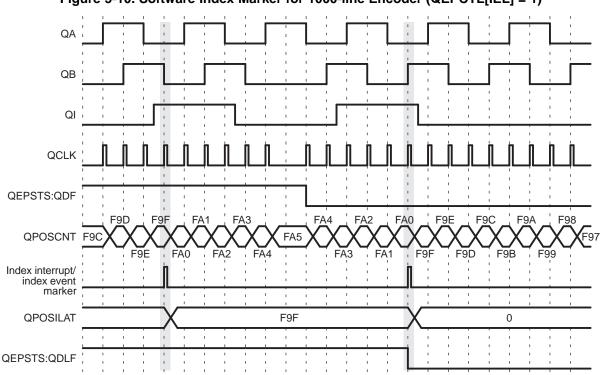

| 5 | 5.1<br>5.2<br>5.3                                                                        | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2                                                                                                                                                                                                  | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output         on Counter operating Modes         Position Counter Latch                                                                                                                                                                                                                                                                                                                                                                                 | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>419                                                                                                                               |

| 5 | 5.1<br>5.2<br>5.3                                                                        | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1                                                                                                                                                                                                           | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output         on Counter and Control Unit (PCCU)         Position Counter Operating Modes         Position Counter Initialization                                                                                                                                                                                                                                                                                                                       | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>419<br>421                                                                                                                        |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                 | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4                                                                                                                                                                                | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output         on Counter and Control Unit (PCCU)         Position Counter Inputation         Position Counter Initialization         eQEP Position-compare Unit                                                                                                                                                                                                                                                                                         | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>421                                                                                                          |

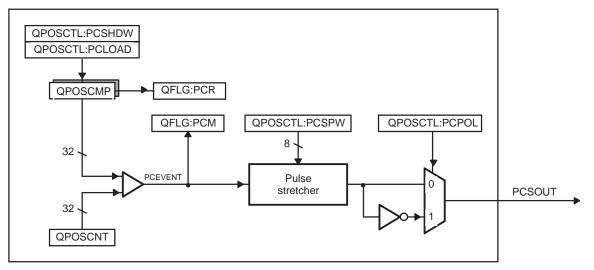

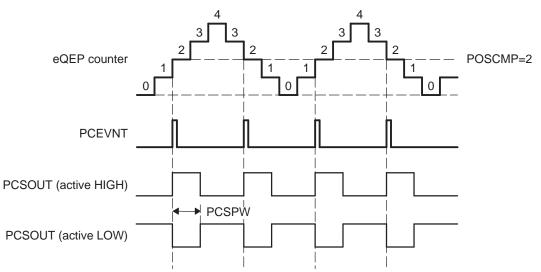

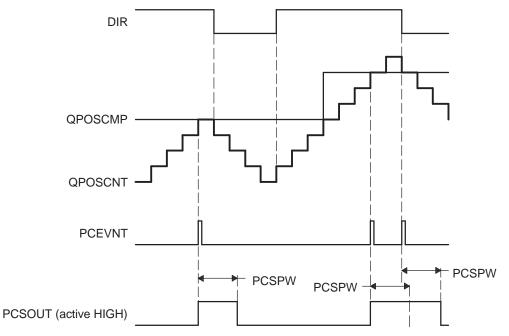

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li><li>5.5</li></ul>                    | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP                                                                                                                                                                        | uction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output         on Counter and Control Unit (PCCU)         Position Counter Operating Modes         Position Counter Initialization         eQEP Position-compare Unit                                                                                                                                                                                                                                                                                    | 408<br>410<br>411<br>412<br>413<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>421<br>423                                                                                     |

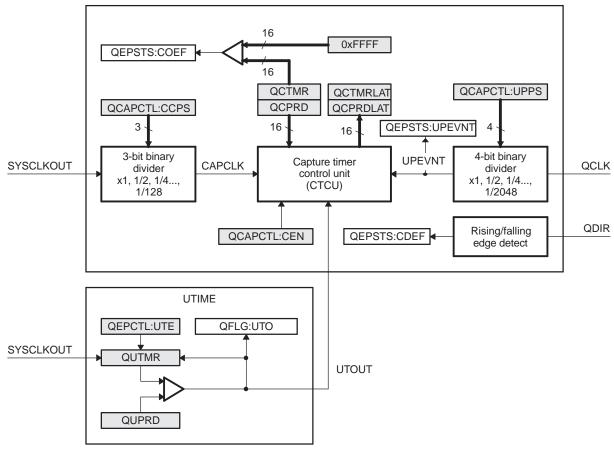

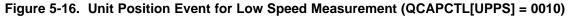

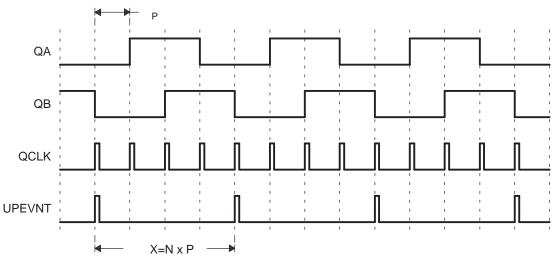

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ul> | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP<br>eQEP                                                                                                                                                                | Juction         ption         EQEP Inputs         Functional Description         eQEP Memory Map         ature Decoder Unit (QDU)         Position Counter Input Modes         eQEP Input Polarity Selection         Position-Compare Sync Output         on Counter and Control Unit (PCCU)         Position Counter Inputation         eQEP Position-compare Unit         Equation         Position Counter Initialization         eQEP Position-compare Unit         Edge Capture Unit         Watchdog                                                                                                                                                                                         | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>421<br>423<br>426                                                                                     |

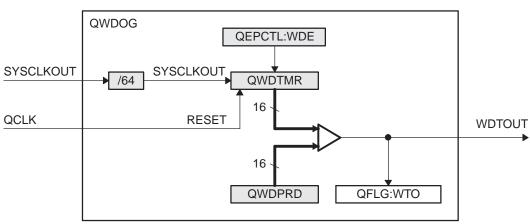

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                            | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP<br>Unit Ti                                                                                                                                                             | Juction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>421<br>423<br>426<br>426                                                                              |

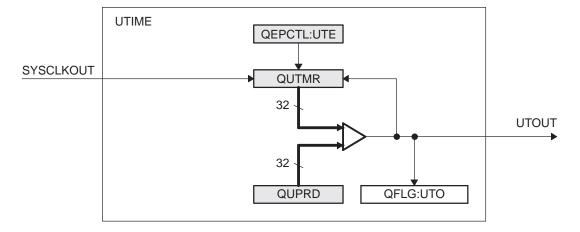

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                     | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP<br>eQEP<br>Unit Ti<br>eQEP                                                                                                                                             | Juction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>421<br>421<br>426<br>426<br>427                                                                       |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                            | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP<br>eQEP<br>Unit Ti<br>eQEP                                                                                                                                             | Juction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>421<br>421<br>426<br>426<br>427                                                                       |

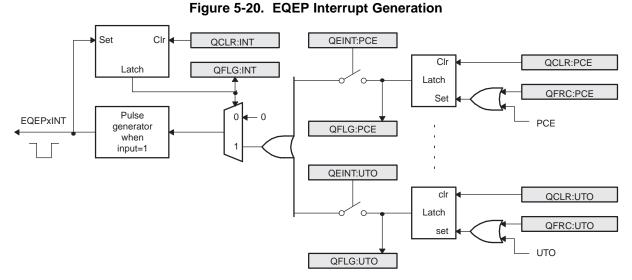

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                              | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP<br>eQEP<br>Unit Ti<br>eQEP<br>eQEP                                                                                                                                     | Juction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>421<br>423<br>426<br>426<br>427                                                                |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                              | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP<br>eQEP<br>Unit Ti<br>eQEP<br>eQEP<br><b>pg-to-D</b>                                                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>416<br>419<br>421<br>423<br>426<br>426<br>426<br>427<br>427<br><b>441</b>                                           |

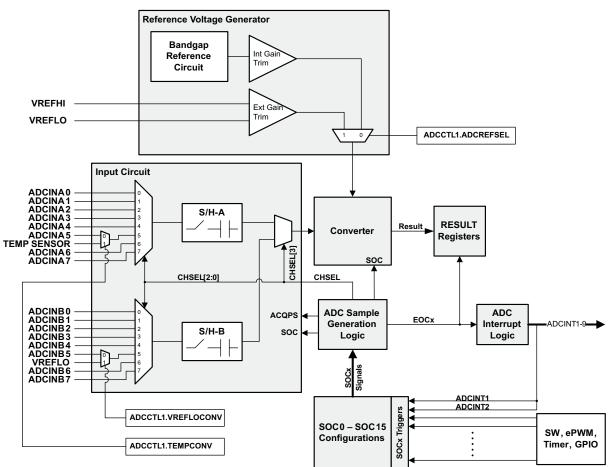

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br><b>Analo</b>              | Introdu<br>Descri<br>5.2.1<br>5.2.2<br>5.2.3<br>Quadr<br>5.3.1<br>5.3.2<br>5.3.3<br>Positic<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>eQEP<br>eQEP<br>Unit Ti<br>eQEP<br>eQEP<br><b>pg-to-D</b>                                                                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 408<br>410<br>411<br>412<br>413<br>413<br>416<br>416<br>416<br>416<br>416<br>416<br>416<br>421<br>421<br>421<br>422<br>426<br>427<br>427<br><b>441</b><br>442<br>442                                    |